# Лекция 2.

# Структура микропроцессорной системы. Основные характеристики микропроцессоров

# Структура микропроцессорной системы

#### Система шин микроЭВМ

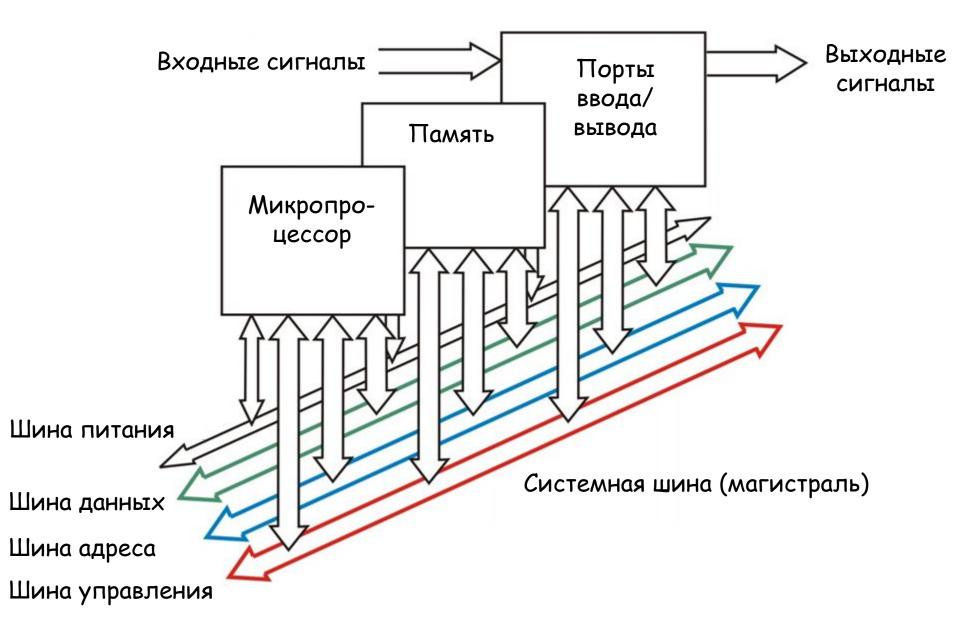

В составе типичной микроЭВМ выделяют три информационных типа шин:

*AB* (*Address Bus*) – шина адреса;

*DB* (*Data Bus*) – шина данных;

CB (Control Bus) – шина управления.

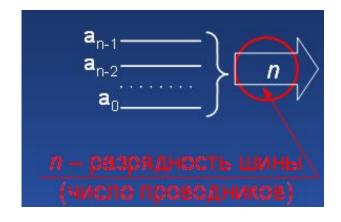

**Шина** — это информационный канал, который объединяет все функциональные блоки МПС и обеспечивает обмен данными в виде двоичных чисел. Конструктивно шина представляет собой п проводников и один общий провод (земля).

Данные по шине передаются в виде слов (байт), которые представляют собой 8 разрядные группы бит.

Различают последовательные и параллельные шины. В параллельной шине информационные биты передаются по отдельным линиям одновременно. Они выполняются в виде плоского кабеля. В последовательной шине информационные биты передаются по одной линии последовательно во времени. Они выполняются в виде коаксиального или оптического кабеля.

#### Назначение шин микроЭВМ

**Шина адреса** служит для определения номера (адреса) устройства, с которым МП обменивается информацией в данный момент. Каждой ячейке памяти в МПС присваивается свой номер (адрес).

**Шина** данных — это основная шина МПС, которая используется для передачи информационных кодов между всеми модулями системы. Обычно в пересылке данных участвует ЦПУ (центральное микропроцессорное устройство), которое передает код данных в какое — либо устройство или ячейку памяти, или же наоборот, принимает код данных из какого — то устройства или ячейки памяти. Но возможен обмен информацией и без участия ЦПУ.

**Шина управления** — в отличии от шин адреса и данных состоит из отдельных управляющий сигналов. Каждый из этих сигналов во время обмена данными имеет свою функцию. Некоторые сигналы служат для определения момента времени, когда информационный код выставляется на шину данных (стробирование). Другие используются для подтверждения приема, сброса устройств в исходное состояние, для синхронизации работы всех устройств.

**Шина питания** не предназначена для передачи данных. Ее функция — подача питания в систему. Она состоит из линий питания и общего провода (земля). В МСП может быть как один, так и несколько источников питания. Каждому напряжению питания соответствует своя линия. Все модули подключаются к этим линиям параллельно.

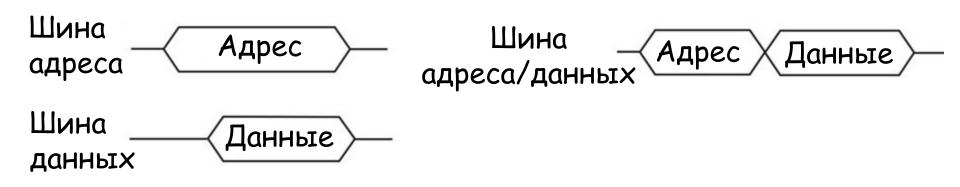

# Мультиплексирование шин адреса и данных

Немультиплексированные шины Мультиплексированная шина

Преимущество мультиплексирования – уменьшение количества линий магистрали;

Недостаток мультиплексирования — снижение скорости обмена по магистрали;

Возможно частичное мультиплексирование (часть данных – по отдельной шине, часть – по шине адреса/данных)

#### Память микроЭВМ

Память микроЭВМ представляет собой совокупность регистров (ячеек), предназначенных для хранения информации в двоичной форме. Каждая ячейка имеет уникальный адрес, что обеспечивает возможность доступа к ней. Адрес представляет собой двоичное слово, длина которого определяет количество ячеек, которое может быть адресовано. Совокупность всех адресов образует адресное пространство микроЭВМ.

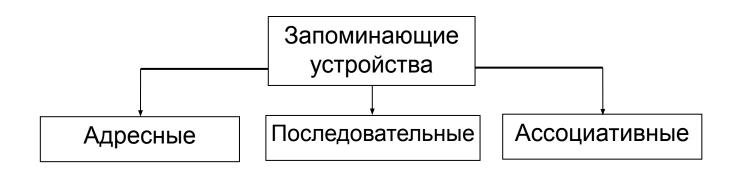

Классификацию запоминающих устройств (ЗУ) произведем по способу доступа к данным.

# Классификация запоминающих устройств

#### Адресные ЗУ

При адресном доступе код на адресном входе указывает ячейку, с которой ведется обмен. Все ячейки адресной памяти в момент обращения равнодоступны. Адресные ЗУ делятся на: *ПЗУ (ROM), ОЗУ (RAM)*.

**Оперативные ЗУ** хранят данные, участвующие в обмене при исполнении текущей программы, которые могут быть изменены в произвольный момент времени. Запоминающие элементы ОЗУ, как правило, не обладают энергонезависимостью.

#### ОЗУ делятся на статические и динамические.

В первом случае запоминающими элементами (3Э) являются триггеры, сохраняющие свое состояние пока схема находится под питанием и нет новой записи данных.

Во втором случае данные хранятся в виде заряда конденсаторов. Саморазряд конденсаторов ведет к разрушению данных, поэтому они должны периодически (через несколько миллисекунд) регенерироваться.

С другой стороны, плотность упаковки динамических элементов памяти в несколько раз превышает плотность упаковки, достижимую в статических ОЗУ поэтому динамические ЗУ характеризуются наибольшей информационной емкостью и невысокой стоимостью. Потому они и нашли более широкое применение (например, в ЭВМ).

**В постоянном ЗУ** содержимое либо вообще не изменяется, либо изменяется, но редко и в специальном режиме. Для рабочего режима это «память только для чтения». ПЗУ программируются при изготовлении методами интегральной технологии.

<u>ПЗУ бывают неперепрограммируемые и репрограммируемые.</u> Последние делятся на:

- РПЗУ УФ (EPROM) репрограммируемое ПЗУ с ультрофиолетовым стиранием;

- РПЗУ ЭС (EEPROM) репрограммируемое ПЗУ с электрическим стиранием.

#### Последовательные ЗУ

В ЗУ с последовательным доступом записываемые данные образуют некоторую очередь. Считывание происходит из очереди слово за словом, либо в порядке записи, либо в обратном порядке.

#### Ассоциативные ЗУ

В таких ЗУ поиск информации реализуется по некоторому признаку, а не по ее расположению в памяти. То есть, все хранимые в памяти слова одновременно проверяются на соответствие признаку, например, на совпадение определенных полей слов (тегов) с признаком, заданным входным словом — теговым адресом. На выход выдаются слова, удовлетворяющие признаку.

#### Особые области памяти МПС

- Память программы начального запуска содержит программу, которая выполняется при включении питания или при подаче сигнала сброса;

- Память для стека или стек используется для временного хранения данных в режиме LIFO (last in, first out). Необходимая при обслуживании прерываний и при работе подпрограмм.

- Память с таблицей векторов прерываний содержит список начальных адресов программ обработки прерываний.

- Память устройств ввода/вывода (УВВ) дает возможность МП общаться с внутренней памятью УВВ как со своей собственной.

#### Порты ввода/вывода

Порты ввода/вывода выполняют роль посредника между микроЭВМ и внешними устройствами. Как и ячейки памяти, порты имеют адрес, что позволяет иметь множество портов в составе одной микроЭВМ. Роль портов могут выполнять микросхемы буферных регистров, микросхема программируемого параллельного интерфейса и др.

#### Структура микропроцессора

В 1970 году фирма Intel сконструировала интегральную схему, аналогичную по своим функциям центральному процессору большой ЭВМ — *первый микропроцессор* Intel-4004, который уже в 1971 году был выпущен в продажу.

#### Микропроцессор включает в себя:

- 1. Арифметико-логическое устройство (АЛУ) служит для осуществления арифметических и логических операций. **Арифметической** операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, умножение);

- **Логической** операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ).

- 2. Регистры общего назначения (РОН), которые используются для хранения информации сверхоперативные запоминающие устройства. Регистры предназначены для хранения операндов в процессе выполнения операций и передачи операндов между регистрами.

#### Структура микропроцессора

- 3. Аккумулятор регистр, из которого берется одно из чисел, с которыми производятся арифметические или логические операции. В него помещается результат.

- **4.** Регистр флагов в него помещаются сведения об особенностях результата выполнения арифметических или логических операций (ноль, переполнение (перенос), четность).

- **5.** Регистр адреса стека, в котором записан адрес последний занятой под стек ячейки памяти.

- **6.** Блок управления шинами МПС схемы, формирующей сигналы на внешних шинах МП для управления МПС.

- 7. Блок дешифрирования кодов команд.

- **8.** Таймер предназначен для подсчета внутренних событий, для получения программно-управляемых временных задержек и для выполнения времязадающих функций МП.

- 9. Счетчик адреса команд, в котором хранится адрес ячейки памяти, в которой записан код текущей команды.

#### Структура микропроцессора

**10.** Память: ОЗУ, ПЗУ, КЭШ.

**КЭШ** память — хранит внутри МП копии тех команд операндов и данных, к которым производились последние обращения МП. Если МП необходимо считать данные, имеющиеся в КЭШ, то она их представляет, и нет необходимости обращаться к внешней памяти. В КЭШ помещаются результаты вычислений.

11. Шины: ША, ШД, ШУ; Шинный интерфейс — выполняет функции согласования действий между внутренними устройствами МП и внешней системой.

#### Основные характеристики микропроцессора

#### МП характеризуется:

1) *тактовой частотой*, определяющей максимальное время выполнения переключения элементов (количество выполняемых операций в секунду);

*Такт* — промежуток времени, между последовательными сигналами синхронизации.

- 2) *разрядностью* максимальным числом одновременно обрабатываемых двоичных разрядов.

- Разрядность МП обозначается m/n/k и включает: m разрядность внутренних регистров, определяет принадлежность к тому или иному классу МП; n разрядность шины данных, определяет скорость передачи информации; k разрядность шины адреса, определяет размер адресного пространства. Например, МП КР580ВМ80 характеризуется значениями m/n/k=16/8/16;

- 3) архитектурой дает представление о функциональном поведении логической структуры и ее организации, определяет особенности построения программных средств.

# Краткая характеристика микропроцессора КР580BM80

Микропроцессор КР580ВМ80 (аналог МП *Intel* 8080) представляет собой 8-разрядное центральное процессорное устройство параллельной обработки данных.

Конструктивно БИС процессора КР580ВМ80 выполнена в корпусе с 40 выводами, из которых 16 приходится на шину адреса, 8 — на шину данных, 4 — на подключение питания, а все остальные — на линии шины управления.

Применяются подобные МП в системах управления различной аппаратурой, где их возможностей хватает для решения поставленных задач.

# Основные параметры МП

| Количество разрядов адреса    | 16                |

|-------------------------------|-------------------|

| Количество разрядов данных    | 8                 |

| Количество выводов для        | 12                |

| управляющих сигналов          |                   |

| Количество исполняемых команд | 78                |

| Тактовая частота              | 2 МГц             |

| Формат команд                 | 1-, 2-, 3-байтные |

|                               | команды           |

| Время выполнения команд       | 29,5 мкс          |

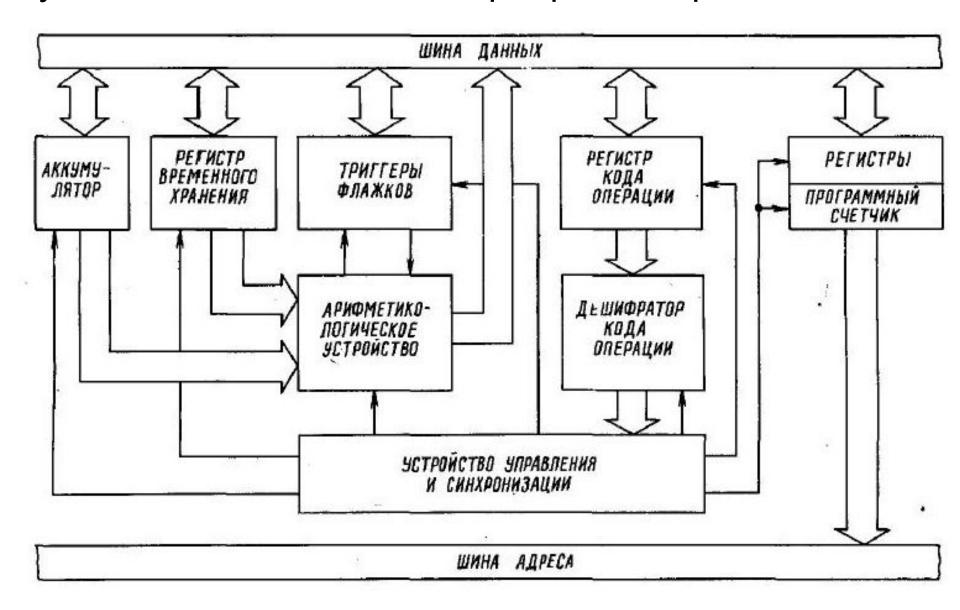

## Функциональная схема микропроцессора КР580ВМ80

## Структура микропроцессора КР580ВМ80

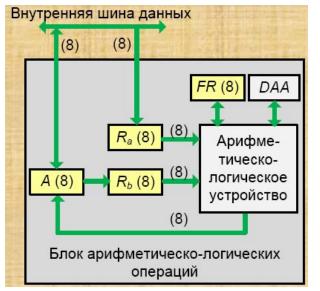

Аккумулятор – главный регистр МП, который соединен шиной данных с арифметико –логическим устройством (АЛУ).

Регистр временного хранения соединен с другим выходом АЛП, этот регистр не доступен программисту и используется для временного хранения данных на выходе АЛП перед их записью в аккумулятор. Он автоматически управляется схемами управления МП.

Регистр кода операции, дешифратор кода операции, программный счетчик, устройство управления и синхронизации, используются для чтения команд из памяти и для их выполнения.

Схемы синхронизации и управления — это процессор внутри процессора. ПЗУ (постоянное запоминающее устройство) внутри МП содержит микрокод (или микропрограмму), который точно указывает процессору, что делать, чтобы выполнить каждую команду. Записанный микрокод, который обычно задается производителем МП, не может изменяться при записи программ, которые выполняются процессором.

Регистр флагов (признаков) микропроцессора KP580BM80

| Биты  | <b>D</b> 7 | D6 | D5 | D4 | D3 | D2 | D1 | D0 |

|-------|------------|----|----|----|----|----|----|----|

| Обозн | S          | Ζ  | 0  | AC | 0  | Р  | 1  | CY |

Проверить состояние флагов можно выполнив проверку содержимого ячейки памяти 83ЕА. Флаги собраны в один байт, показанный на рисунке (значения 0,1 означают, что значение этого бита может быть любым).

| Sign      | Знак результата: "1"— минус; "0"— плюс. Знаком двоичного числа принято считать (как в схемотехнике цифроаналогового преобразования) значение старшего бита этого числа. Поэтому в бит S просто копируется старший бит результата операции, выполняемой процессором. |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Zero      | Нулевой результат: да-"1"; нет-"0".                                                                                                                                                                                                                                 |

| CarrY     | В этот бит помещается перенос из старшего разряда аккумулятора при сложении или из него берётся заём в старший разряд аккумулятора при вычитании: "1"– есть перенос или заём: "1"–нет.                                                                              |

| Add Carry | Дополнительный перенос – то же что и <i>Carry</i> , но для границы полубайтов результата операции (биты D3 и D4).                                                                                                                                                   |

| Parity    | Паритет (чётность) для числа, показывающего количество битов равных "1" в составе байта результата: чётное ( <i>Fven</i> ) –"1": нечётное ( <i>Odd</i> ) – 0                                                                                                        |

в составе байта результата: чётное (Even) –"1"; нечётное (Odd) – 0.