Слайд 2

На этот раз это действительно так: ATI и

NVIDIA поменялись ролями. Если NVIDIA G70 представляет собой не

что иное, как значительно улучшенный NV40 (эволюция), то RADEON X1000 действительно является совершенно новой архитектурой, имеющей мало общего с архитектурами ATI предыдущих поколений (революция).

Более того, старшая модель в семействе, чип RADEON X1800 (R520), получился более сложным, нежели NVIDIA G70 – 320 против 302 миллионов транзисторов! При этом, RADEON X1600 (RV530), нацеленный на средние сегменты рынка состоит из 157 миллионов тразисторов, тогда как RADEON X1300 (RV515) стал, согласно заявлениям разработчиков, первым чипом начального уровня, внутри которого около 100 миллионов транзисторов.

Причинами усложнения архитектуры стал целый набор новведений в чипе, включая такие особенности как:

Поддержка Shader Model 3.0;

Модернизированные шейдерные процессоры со специальным блоком, для выполнения branch инструкций;

Новый контроллер памяти;

Модернизированная система кешей;

Модернизированная система внутренних соединений разных блоков чипа.

Слайд 3

В процессе разработки архитектуры нового поколения, ATI постаралась

сделать ее максимально гибкой, и графический движок был разбит

на отдельные компоненты, число которых можно произвольно компоновать в зависимости от конкретной модели GPU

RADEON X1800 XT graphics card

Слайд 4

Пиксельные процессоры

Поскольку ATI уделила огромное внимание функциям

распределения работы между разными испольнительными устройствами, новая архитектура RADEON

X1000 стала по-настоящему мультипоточной, получив даже специальное название – Ultra-Threaded Architecture. Аналогия с Intel Hyper-Threading здесь вполне уместна, так как цели у этих технологий схожи: как можно более эффективное задействование имеющихся мощностей процессора и максимально возможное сокращение времени простоя исполнительных устройств.

В частности, чипы RADEON X1000 имеют встроенный интеллектуальный коммутатор - специальный блок, называемый Ultra-Threading Dispatch Processor, отвечающий за оптимальное распределение нагрузки между квадами пиксельных процессоров (каждый квад состоит из четырех пиксельных процессоров, каждый из которых в состоянии обработать шейдер для блока 2х2 пиксела за такт), а также текстурными модулями. В частности, Ultra-Threading Dispatch Processor разбивает работу, связанную с одинаковыми пиксельными шейдерами (pixel processing workload) в небольшие группы, или нити (threads) из 4х4 пикселей.

Слайд 5

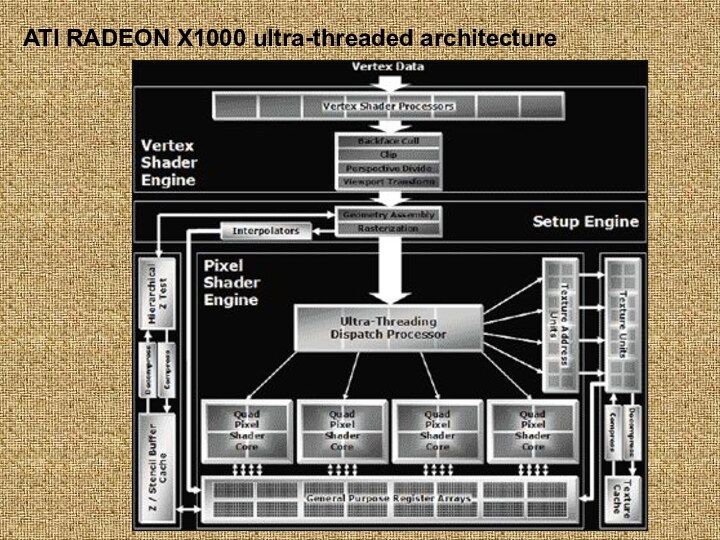

ATI RADEON X1000 ultra-threaded architecture

Слайд 6

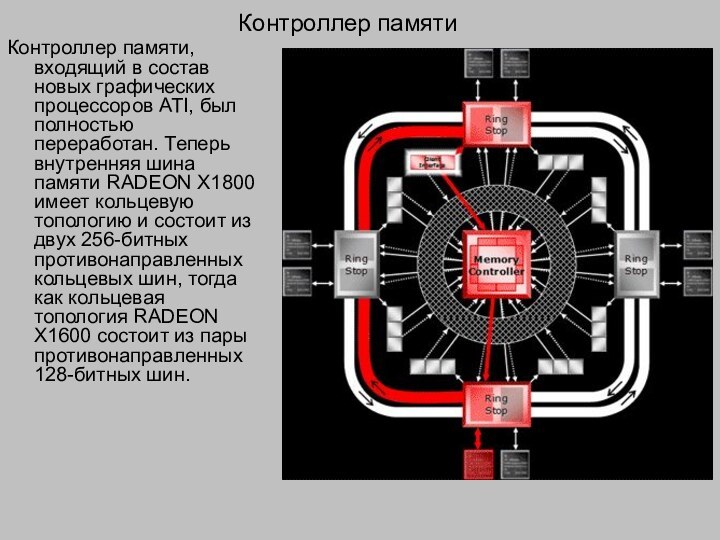

Ultra-Threading Dispatch Processor распознаёт случаи, когда какие-либо пиксельные

процессоры внутри квадов простаивают и моментально назначают им на

выполнение новые задачи. Однако, в случае, когда для продолжения выполнения шейдера требуются еще не полученные данные, то подобная нить приостанавливается арбитражным процессором до их получения, таким образом высвобождая арифметические ресурсы (Arithmetic Logic Unit, ALU) для других нитей и маскируя латентность, к примеру, выборки текстур, находящихся как в кеше, так и в памяти. Согласно ATI, подобная организация работы позволяет достигать 90% эффективности задействования пиксельных процессоров на любых шейдерах.

Поскольку быстрое переключение между нитями требует сохранения промежуточных результатов каждой, ATI использует для этого специальные регистры - General Purpose Register Array - с высокоскоростным соединением с пиксельными процессорами, что мы уже видели в предыдущих графических процессорах. Пока непонятно, какое колиечество регистров имеется в RADEON X1800, X1600 и X1300 и насколько чувствительны новые чипы к сложностям пиксельных шейдеров.

Согласно стандарту Shader Model 3.0, циклы, ветвления и подпрограммы поддерживаются новыми решениями ATI в полной мере, а применение flow control позволяет им исполнять шейдеры практически неограниченной длины. Все вычисления процессоры семейства RADEON X1000 выполняют в формате 128-bit FP, что практически исключает возможность накопления ошибок и, как следствие, ухудшение качества изображения.

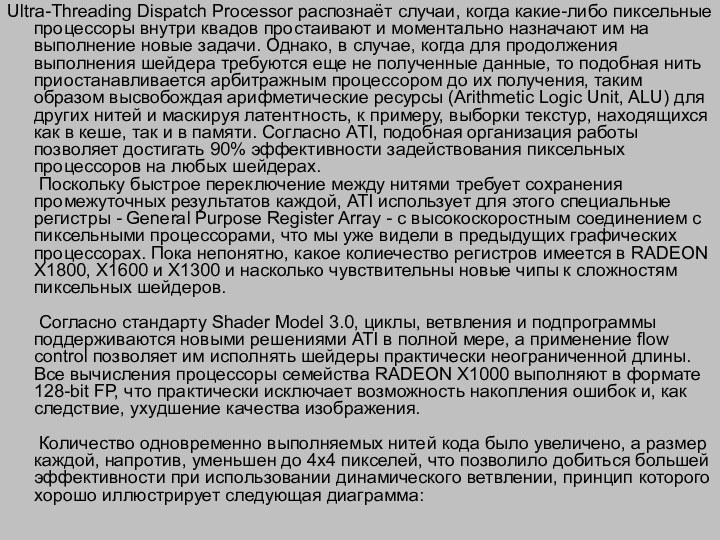

Количество одновременно выполняемых нитей кода было увеличено, а размер каждой, напротив, уменьшен до 4х4 пикселей, что позволило добиться большей эффективности при использовании динамического ветвлении, принцип которого хорошо иллюстрирует следующая диаграмма:

Слайд 8

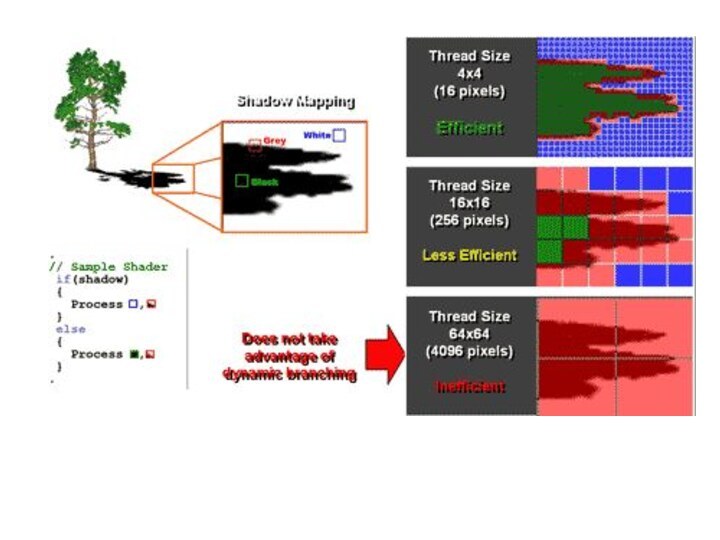

Контроллер памяти

Контроллер памяти, входящий в состав новых

графических процессоров ATI, был полностью переработан. Теперь внутренняя шина

памяти RADEON X1800 имеет кольцевую топологию и состоит из двух 256-битных противонаправленных кольцевых шин, тогда как кольцевая топология RADEON X1600 состоит из пары противонаправленных 128-битных шин.

Слайд 9

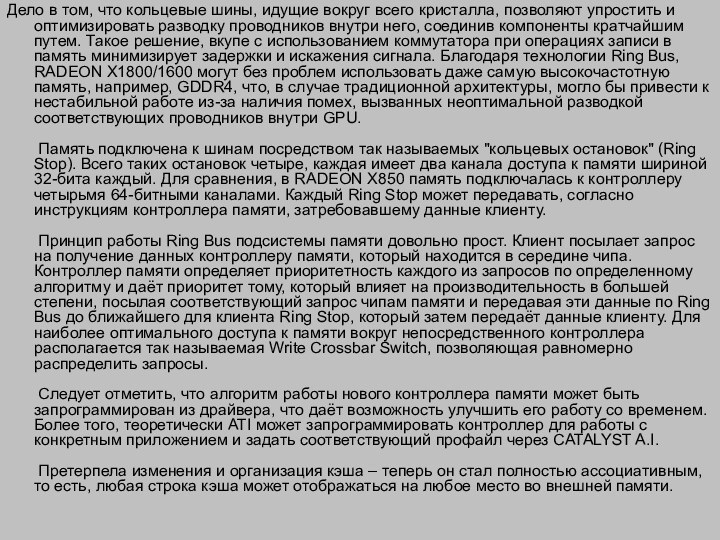

Дело в том, что кольцевые шины, идущие вокруг

всего кристалла, позволяют упростить и оптимизировать разводку проводников внутри

него, соединив компоненты кратчайшим путем. Такое решение, вкупе с использованием коммутатора при операциях записи в память минимизирует задержки и искажения сигнала. Благодаря технологии Ring Bus, RADEON X1800/1600 могут без проблем использовать даже самую высокочастотную память, например, GDDR4, что, в случае традиционной архитектуры, могло бы привести к нестабильной работе из-за наличия помех, вызванных неоптимальной разводкой соответствующих проводников внутри GPU.

Память подключена к шинам посредством так называемых "кольцевых остановок" (Ring Stop). Всего таких остановок четыре, каждая имеет два канала доступа к памяти шириной 32-бита каждый. Для сравнения, в RADEON X850 память подключалась к контроллеру четырьмя 64-битными каналами. Каждый Ring Stop может передавать, согласно инструкциям контроллера памяти, затребовавшему данные клиенту.

Принцип работы Ring Bus подсистемы памяти довольно прост. Клиент посылает запрос на получение данных контроллеру памяти, который находится в середине чипа. Контроллер памяти определяет приоритетность каждого из запросов по определенному алгоритму и даёт приоритет тому, который влияет на производительность в большей степени, посылая соответствующий запрос чипам памяти и передавая эти данные по Ring Bus до ближайшего для клиента Ring Stop, который затем передаёт данные клиенту. Для наиболее оптимального доступа к памяти вокруг непосредственного контроллера располагается так называемая Write Crossbar Switch, позволяющая равномерно распределить запросы.

Следует отметить, что алгоритм работы нового контроллера памяти может быть запрограммирован из драйвера, что даёт возможность улучшить его работу со временем. Более того, теоретически ATI может запрограммировать контроллер для работы с конкретным приложением и задать соответствующий профайл через CATALYST A.I.

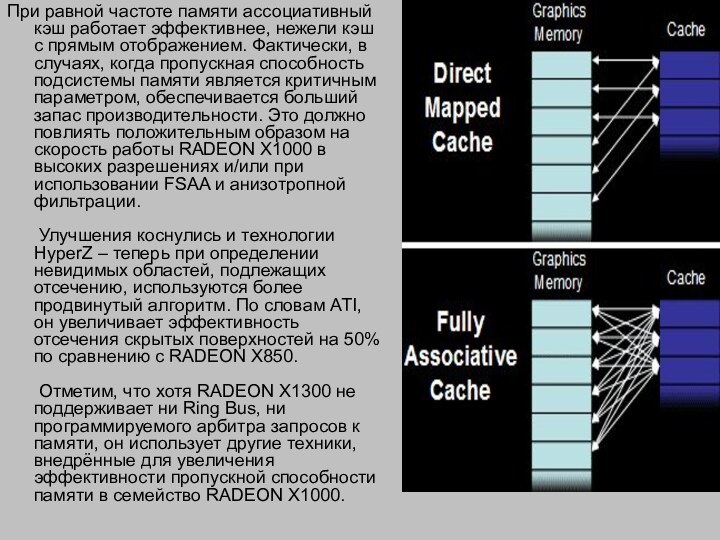

Претерпела изменения и организация кэша – теперь он стал полностью ассоциативным, то есть, любая строка кэша может отображаться на любое место во внешней памяти.

Слайд 10

При равной частоте памяти ассоциативный кэш работает эффективнее,

нежели кэш с прямым отображением. Фактически, в случаях, когда

пропускная способность подсистемы памяти является критичным параметром, обеспечивается больший запас производительности. Это должно повлиять положительным образом на скорость работы RADEON X1000 в высоких разрешениях и/или при использовании FSAA и анизотропной фильтрации.

Улучшения коснулись и технологии HyperZ – теперь при определении невидимых областей, подлежащих отсечению, используются более продвинутый алгоритм. По словам ATI, он увеличивает эффективность отсечения скрытых поверхностей на 50% по сравнению с RADEON X850.

Отметим, что хотя RADEON X1300 не поддерживает ни Ring Bus, ни программируемого арбитра запросов к памяти, он использует другие техники, внедрённые для увеличения эффективности пропускной способности памяти в семейство RADEON X1000.