- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Флэш-память

Содержание

- 2. Флеш-память Флеш-память (англ. flash memory) —

- 3. PROM PROM (англ. Programmable Read-Only Memory)

- 4. EPROM EPROM (англ. Erasable Programmable Read

- 5. EEPROM EEPROM (англ. Electrically Erasable Programmable

- 6. NOR и NAND Различаются методом соединения

- 7. NOR Конструкция NOR использует классическую двумерную

- 8. NANDКонструкция NAND — трехмерный массив. В основе

- 9. NOR и NAND Технология NOR позволяет

- 10. Флэш-памятьс несимметричной блочной структурой

- 11. Boot Block Flesh Memory (ББФП)

- 12. Блоки параметров и главные блоки В

- 13. Расположения ББМикросхемы ББФП предназначены для работы с

- 14. АдресаАдреса задаются 19-разрядным кодом ,т.е в памяти

- 15. Напряжение на выводе RP Напряжение на

- 16. Экономии мощностиИмея ряд режимов экономии мощности, схемы

- 17. Список используемой литературыhttp://www.allbest.ru/http://ru.wikipedia.orghttp://www.ammt.ruhttp://www.zadachi.org.ruhttp://referat.resurs.kz

- 18. Скачать презентацию

- 19. Похожие презентации

Флеш-память Флеш-память (англ. flash memory) — разновидность полупроводниковой технологии электрически перепрограммируемой памяти (EEPROM). Это же слово используется в электронной схемотехнике для обозначения технологически законченных решений постоянных запоминающих устройств в виде микросхем на базе этой полупроводниковой

Слайд 3

PROM

PROM (англ. Programmable Read-Only Memory) —

класс полупроводниковых запоминающих устройств, постоянная память с пережигаемыми перемычками.

Память представляла собой двумерный массив проводников (строк и столбцов) на пересечении которых создавалась специальная перемычка из металла (например, нихрома или титаново-вольфрамового сплава) или аморфного кремния. Программирование заключалось в пропускании через соответствующую перемычку тока, который заставлял её разорваться — расплавиться и испариться. Восстановление расплавленных перемычек невозможно.

Слайд 4

EPROM

EPROM (англ. Erasable Programmable Read Only

Memory) — класс полупроводниковых запоминающих устройств, постоянная память, для

записи информации (программирования) в которую используется электронное устройство-программатор и которое допускает перезапись.Представляет собой матрицу транзисторов с плавающим затвором индивидуально запрограммированных с помощью электронного устройства, которое подаёт более высокое напряжение, чем обычно используеся в цифровых схемах. В отличие от PROM, после программирования данные на EPROM можно стереть (сильным ультрафиолетовым светом от ртутного источника света).

Слайд 5

EEPROM

EEPROM (англ. Electrically Erasable Programmable Read-Only

Memory) — электрически стираемое перепрограммируемое ПЗУ (ЭСППЗУ), один из

видов энергонезависимой памяти (таких как PROM и EPROM). Память такого типа может стираться и заполняться данными до миллиона раз.Эта конструкция снабжается элементами которые позволяют ей работать в большом массиве таких же ячеек. Соединение выполняется в виде двумерной матрицы, в которой на пересечении столбцов и строк находится одна ячейка. Поскольку ячейка EEPROM имеет третий затвор то помимо подложки к каждой ячейке подходят 3 проводника (один проводник столбцов и 2 проводника строк).

Слайд 6

NOR и NAND

Различаются методом соединения ячеек

в массив и алгоритмами чтения-записи.

Компоновка шести ячеек NOR flash

Структура

одного столбца NAND flash

Слайд 7

NOR

Конструкция NOR использует классическую двумерную матрицу

проводников («строки» и «столбцы») в которой на пересечении установлено

по одной ячейке. При этом проводник строк подключался к стоку транзистора, а столбцов к второму затвору. Исток подключался к общей для всех подложке. В такой конструкции было легко считать состояние конкретного транзистора подав положительное напряжение на один столбец и одну строку.

Слайд 8

NAND

Конструкция NAND — трехмерный массив. В основе та

же самая матрица что и NOR, но вместо одного

транзистора в каждом пересечении устанавливается столбец из последовательно включенных ячеек. В такой конструкции затворных цепей в одном пересечении получается много. Плотность компоновки можно резко увеличить (ведь к одной ячейке в столбце подходит только один проводник затвора), однако алгоритм доступа к ячейкам для чтения и записи заметно усложняется.

Слайд 9

NOR и NAND

Технология NOR позволяет получить

быстрый доступ индивидуально к каждой ячейке, однако площадь ячейки

велика. Наоборот, NAND имеют малую площадь ячейки, но относительно длительный доступ сразу к большой группе ячеек. Соответственно различается область применения: NOR используется как непосредственная память программ микропроцессоров и для хранения небольших вспомогательных данных. Топовые значения объемов микросхем NOR — 64 МБайт. NAND имеет топовые значения объема на микросхему в единицы гигабайт.На сегодняшний день классическая двухтранзисторная технология EEPROM практически полностью вытеснена NOR флеш-памятью. Однако название EEPROM прочно закрепилось за сегментом памяти малой емкости независимо от технологии.

Слайд 11

Boot Block Flesh Memory (ББФП)

Схемам

типа Boot Block Flesh Memory(сокращенно ББФП)присуще блочное стирание данных

и несиммметричная блочная структура. Блоки специализированы и имеют разные размеры. Среди них имеется так называемый Boot-блок(ББ),содержимое которого аппаратно защищено от случайного стирания. В ББ хранится программное обеспечение базовой системы ввода/вывода микропроцессорной системы BIOS, необходимое для правильной эксплуатации и инициализации системы.

Слайд 12

Блоки параметров и главные блоки

В составе

блоков имеется БП(блоки параметров) и ГБ(главные блоки),не снабженные аппаратными

средствами защиты от непредусмотренной записи. Блоки БП хранят относительно часто меняемые параметры системы(коды идентификаторов, диагностические программы и т.п).Блоки ГБ хранят основные управляющие программы.

Слайд 13

Расположения ББ

Микросхемы ББФП предназначены для работы с разными

микропроцессорами и для соответствия им имеют 2 варианта расположения

ББ в адресном пространстве: вверху и внизу, что отображается в маркировке ИС буквами Т(ТОР) или В (Воtооm).В настоящее время выпускаются ББФП с емкостями 1...16 мбит ,в последующих поколениях ожидаются ИС с информационными емкостями до 256 мбит.

Слайд 14

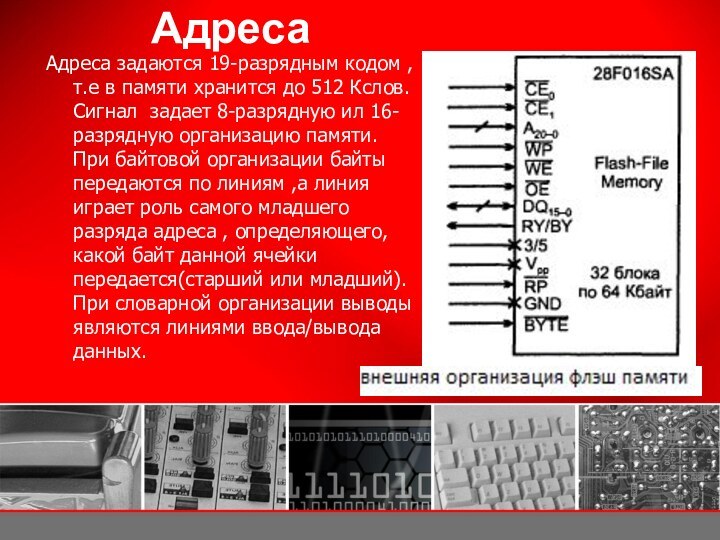

Адреса

Адреса задаются 19-разрядным кодом ,т.е в памяти хранится

до 512 Кслов. Сигнал задает 8-разрядную ил 16-разрядную организацию

памяти. При байтовой организации байты передаются по линиям ,а линия играет роль самого младшего разряда адреса , определяющего, какой байт данной ячейки передается(старший или младший).При словарной организации выводы являются линиями ввода/вывода данных.

Слайд 15

Напряжение на выводе RP

Напряжение на выводе

RP (Reset/Power Down) может иметь три уровня:

12

В ±5% ,уровень логической единицы H и низкий уровень L.При напряжении 12 В ±5% ББ открыт и в нем могут выполняться операции стирания и программирования. При напряжении ниже 6,5 В ББ заперт.

Слайд 16

Экономии мощности

Имея ряд режимов экономии мощности, схемы ББФП,

в частности, реализуют режим APS (Automatic Power Saving) ,благодаря

которому после завершения цикла чтения схема автоматически входит в статический режим с потреблением тока около 1 мА,в котором находится до начала следующего цикла чтения.Когда схема не выбрана(при высоком уровне сигнала на выводе СЕ и выводе ,т.е потребление мощности снижается до уровня покоя(10мкА).При не только запрещается запись, но и вводится режим глубокого снижения мощности, в котором ток потребления снижается до долей мкА.