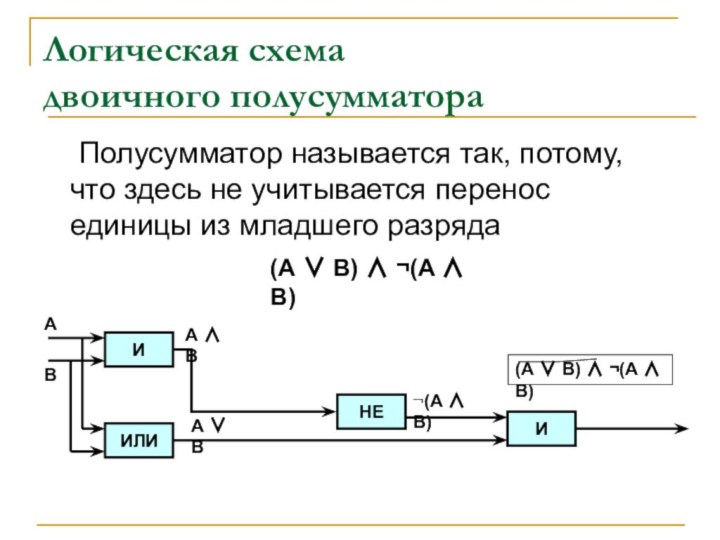

при помощи т.н. базовых логических элементов, которые также еще

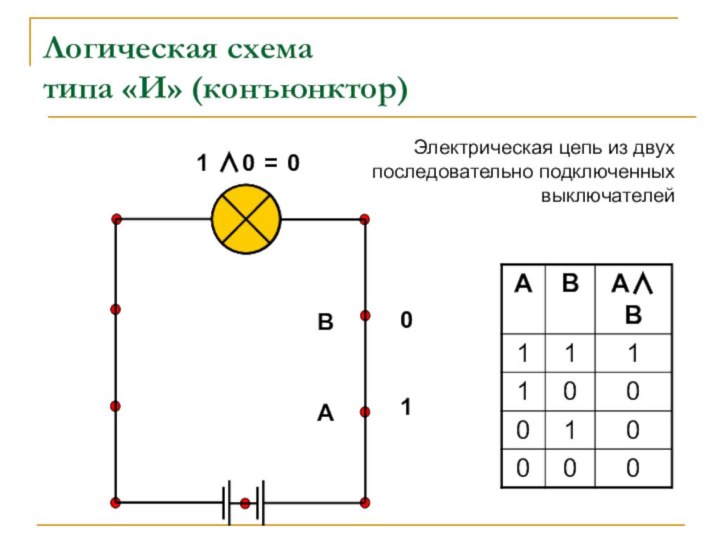

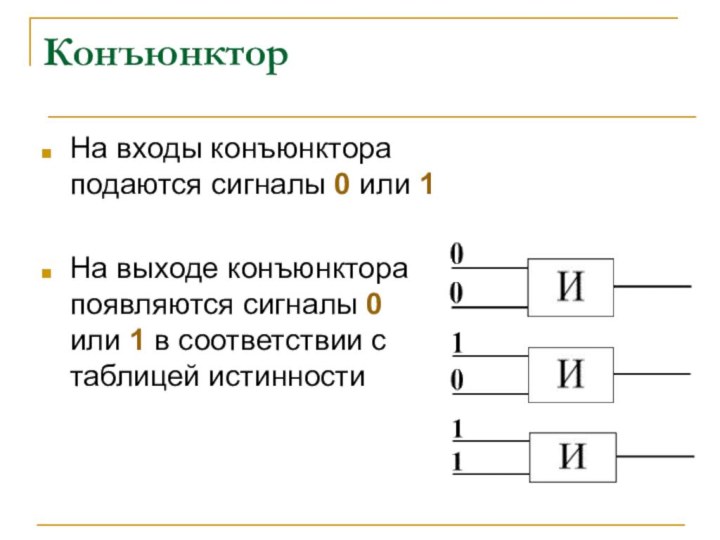

называют вентилями.Вентиль «И» – конъюнктор. Реализует конъюнкцию.

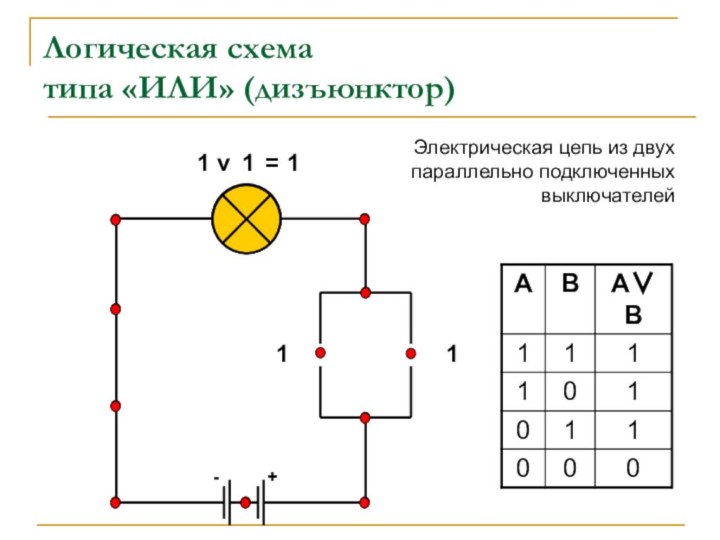

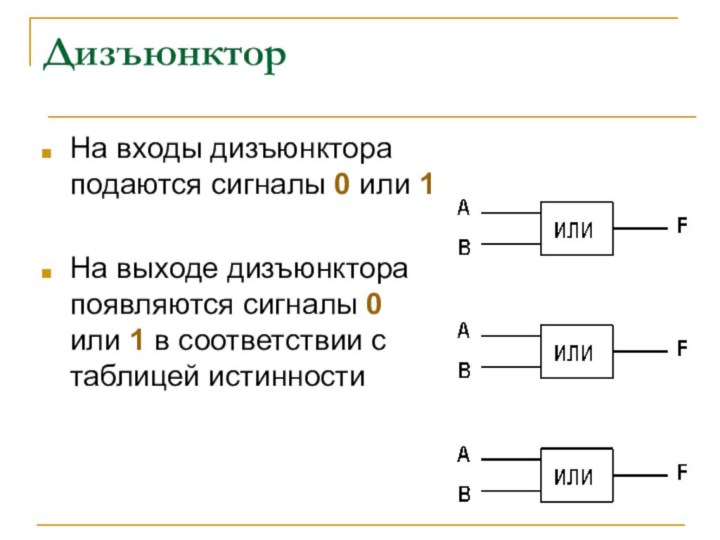

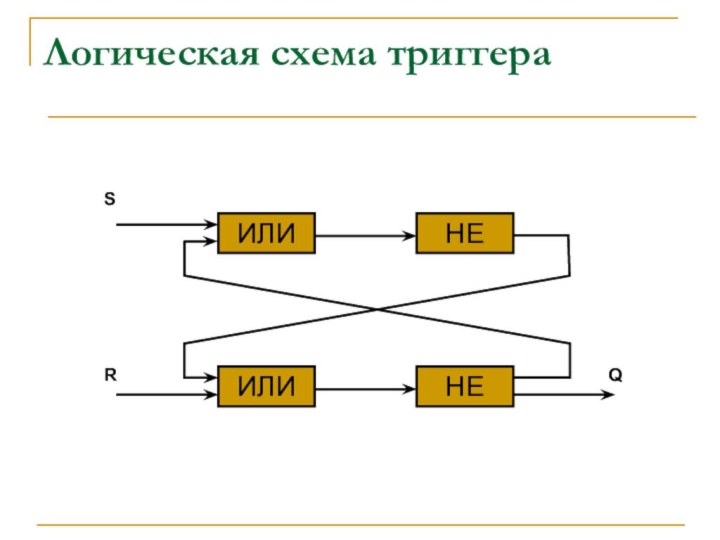

Вентиль «ИЛИ» – дизъюнктор. Реализует дизъюнкцию.

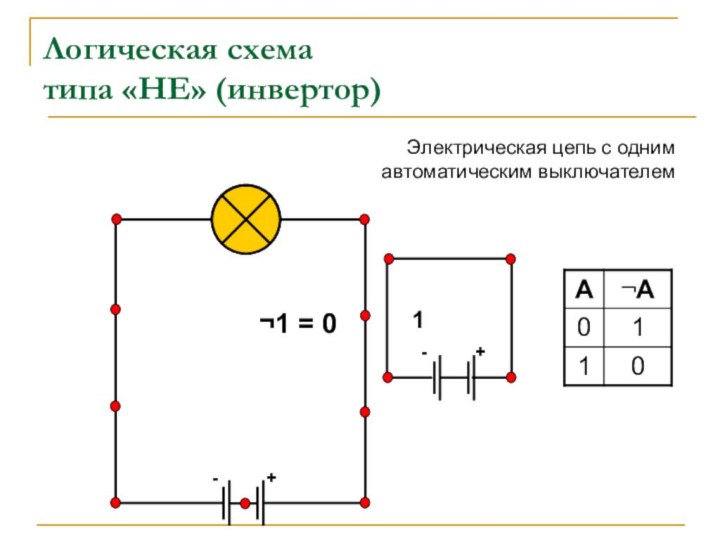

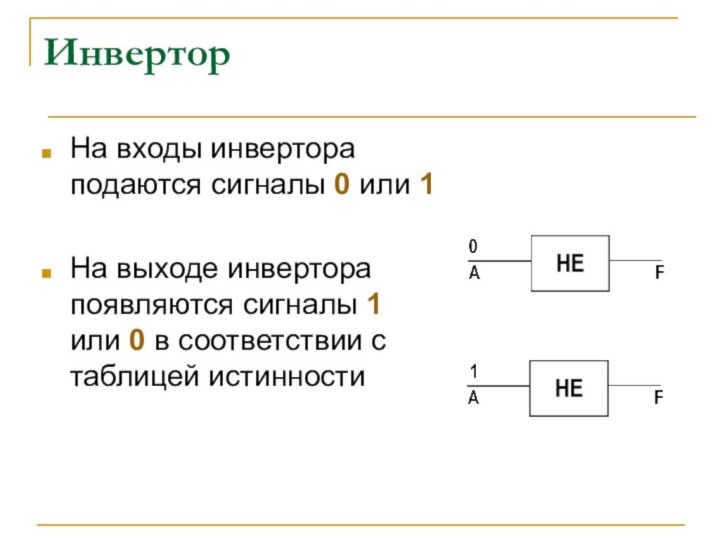

Вентиль «НЕ» – инвертор. Реализует инверсию

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Email: Нажмите что бы посмотреть

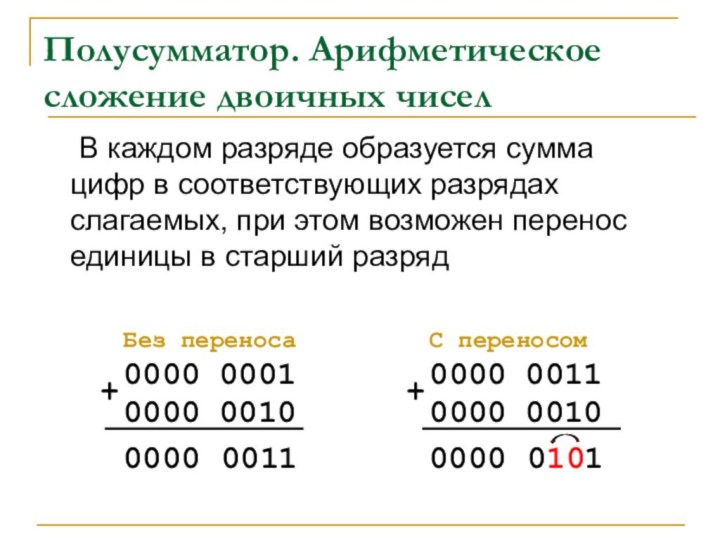

Без переноса

0000 0001

0000 0010

0

0

0

0

0

0

1

1

С переносом

0000 0011

0000 0010

0

0

0

0

0

1

0

1

+

+

0

0

0

1

0

1

1

0

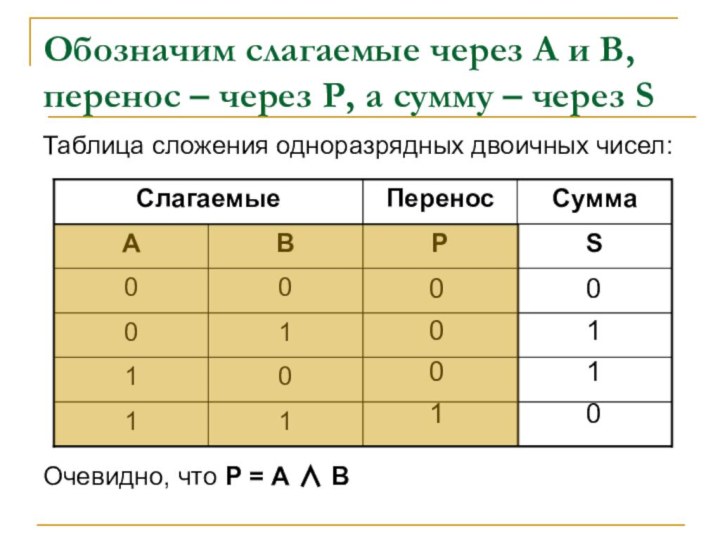

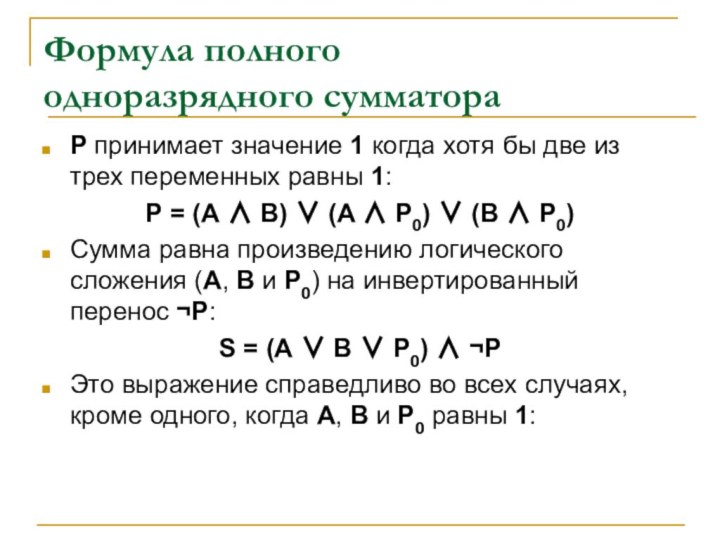

Очевидно, что Р = А ∧ В

0

1

1

1

0

0

0

1

1

1

1

0

0

1

1

0

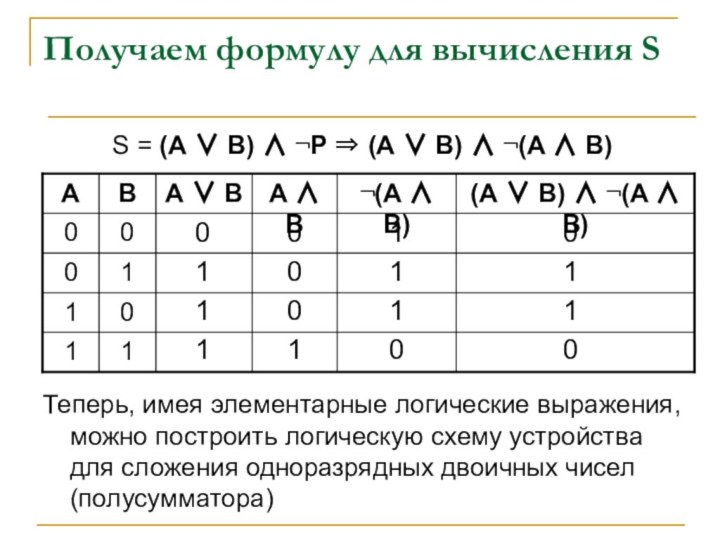

Теперь, имея элементарные логические выражения, можно построить логическую схему устройства для сложения одноразрядных двоичных чисел (полусумматора)

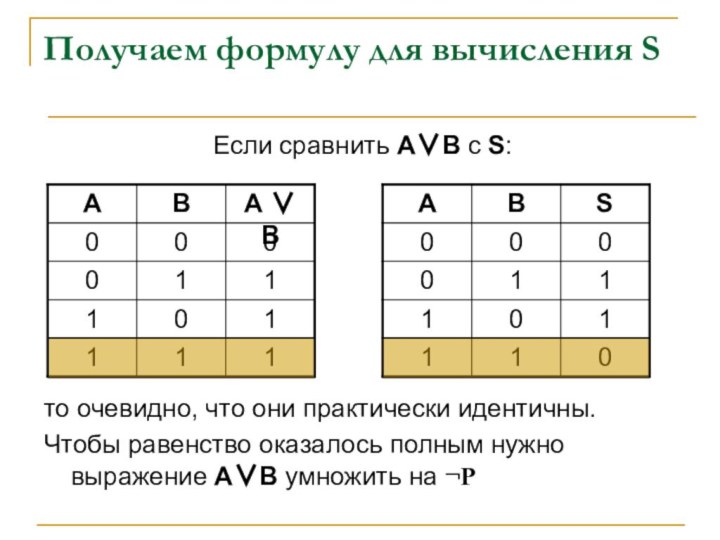

А ∨ В

¬(А ∧ В)

(А ∨ В) ∧ ¬(A ∧ B)

(А ∨ В) ∧ ¬(A ∧ B)