- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

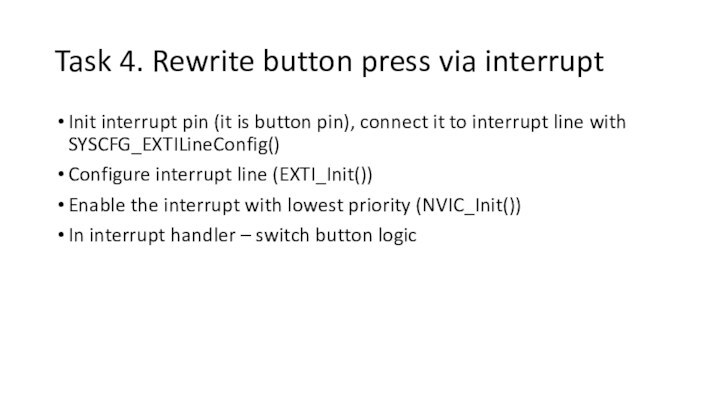

Презентация на тему Task 4. timersandinterrupts

Содержание

- 2. Linksstm32_reference_manual.pdf - Part 12, Interrupts and events, Part 18, General-purpose timers https://habrahabr.ru/post/218825/http://visualgdb.com/tutorials/arm/stm32/timers/

- 3. Nested vectored interrupt controller (NVIC)82 maskable interrupt

- 4. Hardware interrupt selectionTo configure the 23 lines

- 5. General-purpose timers (TIM2 to TIM5)• 16-bit (TIM3

- 6. Task 4. Rewrite main cycle via timerInit

- 7. Скачать презентацию

- 8. Похожие презентации

Linksstm32_reference_manual.pdf - Part 12, Interrupts and events, Part 18, General-purpose timers https://habrahabr.ru/post/218825/http://visualgdb.com/tutorials/arm/stm32/timers/

Слайд 2

Links

stm32_reference_manual.pdf - Part 12, Interrupts and events, Part

18, General-purpose timers

Слайд 3

Nested vectored interrupt controller (NVIC)

82 maskable interrupt channels

for STM32F405xx/07xx and STM32F415xx/17xx, and up to 91 maskable

interrupt channels for STM32F42xxx and STM32F43xxx (not including the 16 interrupt lines of Cortex®-M4 with FPU)16 programmable priority levels (4 bits of interrupt priority are used)

low-latency exception and interrupt handling

power management control

implementation of system control registers