Слайд 2

Микроконтроллер 8051

Микроконтроллер выполнен на основе высокоуровневой

n-МОП технологии. Через четыре программируемых параллельных порта ввода/вывода и

один последовательный порт микроконтроллер взаимодействует с внешними устройствами. Основу структурной схемы (рис. 1) образует внутренняя двунаправленная 8-битная шина, которая связывает между собой основные узлы и устройства микроконтроллера: резидентную память программ (RPM), резидентную память данных (RDM), арифметико-логическое устройство (ALU), блок регистров специальных функций, устройство управления (CU) и порты

ввода/вывода (P0-P3).

Слайд 3

Микроконтроллеры рассматриваемого семейства являются типичными микропроцессорными

устройствами с архитектурой SISC - со стандартным набором команд.

Поэтому их система команд довольно обширна и включает в себя 111 основных команд. Их длина - один, два или три байта, причем большинство из них (94%) - одно- или двухбайтные. Все команды выполняются за один или два машинных цикла (соответственно 1 или 2 мкс при тактовой частоте 12 МГц), исключение - команды умножения и деления, которые выполняются за четыре машинных цикла (4 мкс). Микроконтроллеры семейства 8051 используют прямую, непосредственную, косвенную и неявную, адресацию данных.

В качестве операндов команд микроконтроллеры семейства 8051 могут использовать отдельные биты, четырехбитные цифры, байты и двухбайтные слова.

Все эти черты обычны для набора команд любого SISC-процессора и по сранению с RISC набором команд обеспечивает большую компактность программного кода и увеличение быстродействия при выполнении сложных операций.

В то же время, набор команд семейства 8051 имеет несколько особенностей, связанных с типичными функциями выполняемыми микроконтроллерами - управлением, для которого типичным является оперирование с одноразрядными двоическими сигналами, большое число операций ввода выводи и ветвлений программы.

Слайд 4

Наиболее существенная особенность системы команд рассматриваемых

микроконтроллеров это возможность адресации отдельных бит в резидентной памяти

данных. Кроме того, как отмечалось, некоторые регистры блока регистров специальных функций также допускают адресацию отдельных бит.

Арифметико-логическое устройство.

8-битное арифметико-логическое устройство (ALU) может выполнять арифметические операции сложения, вычитания, умножения и деления; логические операции И, ИЛИ, исключающее ИЛИ, а также операции циклического сдвига, сброса, инвертирования и т.п. К входам подключены программно-недоступные регистры T1 и T2, предназначенные для временного хранения операндов, схема десятичной коррекции (DCU) и схема формирования признаков результата операции (PSW).

Простейшая операция сложения используется в ALU для инкрементирования содержимого регистров, продвижения регистра-указателя данных (RAR) и автоматического вычисления следующего адреса резидентной памяти программ. Простейшая операция вычитания используется в ALU для декрементирования регистров и сравнения переменных.

Слайд 5

Простейшие операции автоматически образуют “тандемы” для

выполнения таких операций, как, например, инкрементирование 16-битных регистровых пар.

В ALU реализуется механизм каскадного выполнения простейших операций для реализации сложных команд. Так, например, при выполнении одной из команд условной передачи управления по результату сравнения в ALU трижды инкрементируется счётчик команд (PC), дважды производится чтение из RDM, выполняется арифметическое сравнение двух переменных, формируется 16-битный адрес перехода и принимается решение о том, делать или не делать переход по программе. Все перечисленные операции выполняются всего лишь за 2 мкс.

Важной особенностью ALU является его способность оперировать не только байтами, но и битами. Отдельные программно-доступные биты могут быть установлены, сброшены, инвертированы, переданы, проверены и использованы в логических операциях. Эта способность достаточно важна, поскольку для управления объектами часто применяются алгоритмы, содержащие операции над входными и выходными булевыми переменными, реализация которых средствами обычных микропроцессоров сопряжена с определенными трудностями.

Ниже прииведена структурная схема микроконтроллера КМ1816ВЕ51.

Слайд 7

Таким образом, ALU может оперировать

четырьмя типами информационных объектов: булевыми (1 бит), цифровыми (4

бита), байтными (8 бит) и адресными (16 бит). В ALU выполняется 51 различная операция пересылки или преобразования этих данных. Так как используется 11 режимов адресации (7 для данных и 4 для адресов), то путем комбинирования операции и режима адресации базовое число команд 111 расширяется до 255 из 256 возможных при однобайтном коде операции.

Резидентная память программ и данных.

Резидентные (размещённые на кристалле) память программ (RPM) и память данных (RDM) физически и логически разделены, имеют различные механизмы адресации, работают под управлением различных сигналов и выполняют разные функции

Память программ RPM имеет емкость 4 Кбайта и предназначена для хранения команд, констант, управляющих слов инициализации, таблиц перекодировки входных и выходных переменных и т.п. Память имеет 16-битную шину адреса, через которую обеспечивается доступ из программного счётчика PC или из регистра- указателя данных (DPTR).

Слайд 8

DPTR выполняет функции базового регистра при косвенных переходах

по программе или используется в операциях с таблицами. Память

данных RDM предназначена для хранения переменных в процессе выполнения прикладной программы, адресуется одним байтом и имеет емкость 128 байт. Кроме того, к её адресному пространству примыкают адреса регистров специальных функций, которые перечислены в табл. 1.

Память программ, так же как и память данных, может быть расширена до 64 Кбайт путем подключения внешних микросхем.

Слайд 9

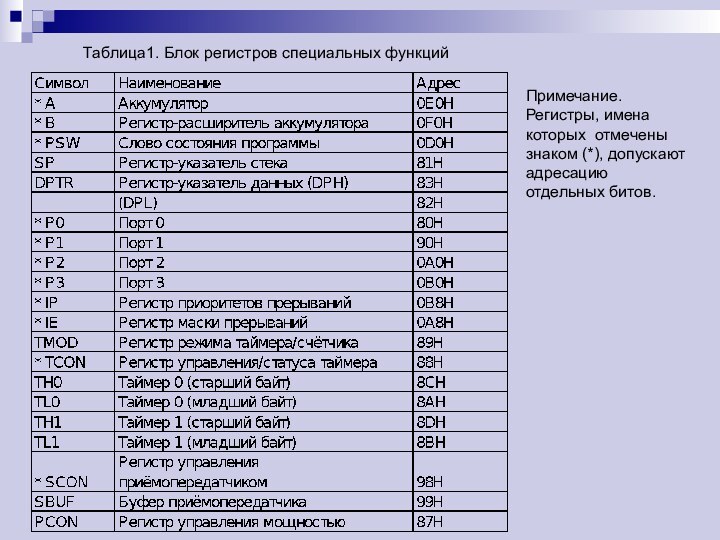

Таблица1. Блок регистров специальных функций

Примечание.

Регистры, имена

которых отмечены

знаком (*), допускают

адресацию

отдельных битов.

Слайд 10

Аккумулятор, регистры общего назначения и флаги.

Аккумулятор (A)

является источником операнда и местом фиксации результата при выполнении

арифметических, логических операций и ряда операций передачи данных. Кроме того, только с использованием аккумулятора могут быть выполнены операции сдвигов, проверка на нуль, формирование флага паритета и т.п. В распоряжении пользователя имеются 8 регистров общего назначения R0–R7 одного из четырёх возможных банков. При выполнении многих команд в ALU формируется ряд признаков операции (флагов), которые фиксируются в регистре PSW. В табл. 2 приводится перечень флагов PSW, даются их символические имена и описываются условия их формирования.

Слайд 11

Таблица 2. Формат слова состояния программы - PSW.

Слайд 12

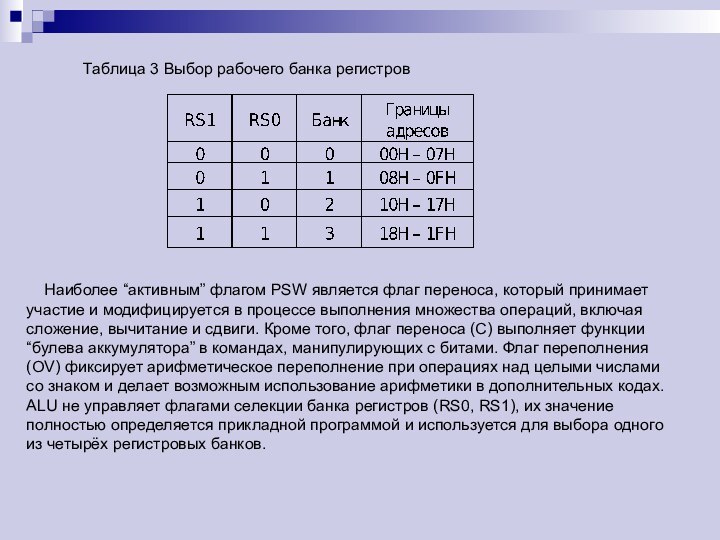

Таблица 3 Выбор рабочего банка регистров

Наиболее “активным” флагом PSW является флаг переноса, который принимает

участие и модифицируется в процессе выполнения множества операций, включая сложение, вычитание и сдвиги. Кроме того, флаг переноса (C) выполняет функции “булева аккумулятора” в командах, манипулирующих с битами. Флаг переполнения (OV) фиксирует арифметическое переполнение при операциях над целыми числами со знаком и делает возможным использование арифметики в дополнительных кодах. ALU не управляет флагами селекции банка регистров (RS0, RS1), их значение полностью определяется прикладной программой и используется для выбора одного из четырёх регистровых банков.

Слайд 13

В микропроцессорах, архитектура которых опирается на аккумулятор, большинство

команд работают с ним, используя неявную адресацию. В Intel

8051 дело обстоит иначе. Хотя процессор имеет в своей основе аккумулятор, он может выполнять множество команд и без его участия. Например, данные могут быть пере- даны из любой ячейки RDM в любой регистр, любой регистр может быть загружен непосредственным операндом и т.д. Многие логические операции могут быть выполнены без участия аккумулятора. Кроме того, переменные могут быть инкрементированы, декрементированы и проверены без использования аккумулятора. Флаги и управляющие биты могут быть проверены и изменены аналогично.

Регистры-указатели.

8-битный указатель стека (SP) может адресовать любую область RDM. Его содержимое инкрементируется прежде, чем данные будут запомнены в стеке в ходе выполнения команд PUSH и CALL. Содержимое SP декрементируется после выполнения команд POP и RET. Подобный способ адресации элементов стека называют прединкрементным/постдекрементным. В процессе инициализации микроконтроллера после сигнала RST в SP автоматически загружается код 07Н. Это значит, что если прикладная программа не переопределяет стек, то первый элемент данных в стеке будет располагаться в ячейке RDM с адресом 08Н. Двухбайтный регистр-указатель данных DPTR обычно используется для фиксации 16-битного адреса в операциях с обращением к внешней памяти. Командами микроконтроллера регистр-указатель данных может быть использован или как 16-битный регистр, или как два независимых 8-битных регистра (DPH и DPL).

Слайд 14

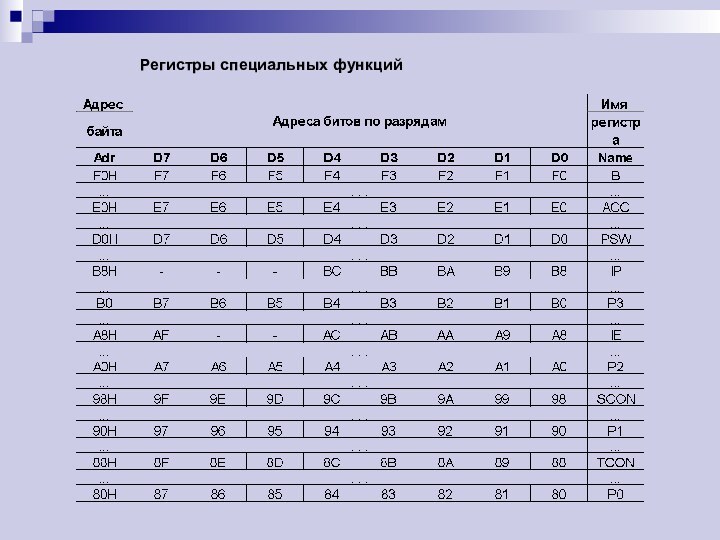

Регистры специальных функций.

Регистры с символическими именами IP, IE,

TMOD, TCON, SCON и PCON используются для фиксации и

программного изменения управляющих бит и бит состояния схемы прерывания, таймера/счётчика, приёмопередатчика последовательного порта и для управления энергопотреблением. Их организация будет описана ниже при рассмотрении особенностей работы микроконтроллера в различных режимах.

Устройство управления и синхронизации

Кварцевый резонатор, подключаемый к внешним выводам микроконтроллера, управляет работой внутреннего генератора, который в свою очередь формирует сигналы синхронизации. Устройство управления (CU) на основе сигналов синхронизации формирует машинный цикл фиксированной длительности, равной 12 периодам резонатора. Большинство команд микроконтроллера выполняется за один машинный цикл. Некоторые команды, оперирующие с 2-байтными словами или связанные с обращением к внешней памяти, выполняются за два машинных цикла. Только команды деления и умножения требуют четырех машинных циклов. На ос нове этих особенностей работы устройства управления производится расчёт времени исполнения прикладных программ.

На схеме микроконтроллера к устройству управления примыкает регистр команд (IR). В его функцию входит хранение кода выполняемой команды.

Слайд 15

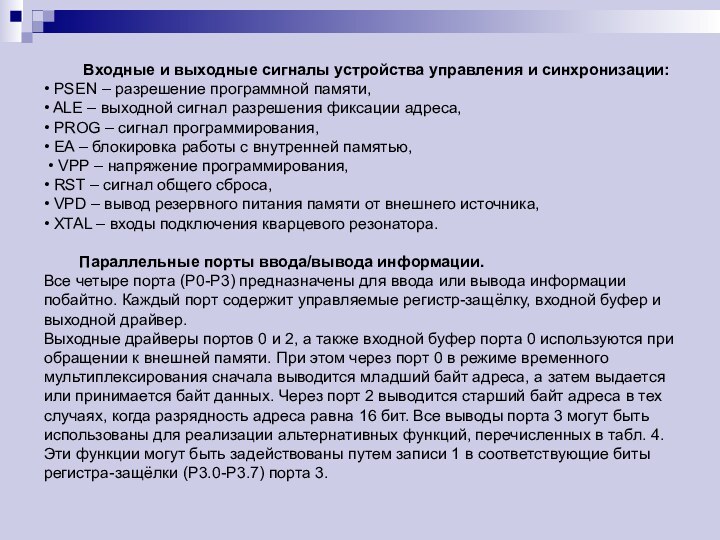

Входные и выходные

сигналы устройства управления и синхронизации:

• PSEN – разрешение

программной памяти,

• ALE – выходной сигнал разрешения фиксации адреса,

• PROG – сигнал программирования,

• EA – блокировка работы с внутренней памятью,

• VPP – напряжение программирования,

• RST – сигнал общего сброса,

• VPD – вывод резервного питания памяти от внешнего источника,

• XTAL – входы подключения кварцевого резонатора.

Параллельные порты ввода/вывода информации.

Все четыре порта (P0-P3) предназначены для ввода или вывода информации побайтно. Каждый порт содержит управляемые регистр-защёлку, входной буфер и выходной драйвер.

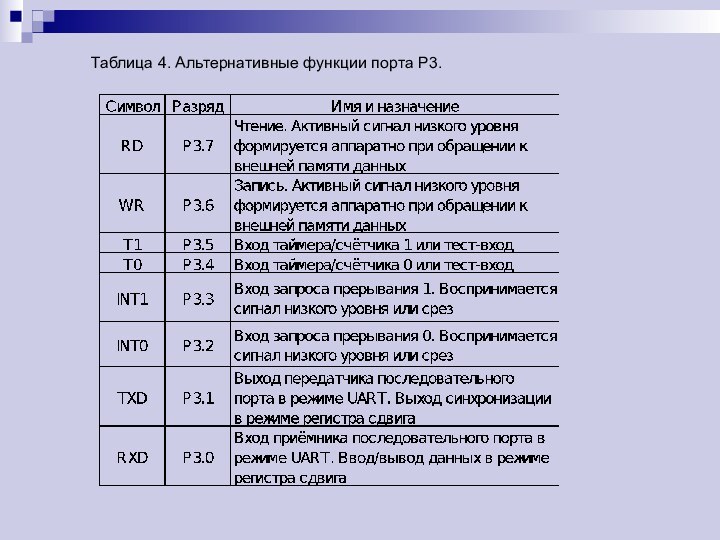

Выходные драйверы портов 0 и 2, а также входной буфер порта 0 используются при обращении к внешней памяти. При этом через порт 0 в режиме временного мультиплексирования сначала выводится младший байт адреса, а затем выдается или принимается байт данных. Через порт 2 выводится старший байт адреса в тех случаях, когда разрядность адреса равна 16 бит. Все выводы порта 3 могут быть использованы для реализации альтернативных функций, перечисленных в табл. 4. Эти функции могут быть задействованы путем записи 1 в соответствующие биты регистра-защёлки (P3.0-P3.7) порта 3.

Слайд 16

Таблица 4. Альтернативные функции порта P3.

Слайд 17

Порт 0 является двунаправленным, а порты

1-3 - квазидвунаправленными. Каждая линия портов может быть использована

независимо для ввода или вывода. По сигналу RST в регистры-защёлки всех портов автоматически записываются единицы, настраивающие их тем самым на режим ввода. Все порты могут быть использованы для организации ввода/вывода информации по двунаправленным линиям передачи. Однако порты 0 и 2 не могут быть использованы для этой цели в случае, если система имеет внешнюю память, связь с которой организуется через общую разделяемую шину адреса/данных, работающую в режиме временного мультиплексирования. Обращение к портам ввода/вывода возможно с использованием команд, оперирующих с байтом, отдельным битом, произвольной комбинацией битов. При этом в тех случаях, когда порт является одновременно операндом и местом назначения результата, устройство управления автоматически реализует специальный режим, который называется “чтение-модификация-запись”. Этот режим обращения предполагает ввод сигналов не с внешних выводов порта, а из его регистразащёлки, что позволяет исключить неправильное считывание ранее выведенной информации. Этот механизм обращения к портам реализован в командах:

• ANL – логическое И, например, ANL P1,А;

• ORL – логическое ИЛИ, например, ORL P2,А;

• XRL – исключающее ИЛИ, например, XRL Р3,А;

• JBC – переход, если в адресуемом бите единица, и последующий сброс бита,например, JBC P1.1, LABEL;

• CPL – инверсия бита, например, CPL Р3.3;

• INC – инкремент порта, например, INC P2;

• DEC – декремент порта, например, DEC P2;

• DJNZ – декремент порта и переход, если его содержимое не равно нулю,например, DJNZ r, LABEL;

• MOV PX.Y,C – передача бита переноса в бит Y порта X;

• SET PX.Y – установка бита Y порта X; • CLR PX.Y – сброс бита Y порта X.

Слайд 18

Таймер/счётчик.

В составе микроконтроллера имеются регистровые

пары с символическими именами TH0, TL0 и TH1, TL1,

на основе которых функционируют два независимых программно-управляемых 16-битных таймера/счётчика событий (T/C0 и T/C1). При работе в качестве таймера содержимое T/C инкрементируется в каждом машинном цикле, то есть через каждые 12 периодов резонатора. При работе в качестве счётчика содержимое T/C инкрементируется под воздействием перехода из 1 в 0 внешнего входного сигнала, подаваемого на соответствующий (T0, T1) вход микроконтроллера. Опрос сигналов выполняется в каждом машинном цикле. Так как на распознавание перехода требуется два машинных цикла, то максимальная частота подсчёта входных сигналов равна 1/24 частоты резонатора. На длительность периода входных сигналов ограничений сверху нет. Для гарантированного прочтения входного считываемого сигнала он должен удерживать значение 1 как минимум в течение одного машинного цикла.

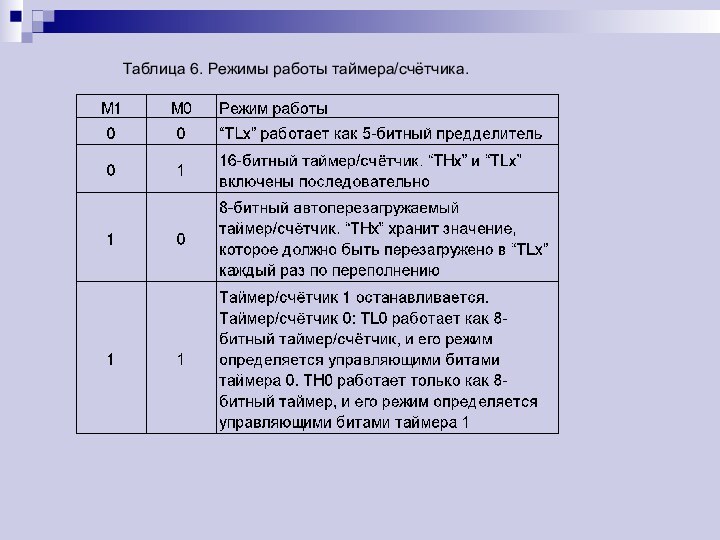

Для управления режимами работы и для организации взаимодействия таймеров с системой прерывания используются два регистра специальных функций TMOD и TCON, описание которых приводится в табл. 5-7. Для обоих T/C режимы работы 0, 1 и 2 одинаковы. Режимы 3 для T/C0 и T/C1 различны.

Слайд 19

Таблица 5. Регистр режима работы таймера/счётчика.

Слайд 20

Таблица 6. Режимы работы таймера/счётчика.

Слайд 21

Таблица 7. Регистр управления/статуса таймера.

Слайд 22

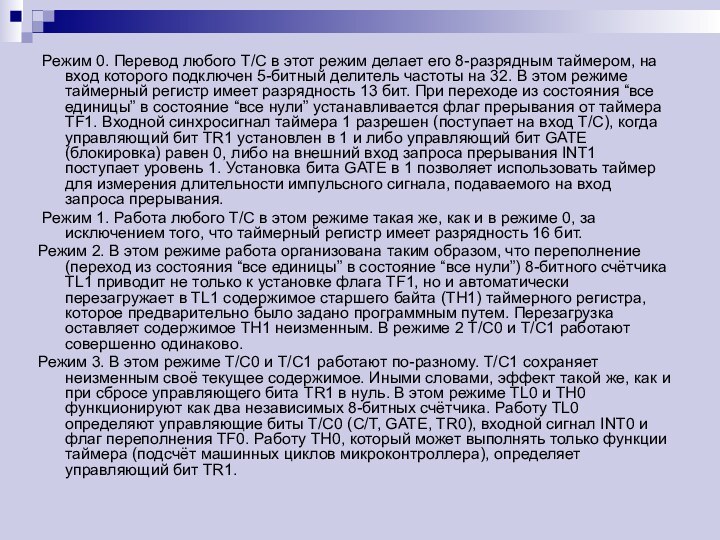

Режим 0. Перевод любого T/C в

этот режим делает его 8-разрядным таймером, на вход которого

подключен 5-битный делитель частоты на 32. В этом режиме таймерный регистр имеет разрядность 13 бит. При переходе из состояния “все единицы” в состояние “все нули” устанавливается флаг прерывания от таймера TF1. Входной синхросигнал таймера 1 разрешен (поступает на вход T/C), когда управляющий бит TR1 установлен в 1 и либо управляющий бит GATE (блокировка) равен 0, либо на внешний вход запроса прерывания INT1 поступает уровень 1. Установка бита GATE в 1 позволяет использовать таймер для измерения длительности импульсного сигнала, подаваемого на вход запроса прерывания.

Режим 1. Работа любого T/C в этом режиме такая же, как и в режиме 0, за исключением того, что таймерный регистр имеет разрядность 16 бит.

Режим 2. В этом режиме работа организована таким образом, что переполнение (переход из состояния “все единицы” в состояние “все нули”) 8-битного счётчика TL1 приводит не только к установке флага TF1, но и автоматически перезагружает в TL1 содержимое старшего байта (TH1) таймерного регистра, которое предварительно было задано программным путем. Перезагрузка оставляет содержимое TH1 неизменным. В режиме 2 T/C0 и T/C1 работают совершенно одинаково.

Режим 3. В этом режиме T/C0 и T/C1 работают по-разному. T/C1 сохраняет неизменным своё текущее содержимое. Иными словами, эффект такой же, как и при сбросе управляющего бита TR1 в нуль. В этом режиме TL0 и TH0 функционируют как два независимых 8-битных счётчика. Работу TL0 определяют управляющие биты T/C0 (C/T, GATE, TR0), входной сигнал INT0 и флаг переполнения TF0. Работу TH0, который может выполнять только функции таймера (подсчёт машинных циклов микроконтроллера), определяет управляющий бит TR1.

Слайд 23

При этом TH0 использует флаг переполнения TF1. Режим

3 используется в тех случаях, когда требуется наличие дополнительного

8-битного таймера или счётчика событий. Можно считать, что в режиме 3 микроконтроллер имеет в своем составе три таймера/счётчика. В том случае, если T/C0 используется в режиме 3, T/C1 может быть или включен, или выключен, или переведен в свой собственный режим 3, или может быть использован последовательным портом в качестве генератора частоты передачи, или, наконец, может быть использован в любом применении, не требующем прерывания.

Последовательный порт

Через универсальный асинхронный приёмопередатчик UART (Universal Asynchronous Receiver-Transmitter) происходит передача информации, представленной последовательным кодом (младшими битами вперед), в полном дуплексном режиме обмена. В состав UART, называемого часто последовательным портом, входят принимающий и передающий сдвигающие регистры, а также специальный буферный регистр (SBUF) приёмопередатчика.

Регистр SBUF

Представляет собой два независимых регистра: буфер приёмника и буфер передатчика. Загрузка байта в SBUF немедленно вызывает начало процесса передачи через последовательный порт. Когда байт считывается из SBUF, это значит, что его источником является приёмник последовательного порта. Запись байта в буфер приводит к автоматической переписи байта в сдвигающий регистр передатчика и инициирует начало передачи байта. Наличие буферного регистра приёмника позволяет совмещать операцию чтения ранее принятого байта с приёмом очередного байта. Если к моменту окончания приёма байта предыдущий байт не был считан, то он будет потерян.

Слайд 24

Последовательный порт может работать в четырех различных режимах.

Режим 0. Информация передаётся и принимается через вход приёмника

RXD. Принимаются и передаются 8 бит данных. Через внешний выход передатчика TXD выдаются импульсы сдвига, которые сопровождают каждый бит. Частота передачи равна 1/12 частоты резонатора. Режим 1. Через TXD передаются или из RXD принимаются 10 бит: старт-бит (0), 8 бит данных и стоп-бит (1). Скорость приёма/передачи – величина переменная и задаётся таймером. Режим 2. Через TXD передаются или из RXD принимаются 11 бит: старт-бит, 8 бит данных, программируемый девятый бит и стоп-бит. При передаче девя- тый бит может использоваться для повышения достоверности передачи путём контроля по чётности и в него можно поместить значение признака паритета из PSW. Частота приёма/передачи выбирается программно и может быть равна 1/32 или 1/64 частоты резонатора в зависимости от SMOD. Режим 3. Совпадает с режимом 2, но частота приёма/передачи является величиной переменной и задаётся таймером. 3.9.2. Регистр SCON Регистр предназначен для управления режимом работы UART. Регистр содержит управляющие биты и девятый бит принимаемых или передаваемых данных RB8 и TB8, а также биты прерывания приёмопередатчика RI и TI. Функциональное назначение битов указано в табл. 8 и 9.

Слайд 25

Таблица 8. Регистр управления/статуса UART.

Слайд 26

Прикладная программа путём

загрузки в два старших разряда SCON определяет режим работы

UART. Во всех режимах передача инициируется любой командой, где SBUF указан как получатель байта. Приём в UART в режиме 0 происходит при условии RI=0 и REN=1. В режимах 1-3 приём начинается с приходом стартбита, если REN=1. В TB8 программно устанавливается значение девятого бита данных, который будет передан в режиме 2 или 3. В RB8 фиксируется в режимах 2 и 3 девятый принимаемый бит данных. В режиме 1, если SM2=0, в бит RB8 заносится стоп-бит. В режиме 0 RB8 не используется. Флаг прерывания передатчика TI устанавливается аппаратно в конце периода передачи восьмого бита данных в режиме 0 и в начале периода передачи стоп-бита в режимах 1-3. Подпрограмма обслуживания этого прерывания должна сбрасывать бит TI. Флаг прерывания приёмника RI устанавливается аппаратно в конце периода приёма восьмого бита данных в режиме 0 и в середине периода приёма стол-бита в режимах 1-3. Подпрограмма обслуживания прерывания должна сбрасывать бит RI.

Таблица 9. Режим работы UART.

Слайд 27

Работа UART в мультиконтроллерных системах.

В системах децентрализованного

управления, которые используются для управления и регулирования в топологически распределенных объектах, возникает задача обмена информацией между множеством микроконтроллеров, объединенных в локальную вычислительно-управляющую сеть. Как правило, локальные сети на основе Intel 8051 имеют магистральную архитектуру с разделяемым моноканалом (коаксиальный кабель, витая пара, оптическое волокно), по которому осущест- вляется обмен информацией между контроллерами. Бит SM2 в SCON позволяет простыми средствами реализовать межконтроллерный обмен. Механизм обмена построен на том, что в режимах 2 и 3 программируемый девятый бит данных при приёме фиксируется в бите RB8. UART может быть запрограммирован таким образом, что при получении стоп-бита прерывание от приёмника будет возможно только при условии RB8=1. Ведущий контроллер всем ведомым передаёт широковещательное сообщение с байтом-идентификатором абонента, которое отличается от байтов данных только тем, что в его девятом бите содержится 1. Ведомые по этому признаку вызывают подпрограммы сравнения байта-идентификатора с кодом собственного сетевого адреса. Адресуемый контроллер сбрасывает свой SM2 и готовится к приёму блока данных. Остальные ведомые микроконтроллеры оставляют неизменными свои SM2=1 и передают управление основной программе. При SM2=1 информационные байты в сети прерывания не вызывают. В режиме 1 автономного микроконтроллера SM2 используется для контроля истинности стоп-бита. В режиме 0 SM2 не используется и должен быть сброшен.

Слайд 28

Скорость приёма/передачи.

Скорость зависит от режима

работы UART. В режиме 0 частота зависит только от резонатора: f0=fрез/12. За один машинный цикл передаётся один бит. В режимах 1-3 скорость зависит от значения управляющего бита SMOD в регистре специальных функций PCON (табл. 10). В режиме 2 частота передачи f2=(2SMOD/64)fрез. В режимах 1 и 3 в формировании частоты передачи кроме управляющего бита SMOD принимает участие таймер 1. При этом частота передачи зависит от частоты переполнения (OVT1) и определяется следующим образом: f1,3=(2SMOD/32)fOVT1. Прерывание от таймера 1 в этом случае должно быть заблоки- ровано. Сам T/C1 может работать и как таймер, и как счётчик событий в любом из трёх режимов. Однако наиболее удобно использовать режим таймера с автоперезагрузкой (старшая тетрада TMOD=0010В). При этом частота передачи определяется выражением f1,3=(2SMOD/32)(fрез/12)(256-(TH1)). В табл. 11 приводится описание способов настройки T/C1 для получения типовых частот передачи данных через UART.

Слайд 29

Таблица 10. Регистр управления мощностью PCON.

Примечание. При

одновременной записи 1 в PD и IDL бит PD

имеет

преимущество. Сброс PCON выполняется путем загрузки в него кода 0XXX0000.

Слайд 30

Таблица 11. Настройка таймера 1 для управления частотой

работы UART.

Таймер/счётчик 1

Слайд 31

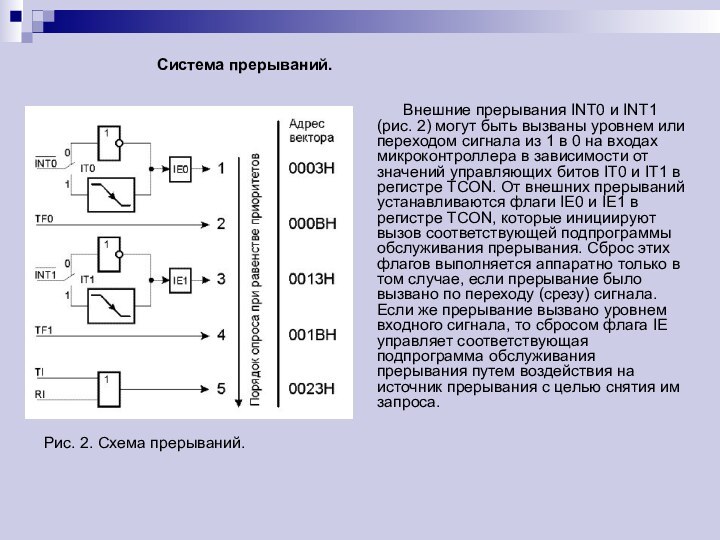

Система прерываний.

Внешние прерывания INT0 и

INT1 (рис. 2) могут быть вызваны уровнем или переходом

сигнала из 1 в 0 на входах микроконтроллера в зависимости от значений управляющих битов IT0 и IT1 в регистре TCON. От внешних прерываний устанавливаются флаги IE0 и IE1 в регистре TCON, которые инициируют вызов соответствующей подпрограммы обслуживания прерывания. Сброс этих флагов выполняется аппаратно только в том случае, если прерывание было вызвано по переходу (срезу) сигнала. Если же прерывание вызвано уровнем входного сигнала, то сбросом флага IE управляет соответствующая подпрограмма обслуживания прерывания путем воздействия на источник прерывания с целью снятия им запроса.

Рис. 2. Схема прерываний.

Слайд 32

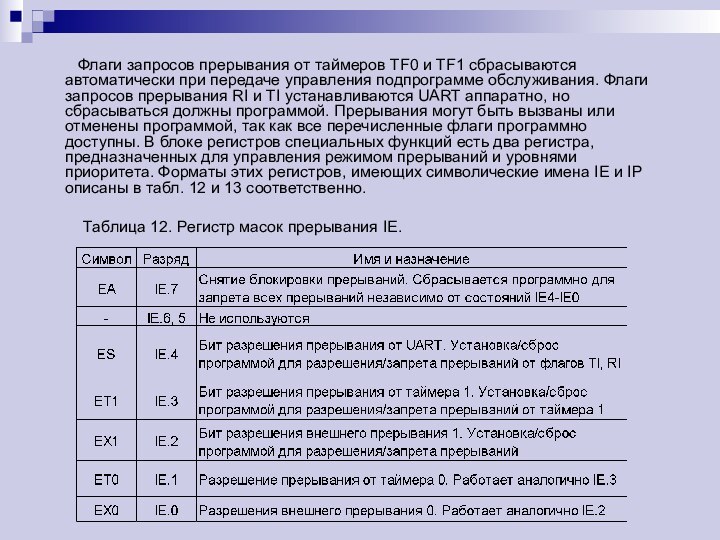

Флаги запросов прерывания

от таймеров TF0 и TF1 сбрасываются автоматически при передаче

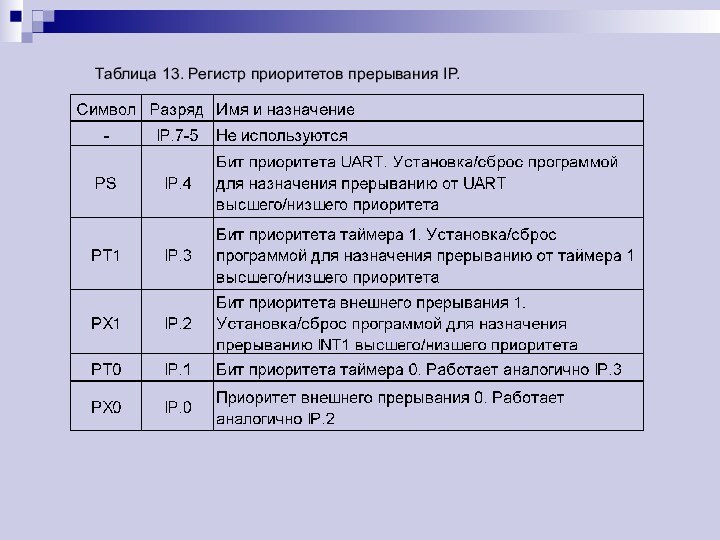

управления подпрограмме обслуживания. Флаги запросов прерывания RI и TI устанавливаются UART аппаратно, но сбрасываться должны программой. Прерывания могут быть вызваны или отменены программой, так как все перечисленные флаги программно доступны. В блоке регистров специальных функций есть два регистра, предназначенных для управления режимом прерываний и уровнями приоритета. Форматы этих регистров, имеющих символические имена IE и IP описаны в табл. 12 и 13 соответственно.

Таблица 12. Регистр масок прерывания IE.

Слайд 33

Таблица 13. Регистр приоритетов прерывания IP.

Слайд 34

Возможность программной установки/сброса любого управляющего бита

в этих двух регистрах делает систему прерываний исключительно гибкой.

Флаги прерываний опрашиваются в каждом машинном цикле. Ранжирование прерываний по приоритету выполняется в течение следующего машинного цикла. Система прерываний сформирует аппаратно вызов LCALL соответствующей подпрограммы обслуживания, если она не заблокирована одним из условий:

• в данный момент обслуживается запрос прерывания равного или более высокого уровня приоритета;

• текущий машинный цикл – не последний в цикле выполняемой команды;

• выполняется команда RETI или любая команда, связанная с обращением к регистрам IE или IP.

Примечание. Если флаг прерывания был установлен, но по одному из перечисленных условий не получил обслуживания и к моменту окончания блокировки уже был сброшен, то запрос прерывания теряется. По аппаратно сформированному коду команды LCALL система прерывания помещает в стек содержимое программного счётчика PC и загружает в PC адрес вектора прерывания соответствующей подпрограммы обслуживания. По этому адресу должна быть расположена команда безусловного перехода JMP к начальному адресу подпрограммы обслуживания прерывания. Эта подпрограмма в случае необходимости должна начинаться командами записи в стек PUSH слова состояния программы PSW, аккумулятора A, расширителя аккумулятора B, указателя данных DPTR и т.д. и заканчиваться командами восстановления из стека POP. Подпрограммы обслуживания прерывания обязательно завершаются командой RETI, по которой в программный счётчик перезагружается из стека сохранённый адрес возврата в основную программу. Команда RET также возвращает управление, но при этом не снимает блокировку прерывания.

Слайд 35

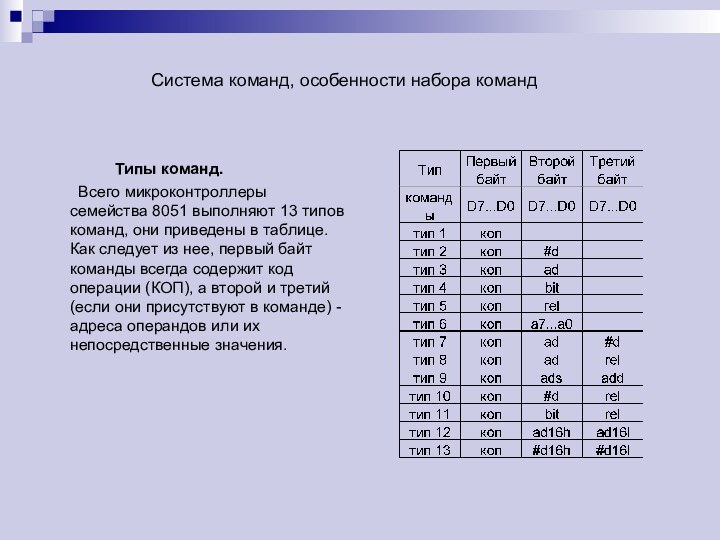

Типы команд.

Всего микроконтроллеры семейства

8051 выполняют 13 типов команд, они приведены в таблице.

Как следует из нее, первый байт команды всегда содержит код операции (КОП), а второй и третий (если они присутствуют в команде) - адреса операндов или их непосредственные значения.

Система команд, особенности набора команд

Слайд 36

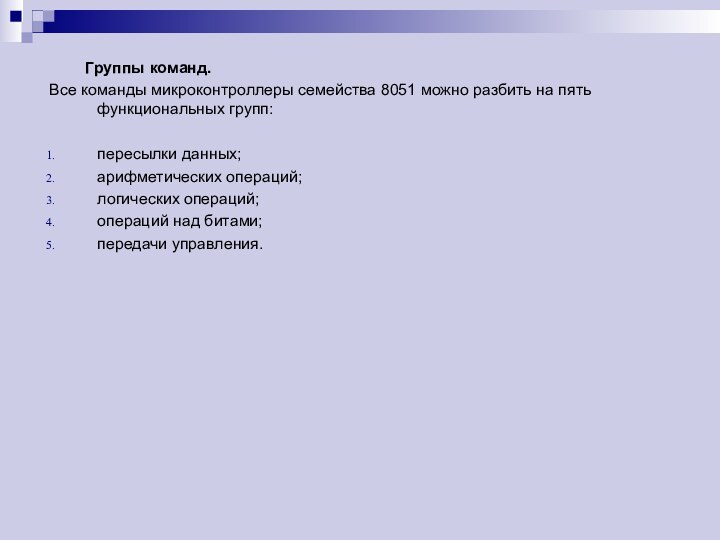

Группы команд.

Все команды микроконтроллеры семейства 8051 можно разбить

на пять функциональных групп:

пересылки данных;

арифметических операций;

логических операций;

операций над битами;

передачи управления.

Слайд 37

Oбозначения, используемые при описании

команд:

Rn (n = 0, 1,..., 7) - регистр общего

назначения в выбранном банке регистров;

@Ri(i= 0, 1) - регистр общего назначения в выбранном банке регистров, используемый в качестве регистра косвенного адреса;

ad - адрес прямоадресуемого байта;

ads - адрес прямо адресуемого байта-источника;

add - адрес прямо адресуемого байта-получателя;

ad11 - 11-разрядный абсолютный адрес перехода;

ad16 - 16-разрядный абсолютный адрес перехода;

rel - относительный адрес перехода;

#d - непосредственный операнд;

Слайд 38

#d16 - непосредственный операнд (2 байта);

bit - адрес

прямо адресуемого бита;

/bit - инверсия прямо адресуемого бита;

А -

аккумулятор;

РС - счетчик команд;

DPTR - регистр указатель данных;

( ) - содержимое ячейки памяти или регистра,

Слайд 39

Команды пересылки данных микроконтроллера 8051

Эта группа представлена

28 командами, их краткое описание приведено в таблице, где

также указаны тип команды (Т) в соответствии с таблицей, ее длина в байтах (В) и время выполнения в машинных циклах (С).

Слайд 40

По команде MOV выполняется пересылка данных из второго

операнда в первый. Эта команда не имеет доступа ни

к внешней памяти данных, ни к памяти программ. Для этих целей предназначены команды M0VX и MOVC соответственно. Первая из них обеспечивает чтение/запись байт из внешней памяти данных, вторая - чтение байт из памяти программ.

По команде XCH выполняется обмен байтами между аккумулятором и ячейкой РПД, а по команде XCHD - обмен младшими тетрадами (битами 0 - 3).

Команды PUSH и РОР предназначены соответственно для записи данных в стек и их чтения из стека .Размер стека ограничен лишь размером резидентной памяти данных. В процессе инициализации микроконтроллеры после сигнала сброса или при включении питающего напряжения в SP заносится код 07Н. Это означает, что первый элемент стека будет располагаться в ячейке памяти с адресом 08Н.

Группа команд пересылок микроконтроллера имеет следующую особенность - в ней нет специальных команд для работы со специальными регистрами: PSW, таймером, портами ввода-вывода. Доступ к ним, как и к другим регистрам специальных функций, осуществляется заданием соответствующего прямого адреса, т.е. это команды обычных пересылок, в которых вместо адреса можно ставить название соответствующего регистра. Например, чтение PSW в аккумулятор может быть выполнено командой:

MOV A, PSW ,которая преобразуется Ассемблером к виду:

MOV А, 0D0h (E5 D0) , где Е5 - код операции, а D0 - операнд (адрес PSW).

Кроме того, следует отметить, что в микроконтроллере аккумулятор имеет два различных имени в зависимости от способа адресации: А - при неявной адресации (например, MOV A, R0) и АСС - при использовании прямого адреса. Первый способ предпочтительнее, однако, не всегда применим.

Слайд 41

Команды арифметических операций микроконтроллера 8051

В данную группу входят

24 команды, краткое описание которых приведено в таблице. Из

нее следует, что микроЭВМ выполняет достаточно широкий набор команд для организации обработки целочисленных данных, включая команды умножения и деления.

В таблице также указаны тип команды (Т) в соответствии с таблицей, ее длина в байтах (В) и время выполнения в машинных циклах (С)

Слайд 42

По результату выполнения команд ADD, ADDC, SUBB, MUL

и DIV устанавливаются флаги PSW, структура которых приведена в

таблице.

Флаг С устанавливается при переносе из разряда D7, т. е. в случае, если результат не помещается в восемь разрядов; флаг АС устанавливается при переносе из разряда D3 в командах сложения и вычитания и служит для реализации десятичной арифметики. Этот признак используется командой DAA.

Флаг OV устанавливается при переносе из разряда D6, т. е. в случае, если результат не помещается в семь разрядов и восьмой не может быть интерпретирован как знаковый. Этот признак служит для организации обработки чисел со знаком.

Наконец, флаг Р устанавливается и сбрасывается аппаратно. Если число единичных бит в аккумуляторе нечетно, то Р = 1, в противном случае Р = 0.

Слайд 43

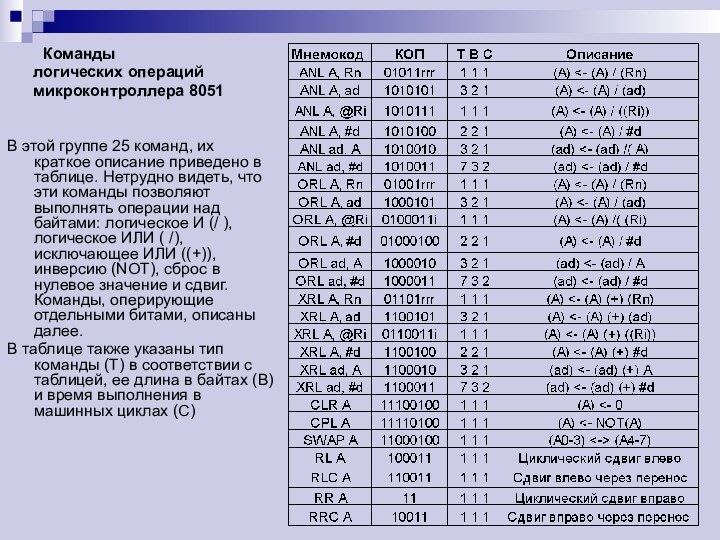

Команды

логических операций

микроконтроллера 8051

В этой группе 25 команд, их краткое

описание приведено в таблице. Нетрудно видеть, что эти команды позволяют выполнять операции над байтами: логическое И (/ ), логическое ИЛИ ( /), исключающее ИЛИ ((+)), инверсию (NOT), сброс в нулевое значение и сдвиг. Команды, оперирующие отдельными битами, описаны далее.

В таблице также указаны тип команды (Т) в соответствии с таблицей, ее длина в байтах (В) и время выполнения в машинных циклах (С)

Слайд 44

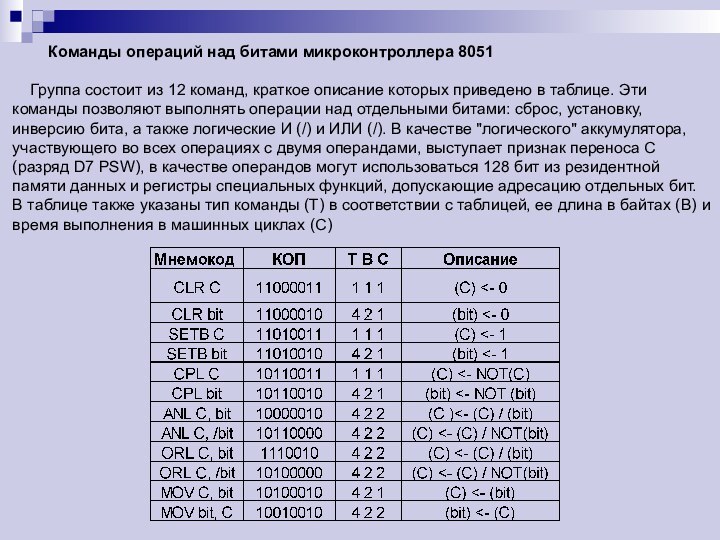

Команды операций над битами микроконтроллера 8051

Группа

состоит из 12 команд, краткое описание которых приведено в

таблице. Эти команды позволяют выполнять операции над отдельными битами: сброс, установку, инверсию бита, а также логические И (/) и ИЛИ (/). В качестве "логического" аккумулятора, участвующего во всех операциях с двумя операндами, выступает признак переноса С (разряд D7 PSW), в качестве операндов могут использоваться 128 бит из резидентной памяти данных и регистры специальных функций, допускающие адресацию отдельных бит.

В таблице также указаны тип команды (Т) в соответствии с таблицей, ее длина в байтах (В) и время выполнения в машинных циклах (С)

Слайд 45

Группа представлена командами безусловного и условного переходов, командами

вызова подпрограмм и командами возврата из подпрограмм.

В таблице также

указаны тип команды (Т) в соответствии с таблицей, ее длина

в байтах (В) и время выполнения в машинных

циклах (С)

Команды

передачи управления

Слайд 46

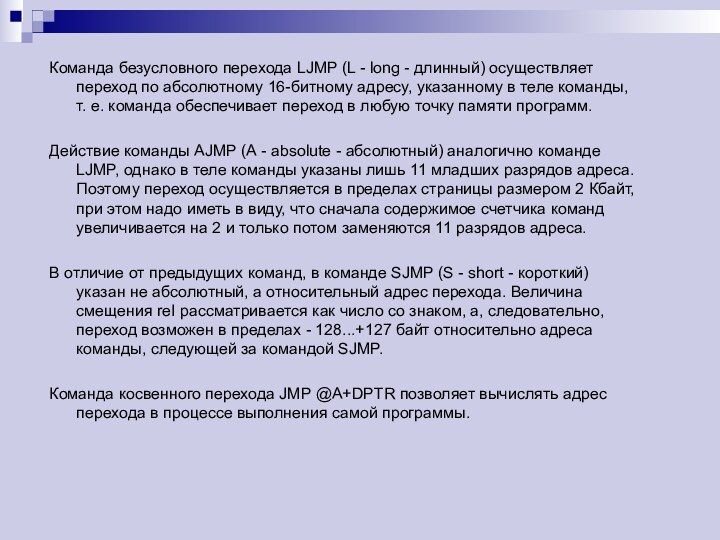

Команда безусловного перехода LJMP (L - long -

длинный) осуществляет переход по абсолютному 16-битному адресу, указанному в

теле команды, т. е. команда обеспечивает переход в любую точку памяти программ.

Действие команды AJMP (А - absolute - абсолютный) аналогично команде LJMP, однако в теле команды указаны лишь 11 младших разрядов адреса. Поэтому переход осуществляется в пределах страницы размером 2 Кбайт, при этом надо иметь в виду, что сначала содержимое счетчика команд увеличивается на 2 и только потом заменяются 11 разрядов адреса.

В отличие от предыдущих команд, в команде SJMP (S - short - короткий) указан не абсолютный, а относительный адрес перехода. Величина смещения reI рассматривается как число со знаком, а, следовательно, переход возможен в пределах - 128...+127 байт относительно адреса команды, следующей за командой SJMP.

Команда косвенного перехода JMP @A+DPTR позволяет вычислять адрес перехода в процессе выполнения самой программы.

Слайд 47

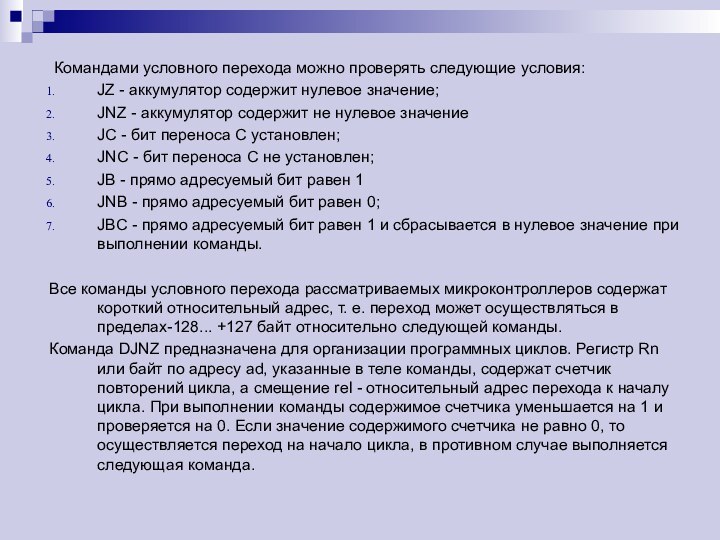

Командами условного перехода можно проверять следующие условия:

JZ

- аккумулятор содержит нулевое значение;

JNZ - аккумулятор содержит

не нулевое значение

JC - бит переноса С установлен;

JNC - бит переноса С не установлен;

JB - прямо адресуемый бит равен 1

JNB - прямо адресуемый бит равен 0;

JBC - прямо адресуемый бит равен 1 и сбрасывается в нулевое значение при выполнении команды.

Все команды условного перехода рассматриваемых микроконтроллеров содержат короткий относительный адрес, т. е. переход может осуществляться в пределах-128... +127 байт относительно следующей команды.

Команда DJNZ предназначена для организации программных циклов. Регистр Rn или байт по адресу ad, указанные в теле команды, содержат счетчик повторений цикла, а смещение rеl - относительный адрес перехода к началу цикла. При выполнении команды содержимое счетчика уменьшается на 1 и проверяется на 0. Если значение содержимого счетчика не равно 0, то осуществляется переход на начало цикла, в противном случае выполняется следующая команда.

Слайд 48

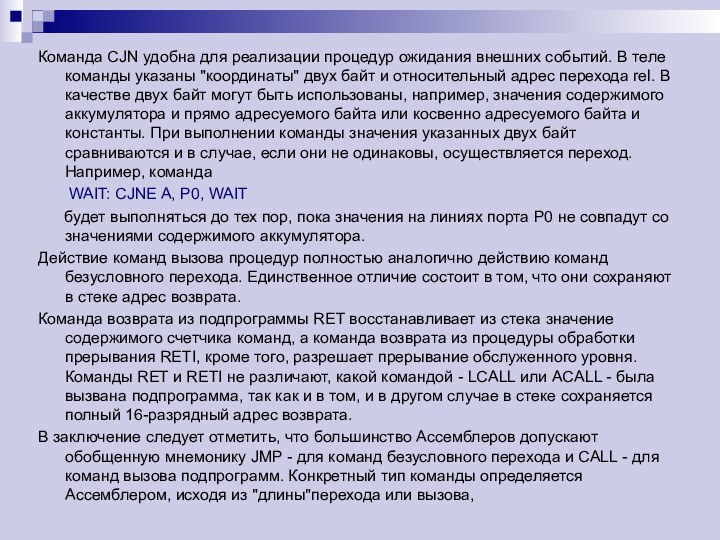

Команда CJN удобна для реализации процедур ожидания внешних

событий. В теле команды указаны "координаты" двух байт и

относительный адрес перехода rel. В качестве двух байт могут быть использованы, например, значения содержимого аккумулятора и прямо адресуемого байта или косвенно адресуемого байта и константы. При выполнении команды значения указанных двух байт сравниваются и в случае, если они не одинаковы, осуществляется переход. Например, команда

WAIT: CJNE A, P0, WAIT

будет выполняться до тех пор, пока значения на линиях порта P0 не совпадут со значениями содержимого аккумулятора.

Действие команд вызова процедур полностью аналогично действию команд безусловного перехода. Единственное отличие состоит в том, что они сохраняют в стеке адрес возврата.

Команда возврата из подпрограммы RET восстанавливает из стека значение содержимого счетчика команд, а команда возврата из процедуры обработки прерывания RETI, кроме того, разрешает прерывание обслуженного уровня. Команды RET и RETI не различают, какой командой - LCALL или ACALL - была вызвана подпрограмма, так как и в том, и в другом случае в стеке сохраняется полный 16-разрядный адрес возврата.

В заключение следует отметить, что большинство Ассемблеров допускают обобщенную мнемонику JMP - для команд безусловного перехода и CALL - для команд вызова подпрограмм. Конкретный тип команды определяется Ассемблером, исходя из "длины"перехода или вызова,

Слайд 49

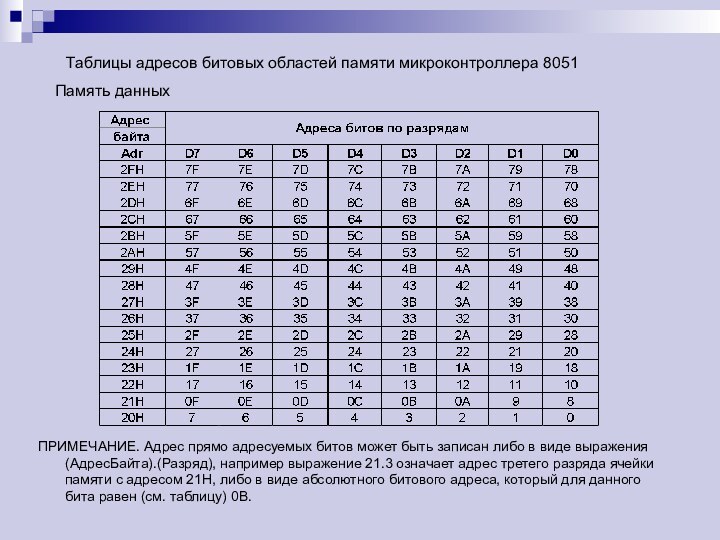

Таблицы адресов битовых областей памяти микроконтроллера 8051

Память

данных

ПРИМЕЧАНИЕ. Адрес прямо адресуемых битов может быть записан

либо в виде выражения (АдресБайта).(Разряд), например выражение 21.3 означает адрес третего разряда ячейки памяти с адресом 21H, либо в виде абсолютного битового адреса, который для данного бита равен (см. таблицу) 0B.