Слайд 2

1971 год- 4004

Первый процессор был представлен публике

15 ноября 1971 года. В то время реализация всех

функций большой ЭВМ на одном маленьком чипе казалась просто чудом. Правда, его возможности были скромными даже для тех лет. Он мог обрабатывать данные порциями по 4 бита, длина машинной команды составляла 8 бит, что позволило иметь 46 инструкций. Память была раздельной для кодов и данных, менее 1 Кб для данных и 4 Кб для команд. Внутри у него было шестнадцать 4-битных регистров и 4-х уровневый стек.

Первый микропроцессор имел 4-битную архитектуру и состоял из 2300 транзисторов. При этом стандартно он работал на частоте 108 КГц (отдельные экземпляры разгонялись до 740 КГц) Техпроцесс по сегодняшним меркам был ужасно "толстым" - целых 10 мкм. Несмотря на то что в компьютерах этот процессор не нашел применения, он все же использовался в калькуляторах Busicom и в различных системах управления (например, уличными светофорами). Через год (1972) был выпущен 4040. Он представлял собой улучшенную версию 4004 - главным нововведением была поддержка прерываний. Кроме того, добавилось 14 новых инструкций и глубина стека была увеличена до 8 уровней, а память команд до 8 Кб.

Слайд 3

1972 год- 8008

8008 был разработан в апреле

1972 года и стал первым 8-битным микропроцессором. Он был

очень похож на 4040: появившиеся 8-битные регистры и увеличенная до 16 Кб память команд - вот, пожалуй, единственные отличия. Стек по-прежнему находился внутри чипа и был ограничен 8 уровнями вложенности. Он все еще позиционировался как процессор для продвинутых калькуляторов и терминалов ввода-вывода.

Слайд 4

1973 год- 8080

Основные идеи архитектуры были

взяты с его предшественника, 8008, - но внутренняя организация

была улучшена Новый процессор имел очень развитую систему команд (78 базовых + более 200 их вариаций). Шина данных была 8-битной, а 16-разрядная адресная шина позволила ему прямо адресовать 64 Кб единой памяти, которая перестала физически разделяться на память команд и память данных. С чипом 8080 связано появление стека внешней памяти, то есть стек стал располагаться не внутри процессора, а в оперативной памяти и мог быть довольно большим. Это позволило использовать в программах алгоритмы рекурсии. "

Восьмидесятка" обладала семью 8-битными регистрами (именовавшимися A - E, H и L, - причем пары BC, DE и HL могли быть скомбинированы в 16-битные регистры). Кроме того, был улучшен техпроцесс, он составил 6 мкм. Количество транзисторов: 6000. Тактовая частота достигла 2 МГц

Помимо всего прочего 8080 послужил основой первому персональному компьютеру Альтаир-8800. Выпущенный в 1975 году фирмой MITS "Альтаир" стоил $439 ($621 в сборке). Клавиатура и монитор в стандартный комплект не входили, оперативная память составляла всего 256 байт (да-да, именно байт, а не килобайт), правда позже стали продаваться блоки расширенной памяти (от 1 до 4 Кб). Тогда же фирмой Digital Research была написана операционная система CP/M. Программисты "Альтаира" умудрялись писать даже игры, а Билл Гейтс и Пол Аллен - написали интерпретатор Бейсика

Слайд 5

1976 год - 8086

Первый 16-битный процессор. Он содержал

рекордное по тому времени количество транзисторов - 29 тысяч

Именно от него ведет свое начало известная на сегодня архитектура x86. Размер его регистров по сравнению с 8080 был увеличен вдвое, что в свою очередь увеличило производительность в 10 раз. Количество базовых команд процессора 8086 возросло до 92. Кроме того, размер информационной шины был увеличен до 16 разрядов. Размер его адресной шины тоже был увеличен - до 20 бит. Это позволило 86-му иметь 1 Мб (220 байт) оперативной памяти

Память 8086 была также доработана: весь мегабайт оперативной памяти не представлялся единым полем, а был разделен на 16 сегментов величиной по 64 Кб. Таким образом, память 8086 можно было представить как объединенную вместе память нескольких 8080. При этом впервые в истории микропроцессоров программа перестала работать непосредственно с одним физическим адресом ячейки памяти. У 86-го процессора было всего 14 регистров. Из них 4 регистра общего назначения (AX, BX, CX, DX), 2 индексных (SI, DI), 2 указательных (BP, SP), 4 сегментных (CS, SS, DS, ES), регистр следующей инструкции IP и регистр флагов (состояний процессора) FLAGS. Все они были 16-битными. Несмотря на то, что они являлись частями целых 16-битных регистров, их можно было использовать как отдельные 8-битные. Благодаря этому, программы, разработанные под 8080, можно было с минимальной переделкой использовать и на 8086 процессоре.

Слайд 6

1977 год - 8088

Через год после презентации 8086,

Intel объявила о разработке его более дешевого аналога -

8088. Он являлся близнецом 8086: 16-битные регистры, 20 адресных линий, тот же набор команд - все то же, за исключением одного, - шина данных была уменьшена до 8 бит. Заполнение 16-битных регистров извне теперь проходило в два раза медленнее. Как следствие - меньшая производительность. Так для чего же Intel понадобилось делать этот шаг? Для того, чтобы угодить фирме IBM, решившей начать производство компьютеров на базе этого процессора. Восьмибитная шина данных позволяла использовать имеющиеся на рынке 8-битные микросхемы памяти и сэкономить на развертывании производства 16-битных. При этом внутренняя структура процессора оставалась по-прежнему 16-битной, что давало важные преимущества по сравнению с другими микропроцессорами и задатком на будущее.

Слайд 7

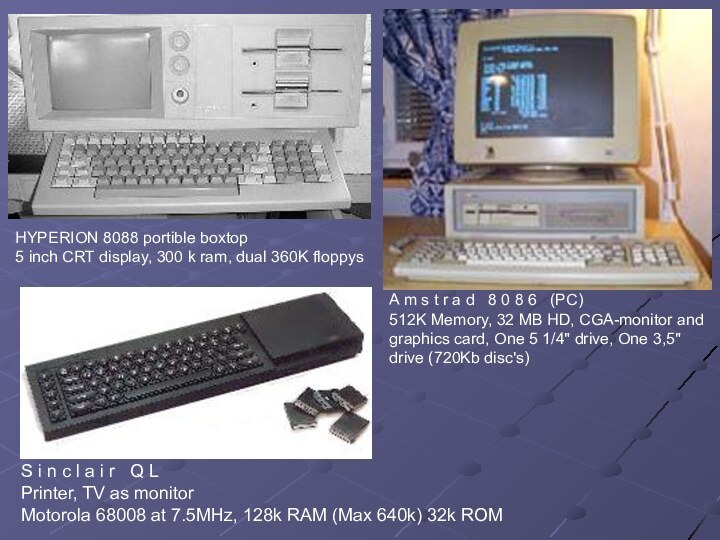

HYPERION 8088 portible boxtop

5 inch CRT display,

300 k ram, dual 360K floppys

A m s t

r a d 8 0 8 6 (PC)

512K Memory, 32 MB HD, CGA-monitor and graphics card, One 5 1/4" drive, One 3,5" drive (720Kb disc's)

S i n c l a i r Q L

Printer, TV as monitor

Motorola 68008 at 7.5MHz, 128k RAM (Max 640k) 32k ROM

Слайд 8

1982 год - 286

В 1982 году фирма Intel

сделала крупный шаг в разработке новых идей: ее следующий

16-битный чип стал первой попыткой создать процессор, который мог бы аппаратно реализовывать многозадачность. Для этого был придуман защищенный режим. Система защиты 286-го процессора позволила разбить всю память и программы на 4 типа (кольца защиты - рис. 3). При этом программа работала только со своими блоками. Если программа обращалась к чужому сегменту памяти, то происходило прерывание с выдачей сообщения об ошибке. Ошибка также возникала, если программа пыталась считать или записать в свой собственный сегмент кода.

Параметры 286-го чипа:134 000 транзисторов, техпроцесс 1.5 мкм, 68 контактных ножек, 16-битная шина данных, 24-битная адресная шина (до 16 Мб физической памяти), 19 "видимых" регистров и 6 "невидимых" Максимальный размер виртуальной памяти (файл подкачки) составил 1008 Мб. Стартовая частота - 6 МГц, затем были созданы модели с частотами от 10 до 25 МГц. Некоторые операции 286-й научился выполнять за меньшое число тактов. Процессор 286 с тактовой частотой 12.5 МГц работал примерно в 6 раз быстрее, чем 8086 с частотой 4.77 МГц. Команда push научилась сохранять в стеке константы. Шины адреса и данных теперь стали раздельными, а не совмещенными на одном множестве ножек. Как и в 8086-м новый процессор имел 6-байтную очередь команд - что-то вроде прообраза будущих конвейеров.

Слайд 9

IBM PS/2 55SX

производство компьютеров на его основе началось

только в 1984-м. Новые компьютеры стали называться IBM PC

AT (Advanced Technology). Выпуск этой модели подхлестнул интерес и к прежней IBM PC, способствуя популяризации архитектуры x86 в целом.

К сожалению, защищенный режим 286-го обладал и недостатками:

Несмотря на возможность адресовать 16 Мб памяти, максимальный размер сегмента остался по-прежнему равным 64 Кб, затрудняя программистам работу с большими массивами данных.

Режим работы с виртуальной памятью не был толком продуман - отсутствовал "прозрачный" для приложений способ перемещения данных операционной системой из памяти на жесткий диск - для реализации этого программам приходилось прибегать к разным ухищрениям вроде "запирания" и "отпирания" указателей на блок памяти.

В защищенном режиме отсутствовала совместимость с программами, написанными для реального режима MS-DOS.

Переход из реального режима в защищенный был односторонним, для обратного перехода требовалась перезагрузка компьютера.

Commodore PC-Compatibles (80286 based)

Слайд 10

1982 год - 386

Обладая полностью 32-битной архитектурой, 386-й

процессор адресовал до 4 Гб (232 байт) физической оперативной

памяти и до 64 Тб виртуальной. Он состоял из 275 000 транзисторов Толщина транзисторных элементов, как и у 286-го, составляла 1.5 мкм (в дальнейшем - 1 мкм), а число ножек увеличилось с 68 до 132.

Умножение двух 16-битных чисел командой MUL R16 выполнялось, в зависимости от числа единичных разрядов, за 9-22 такта. Для сравнения: то же у 286-го срабатывало всегда за 21 такт, а у 86-го аж за 118-133 такта! Математический сопроцессор 80387 не остался в стороне и тоже был оптимизирован - если 287-й выполнял команду извлечение корня FSQRT за 180-186 тактов, то 387-й чип справлялся с этой задачей уже за 122-129 тактов. В среднем количество тактов, необходимых для выполнения команд, уменьшилось в полтора-два раза в сравнении с 286-м и в 3-8 раз в сравнении с оригинальным IBM PC. Кроме того, добавилось несколько продвинутых команд сопроцессора, например вычисление синуса, косинуса и логарифмов.

Первые процессоры стали работать с наивысшей частотой, достигнутой к тому времени для 286-го - 16 МГц, затем появилась 20 МГц модель (16 февраля 1987), а к середине 1988 года предел был отодвинут до 25 МГц (4 апреля 1988). В начале 90-х популярность приобрели 33 МГц модели (10 апреля 1989) Защищенный режим 386-го был существенно доработан. Модель 286-го в целом была сохранена, но добавилось три очень важных аспекта: сколь угодно большой размер сегмента, страничный режим адресации (Page Addressing) и режим виртуального 8086. Все эти аспекты используются операционными системами Windows 95/NT и без них они работать не смогут. Кроме того, 386-й "научился" возвращаться обратно из защищенного режима в реальный без перезагрузки компьютера

Слайд 11

Intel 80386SX + 80387SX, 20 MHz

4 MByte Expandable

up to 16 MByte

102 MB Hard disk

Снятие ограничения на

размер сегмента (вообще-то он ограничен четырьмя гигабайтами, но по-моему для компьютерного ОЗУ это почти бесконечность) тесно связано со страничной организацией памяти. Без использования страниц ограничение на размер остается, правда уже не в 64 Кб как у 86/286, а в 1 Мб. Это объясняется тем, что для указания размера сегмента в таблице дескрипторов отведено 20 бит (у 286-го 16 бит). 220 дает нам 1 Мб комбинаций. Но в дескрипторе сегмента 386-й машины появился очень интересный бит - бит гранулярности. При его включении процессор начинает понимать размер сегмента не в байтах, а в страницах по 4 Кб (4096 байт). Минимальный размер сегмента в этом случае будет равен 4 Кб (1 * 4 Кб), а максимальный - 4 Гб (1 Мб * 4 Кб)

Процессор неправильно выполнял некоторые операции с 32-битными числами, в частности, умножение. Intel моментально устранила ошибку и микросхемы, изготовленные после апреля 1987 года ее не имели, а уже вышедшие чипы были промаркированы "только для 16-битных операций". При попытке установить на такой компьютер Windows 95, Setup выдает сообщение об ошибке "B1". Отличительный признак исправленных процессоров - все они маркируются двойным символом "сигма".

И напоследок кое-что о процессоре 386SX. Он был представлен 16 июня 1988 года как недорогая альтернатива полноценному 80386, который с этого момента стал называться 386DX. в 16-битных приложениях 386SX отставал от старшего брата всего на 10-20%, но в 32-битных разница была существеннее - 50-70%. Поэтому Windows 95 не имело большого смысла ставить на 386SX, в то время как на DX-версию это было вполне оправдано (в случае 8 или более мегабайт памяти). Кроме того, в SX-версию нельзя было добавить свыше 16 Мб оперативной памяти - следствие урезанной до 24 бит адресной шины

Слайд 12

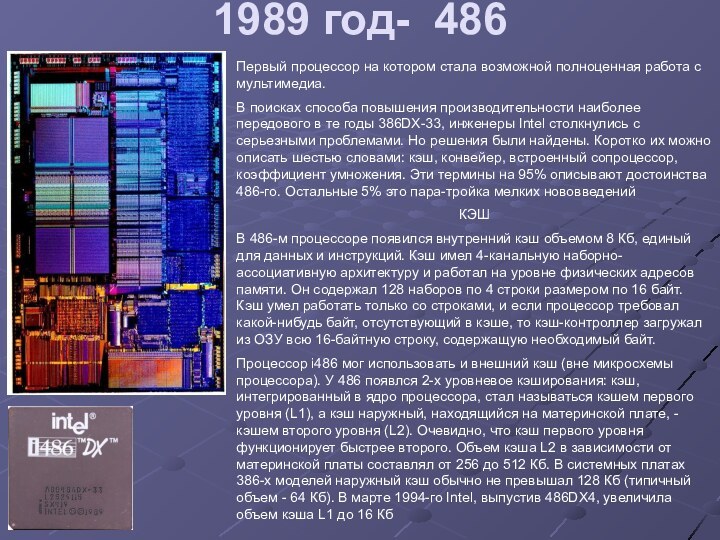

1989 год- 486

Первый процессор на котором стала возможной

полноценная работа с мультимедиа.

В поисках способа повышения производительности наиболее

передового в те годы 386DX-33, инженеры Intel столкнулись с серьезными проблемами. Но решения были найдены. Коротко их можно описать шестью словами: кэш, конвейер, встроенный сопроцессор, коэффициент умножения. Эти термины на 95% описывают достоинства 486-го. Остальные 5% это пара-тройка мелких нововведений

КЭШ

В 486-м процессоре появился внутренний кэш объемом 8 Кб, единый для данных и инструкций. Кэш имел 4-канальную наборно-ассоциативную архитектуру и работал на уровне физических адресов памяти. Он содержал 128 наборов по 4 строки размером по 16 байт. Кэш умел работать только со строками, и если процессор требовал какой-нибудь байт, отсутствующий в кэше, то кэш-контроллер загружал из ОЗУ всю 16-байтную строку, содержащую необходимый байт.

Процессор i486 мог использовать и внешний кэш (вне микросхемы процессора). У 486 появлся 2-х уровневое кэширования: кэш, интегрированный в ядро процессора, стал называться кэшем первого уровня (L1), а кэш наружный, находящийся на материнской плате, - кэшем второго уровня (L2). Очевидно, что кэш первого уровня функционирует быстрее второго. Объем кэша L2 в зависимости от материнской платы составлял от 256 до 512 Кб. В системных платах 386-х моделей наружный кэш обычно не превышал 128 Кб (типичный объем - 64 Кб). В марте 1994-го Intel, выпустив 486DX4, увеличила объем кэша L1 до 16 Кб

Слайд 13

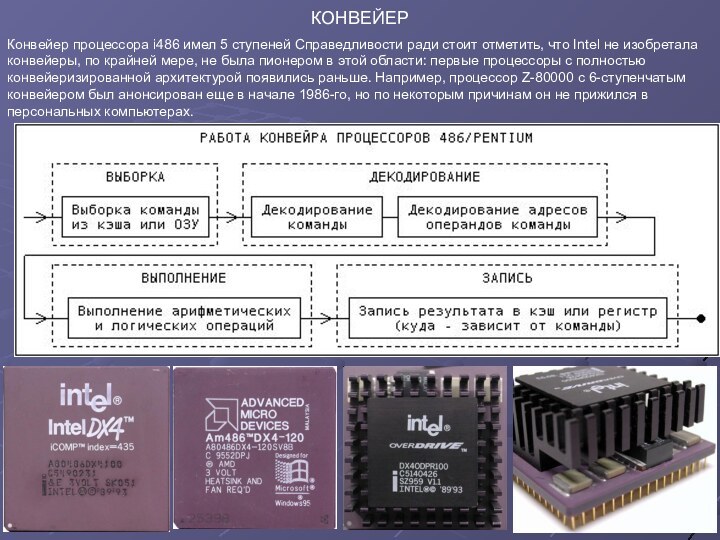

КОНВЕЙЕР

Конвейер процессора i486 имел 5 ступеней Справедливости ради

стоит отметить, что Intel не изобретала конвейеры, по крайней

мере, не была пионером в этой области: первые процессоры с полностью конвейеризированной архитектурой появились раньше. Например, процессор Z-80000 с 6-ступенчатым конвейером был анонсирован еще в начале 1986-го, но по некоторым причинам он не прижился в персональных компьютерах.

Слайд 14

ВСТРОЕННЫЙ СОПРОЦЕССОР

Сопроцессор (FPU, Floating-Point Unit) помогает основному процессору

выполнять математические операции над вещественными числами. Начиная с 8086-го

чипа сопроцессор представлял собой отдельную микросхему, имеющую то же название, что и центральный процессор, только с семеркой на конце: 8087, 80287, 80387. Микросхема 486-го стала первой микросхемой Intel со встроенным FPU. В состав процессора был введен математический сопроцессор, программно совместимый с сопроцессором 387. Процессор 486SX, появившийся 22 апреля 1991 года, отличался тем, что не имел встроенного сопроцессора. Интересно заметить, что существовал 487SX процессор - по сути, аналог 486DX (CPU + FPU), устанавливаемый в гнездо сопроцессора материнской платы 486SX, и отключающий "основной" SX-процессор.

КОЭФФИЦИЕНТ УМНОЖЕНИЯ

Коэффициент умножения - это число на которое надо умножить тактовую частоту материнской платы, чтобы получить частоту работы самого процессора. Но к 486-м, появившимся в 1989 году, он не имел отношения. Эти процессоры работали на частоте системной платы, также как и 386-е. Первым процессором, функционирующим на удвоенной частоте материнской платы, стал i486DX2-50, объявленный 3 марта 1992 года. Коэффициент умножения - одно из важнейших улучшений и оно тесно переплетается с внутренним кэшем. Без кэша вводить коэффициент почти бессмысленно. Именно появление i486DX2-50 и материнских плат, поддерживающих разные частоты шины и коэффициенты умножения, заложило основу для практического "разгона" процессоров.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ

Тактовая частота-25, 33, 50, 66, 75, 100 МГц. Шина 32 бит, 1,25 млн. транзисторов. Техпроцесс 1 мкн., адресуемая память 4 Гб. Виртуальная 64 Тб. Встроенный КЭШ 1 уровня. Конвейер. FPU

Слайд 15

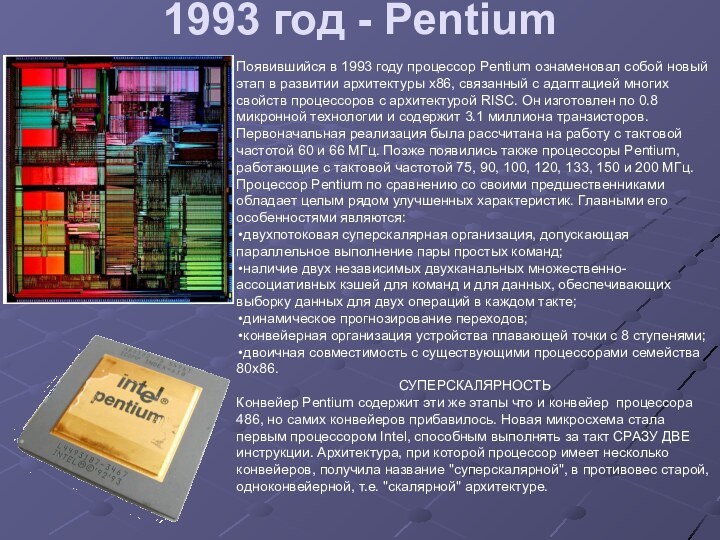

1993 год - Pentium

Появившийся в 1993 году процессор

Pentium ознаменовал собой новый этап в развитии архитектуры x86,

связанный с адаптацией многих свойств процессоров с архитектурой RISC. Он изготовлен по 0.8 микронной технологии и содержит 3.1 миллиона транзисторов. Первоначальная реализация была рассчитана на работу с тактовой частотой 60 и 66 МГц. Позже появились также процессоры Pentium, работающие с тактовой частотой 75, 90, 100, 120, 133, 150 и 200 МГц. Процессор Pentium по сравнению со своими предшественниками обладает целым рядом улучшенных характеристик. Главными его особенностями являются:

двухпотоковая суперскалярная организация, допускающая параллельное выполнение пары простых команд;

наличие двух независимых двухканальных множественно-ассоциативных кэшей для команд и для данных, обеспечивающих выборку данных для двух операций в каждом такте;

динамическое прогнозирование переходов;

конвейерная организация устройства плавающей точки с 8 ступенями;

двоичная совместимость с существующими процессорами семейства 80x86.

СУПЕРСКАЛЯРНОСТЬ

Конвейер Pentium содержит эти же этапы что и конвейер процессора 486, но самих конвейеров прибавилось. Новая микросхема стала первым процессором Intel, способным выполнять за такт СРАЗУ ДВЕ инструкции. Архитектура, при которой процессор имеет несколько конвейеров, получила название "суперскалярной", в противовес старой, одноконвейерной, т.е. "скалярной" архитектуре.

Слайд 16

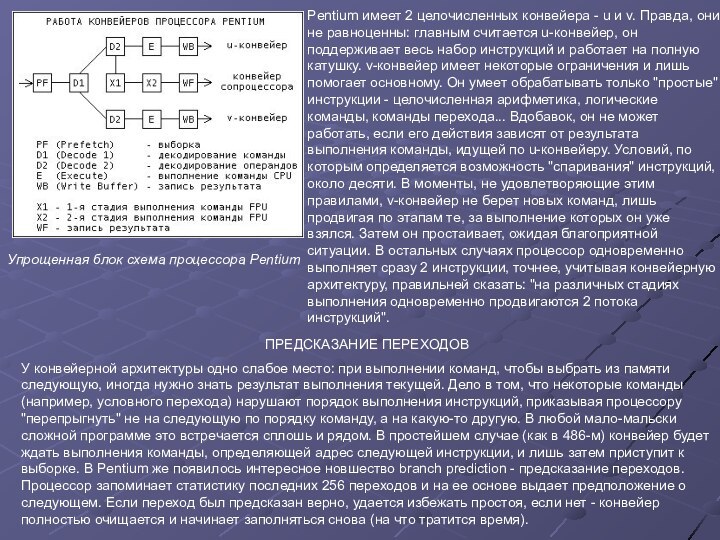

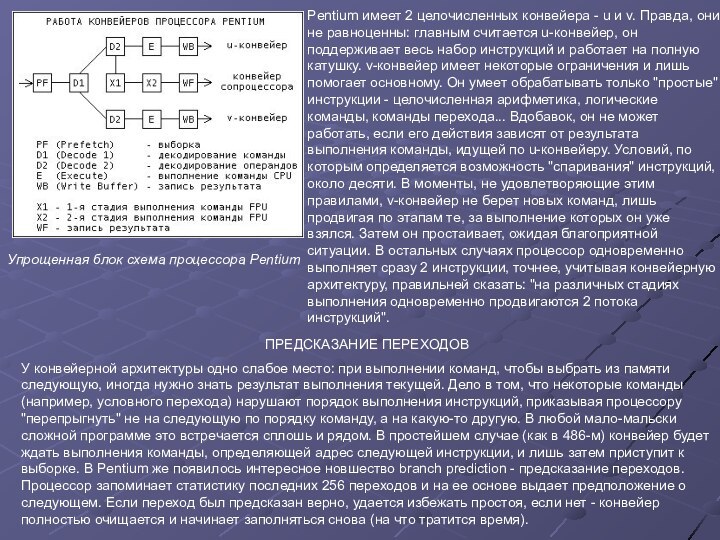

Pentium имеет 2 целочисленных конвейера - u и

v. Правда, они не равноценны: главным считается u-конвейер, он

поддерживает весь набор инструкций и работает на полную катушку. v-конвейер имеет некоторые ограничения и лишь помогает основному. Он умеет обрабатывать только "простые" инструкции - целочисленная арифметика, логические команды, команды перехода... Вдобавок, он не может работать, если его действия зависят от результата выполнения команды, идущей по u-конвейеру. Условий, по которым определяется возможность "спаривания" инструкций, около десяти. В моменты, не удовлетворяющие этим правилами, v-конвейер не берет новых команд, лишь продвигая по этапам те, за выполнение которых он уже взялся. Затем он простаивает, ожидая благоприятной ситуации. В остальных случаях процессор одновременно выполняет сразу 2 инструкции, точнее, учитывая конвейерную архитектуру, правильней сказать: "на различных стадиях выполнения одновременно продвигаются 2 потока инструкций".

Упрощенная блок схема процессора Pentium

ПРЕДСКАЗАНИЕ ПЕРЕХОДОВ

У конвейерной архитектуры одно слабое место: при выполнении команд, чтобы выбрать из памяти следующую, иногда нужно знать результат выполнения текущей. Дело в том, что некоторые команды (например, условного перехода) нарушают порядок выполнения инструкций, приказывая процессору "перепрыгнуть" не на следующую по порядку команду, а на какую-то другую. В любой мало-мальски сложной программе это встречается сплошь и рядом. В простейшем случае (как в 486-м) конвейер будет ждать выполнения команды, определяющей адрес следующей инструкции, и лишь затем приступит к выборке. В Pentium же появилось интересное новшество branch prediction - предсказание переходов. Процессор запоминает статистику последних 256 переходов и на ее основе выдает предположение о следующем. Если переход был предсказан верно, удается избежать простоя, если нет - конвейер полностью очищается и начинает заполняться снова (на что тратится время).

Слайд 17

FPU

2-е по значимости отличие Pentium от 486-го -

быстрый сопроцессор (FPU).

С появлением Pentium стало очевидным: нет смысла

соревноваться с оптимизированным сопроцессором. В результате появился целый ряд игр (Quake, MDK), сотворивших революцию в игровом мире. Благодаря новому FPU, мощность Pentium'а оказалась достаточной для показа Video CD без приобретения MPEG-карт, стоящих сотни долларов.

Причина ускорения сопроцессора кроется в его новой конвейерной архитектуре. Инструкции FPU сначала проходят по u-конвейеру до ступени D2 включительно, после чего сворачивают на ступени X1, X2 и WF конвейера FPU (на схеме). Причем инструкции на целочисленном конвейере могут продвигаться во время просчета длительных инструкций FPU - именно с учетом этого был оптимизирован Quake. Почему конвейер сопроцессора сам не выбирает инструкции? В основном из-за вопросов совместимости, а отчасти - чтобы не заниматься проблемами адресации в защищенном режиме, эту сложную рутину делает основной процессор.

Другая причина ускорения, пусть и не столь важная, - увеличение шины данных до 64 бит. Внешняя шина данных - это магистраль, передающая информацию между процессором и памятью. Особо заметно увеличение шины проявилось в серьезных программах, наподобие AutoCAD или Corel Draw.

КЭШ

С кэшем ситуация неоднозначная. Разумеется, он стал быстрее (в основном, благодаря объему), но появились и минусы. Сначала о главном: кэш L1 в Pentium стал раздельным и увеличился с 8 до 16 Кб - по 8 Кб на кэш команд и кэш данных. Оба кэша поддерживают политику отложенной записи (Write Back), хотя в кэш команд запись обычно не производится.

Нельзя сказать, что это однозначно хорошо. Не случайно процессоры M1 фирмы Cyrix имели общий кэш L1 и в задачах, не требующих интенсивных FPU-вычислений, показывали отличную производительность. Скорее всего, это разделение в Pentium было мотивировано упрощением схем некоторых ступеней конвейеров (ступени PF и WB).

Еще один минус: строки кэша стали 32-байтными (в 486-м строки 16-байтные). С одной стороны, это снизило число "служебных" транзисторов, а с другой - привело к небольшому падению эффективности.

Слайд 18

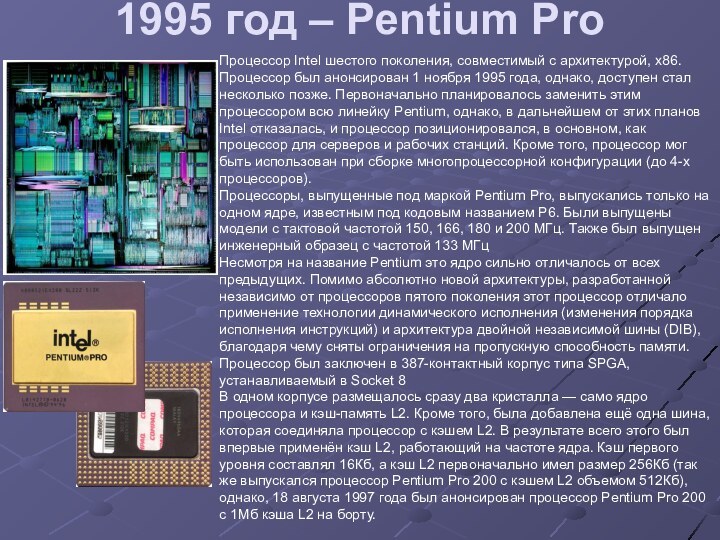

1995 год – Pentium Pro

Процессор Intel шестого поколения,

совместимый с архитектурой, x86. Процессор был анонсирован 1 ноября

1995 года, однако, доступен стал несколько позже. Первоначально планировалось заменить этим процессором всю линейку Pentium, однако, в дальнейшем от этих планов Intel отказалась, и процессор позиционировался, в основном, как процессор для серверов и рабочих станций. Кроме того, процессор мог быть использован при сборке многопроцессорной конфигурации (до 4-х процессоров).

Процессоры, выпущенные под маркой Pentium Pro, выпускались только на одном ядре, известным под кодовым названием P6. Были выпущены модели с тактовой частотой 150, 166, 180 и 200 МГц. Также был выпущен инженерный образец с частотой 133 МГц

Несмотря на название Pentium это ядро сильно отличалось от всех предыдущих. Помимо абсолютно новой архитектуры, разработанной независимо от процессоров пятого поколения этот процессор отличало применение технологии динамического исполнения (изменения порядка исполнения инструкций) и архитектура двойной независимой шины (DIB), благодаря чему сняты ограничения на пропускную способность памяти. Процессор был заключен в 387-контактный корпус типа SPGA, устанавливаемый в Socket 8

В одном корпусе размещалось сразу два кристалла — само ядро процессора и кэш-память L2. Кроме того, была добавлена ещё одна шина, которая соединяла процессор с кэшем L2. В результате всего этого был впервые применён кэш L2, работающий на частоте ядра. Кэш первого уровня составлял 16Кб, а кэш L2 первоначально имел размер 256Кб (так же выпускался процессор Pentium Pro 200 с кэшем L2 объемом 512Кб), однако, 18 августа 1997 года был анонсирован процессор Pentium Pro 200 с 1Мб кэша L2 на борту.

Слайд 19

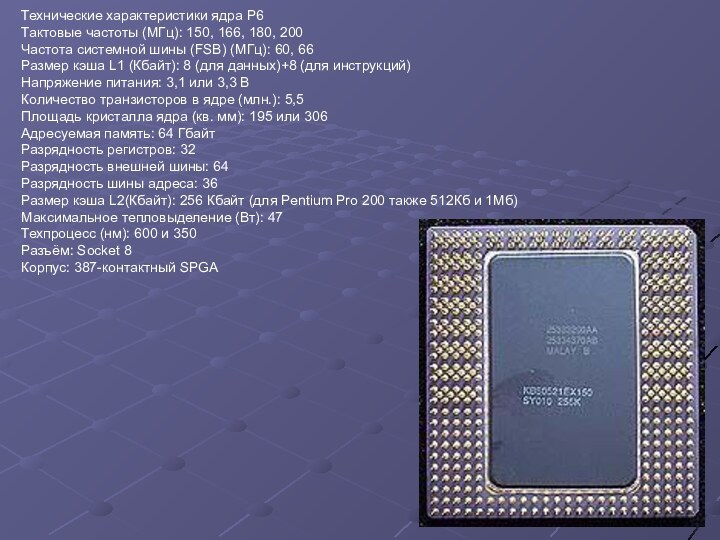

Технические характеристики ядра P6

Тактовые частоты (МГц): 150, 166,

180, 200

Частота системной шины (FSB) (МГц): 60, 66

Размер кэша

L1 (Кбайт): 8 (для данных)+8 (для инструкций)

Напряжение питания: 3,1 или 3,3 В

Количество транзисторов в ядре (млн.): 5,5

Площадь кристалла ядра (кв. мм): 195 или 306

Адресуемая память: 64 Гбайт

Разрядность регистров: 32

Разрядность внешней шины: 64

Разрядность шины адреса: 36

Размер кэша L2(Кбайт): 256 Кбайт (для Pentium Pro 200 также 512Кб и 1Мб)

Максимальное тепловыделение (Вт): 47

Техпроцесс (нм): 600 и 350

Разъём: Socket 8

Корпус: 387-контактный SPGA

Слайд 20

1997 год – Pentium II

Процессоры Intel шестого поколения,

построенный на архитектуре x86 и анонсированный 7 мая 1997

года. Pentium II был основан на модифицированном Pentium Pro с добавленным блоком MMX и улучшенной обработкой 16-разрядных приложений. В системах, построенных на базе Pentium II, начал использоваться новый стандарт памяти — SDRAM, а также новая графическая шина — AGP.

Первые модели Pentium II были предназначены для рынка персональных компьютеров и изготавливались на ядре Klamath. Однако через некоторое время вышли процессоры Pentium II предназначенные для переносных компьютеров (ноутбуки), вышил первые процессоры Xeon построенные на тех же ядрах, что и Pentium II, кроме того, появились новые процессоры под маркой Celeron, представляющие собой урезанный Pentium II.

Klamath

Данное ядро является эволюционным продолжением ядра P6, на котором был построен Pentium Pro. В него было добавлен блок MMX, модернизировано ядро, теперь с 16-битными приложениями этот процессор работал значительно быстрее Pentium Pro. Архитектура двойной независимой шины (DIB) была реализована и в Pentium II. Был увеличен объем кэша L1, теперь он равнялся 32Кб, а кэш L2 теперь работал на половине частоты ядра, но её объем был удвоен и составлял 512Кб. Процессор изготавливался по 350 нм технологии и генерировал большое количество тепла, поэтому вскоре Intel выпустила Pentium II на обновленном ядре Deschutes.

Слайд 21

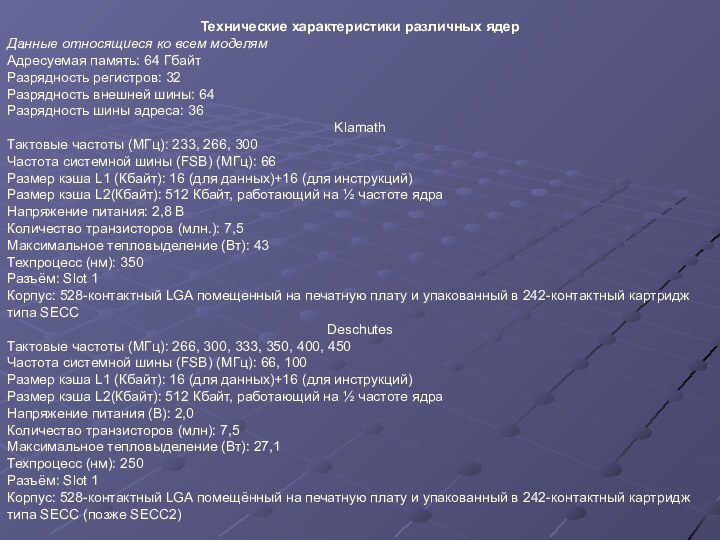

Deschutes

26 января 1998 года Intel анонсировала процессор Pentium

II, построенный на новом ядре, носящее кодовое имя Deschutes.

Чтобы отличить модели, работающие на одинаковых частотах (266 и 300 МГц), но изготовленные на разных ядрах, у процессоров, построенных на ядре Deschutes, в конце названия дописывали литеру «A». В отличие от Klamath, данное ядро изготавливалось по 250 нм техпроцессу, что позволило значительно снизить тепловыделение и поднять планку максимальной частоты до 450 МГц. Также это привело и к уменьшению размера ядра. Первоначально первые процессоры (с частотами 266, 300, 333, 350 и 400 МГц) имели размер кристалла ядра 131 кв. мм, однако с выходом новой ревизии данного ядра ядро у этих процессоров и у модели с частотой 450МГц размеры кристалла уменьшились до 118 кв. мм. Модели с частотой 350МГц и выше работали на шине FSB с частотой 100МГц.

Pentium II OverDrive

Как и раньше процессоры серии OverDrive предназначены для модернизации систем предыдущего поколения. В данном случае для модернизации систем на базе Pentium Pro. Данный процессор был построен на ядре P6T (представляет собой модифицированное ядро Deschutes) и предназначался для установки в разъем Socket 8. То есть, благодаря этому процессору можно было, не меняя материнской платы, приобрести процессор который мало чем отличался от Pentium II. Было выпущено только две модели с частотами 300МГц (шина FSB работала на частоте 60МГц) и 333МГц (с шиной FSB — 66МГц). Оба процессора были выпущены 10 августа 1998 года.

Tonga и Dixon

На основе этих ядер изготавливались мобильные процессоры Mobile Pentium II. Которые отличались от версий для персональных компьютеров пониженным напряжением питания и потребления тока, и, следовательно, имели небольшое тепловыделение, что и позволяло использовать их в ноутбуках и лэптопах.

Слайд 22

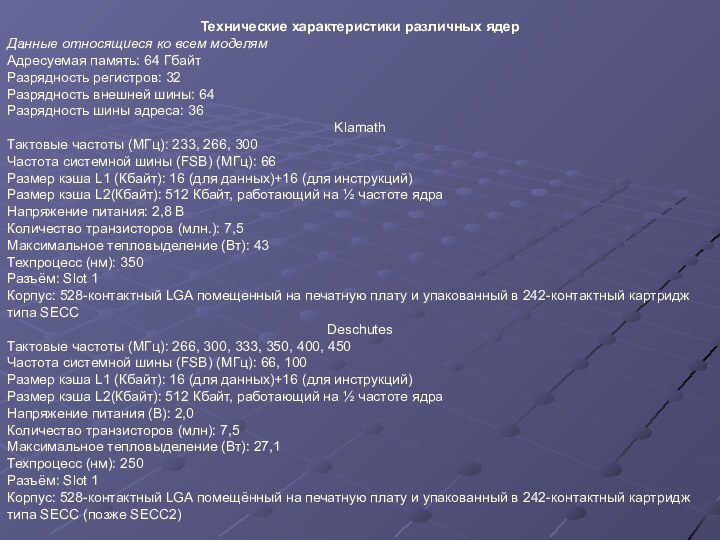

Технические характеристики различных ядер

Данные относящиеся ко всем моделям

Адресуемая

память: 64 Гбайт

Разрядность регистров: 32

Разрядность внешней шины: 64

Разрядность шины

адреса: 36

Klamath

Тактовые частоты (МГц): 233, 266, 300

Частота системной шины (FSB) (МГц): 66

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 512 Кбайт, работающий на ½ частоте ядра

Напряжение питания: 2,8 В

Количество транзисторов (млн.): 7,5

Максимальное тепловыделение (Вт): 43

Техпроцесс (нм): 350

Разъём: Slot 1

Корпус: 528-контактный LGA помещенный на печатную плату и упакованный в 242-контактный картридж типа SECC

Deschutes

Тактовые частоты (МГц): 266, 300, 333, 350, 400, 450

Частота системной шины (FSB) (МГц): 66, 100

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 512 Кбайт, работающий на ½ частоте ядра

Напряжение питания (В): 2,0

Количество транзисторов (млн): 7,5

Максимальное тепловыделение (Вт): 27,1

Техпроцесс (нм): 250

Разъём: Slot 1

Корпус: 528-контактный LGA помещённый на печатную плату и упакованный в 242-контактный картридж типа SECC (позже SECC2)

Слайд 23

Tonga

Тактовые частоты (МГц): 233, 266, 300

Частота системной шины

(FSB) (МГц): 66

Размер кэша L1 (Кбайт): 16 (для данных)+16

(для инструкций)

Размер кэша L2(Кбайт): 512 Кбайт, работающий на ½ частоте ядра

Напряжение питания: 1,6 В

Количество транзисторов (млн.): 7,5

Максимальное тепловыделение (Вт): 11,6

Техпроцесс (нм): 250

Разъём: 240-контактный MMC

Корпус: 615-контактный BGA помещенный на печатную плату и упакованный в 240-контактный картридж типа MMC (Mini Cartridge Connector)

Dixon

Тактовые частоты (МГц): 266, 300, 333, 366, 400

Частота системной шины (FSB) (МГц): 66, 100

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 256 Кбайт, работающий на частоте ядра

Напряжение питания: 1,6; 1,55 или 1,5 В

Количество транзисторов (млн.): 27,4

Максимальное тепловыделение (Вт): 13,1

Техпроцесс (нм): 250

Разъём: Socket 615, либо MMC (Mobile Module Connector)

Корпус: 615-контактный BGA или mBGA.

Слайд 24

1998 год – Celeron

Celeron — большое семейство бюджетных

x86-совместимых процессоров компании Intel. Семейство Celeron предназначалось для построения

дешёвых компьютеров. Процессоры Celeron изначально позиционировались как low-end процессоры, и предназначались для расширения доли рынка компании Intel. Одной из причин невысокой цены является их низкая, по отношению к старшим процессорам, производительность.

Первый процессор семейства Celeron был анонсирован 15 апреля 1998 года и был построен на основе Pentium II. Позже вышли процессоры основанные на Pentium III, Pentium 4 и Pentium M.

До выпуска Celeron`а Intel активно вытеснялась с рынка low-end такими конкурентами, как AMD, со своим процессором K6 и IDT, со своим процессором Winchip. Оба процессора были предназначены для уже устаревающей платформы Socket 7. Конкурировать с ними мог тогда только Pentium MMX, в то время, уже, позиционирующийся как процессор для low-end рынка. Но производительности Pentium MMX уже начинало не хватать, и Intel решает выпустить процессор построенный на архитектуре Pentium II и при этом с ценой привлекательной для построения малобюджетной системы. В результате Intel удалось отвоевать большую долю рынка. Процессор, как и Pentium II, выпускался для Slot 1, но использовал корпус типа SEPP, в котором нет верхней пластиковой крышки.

Слайд 25

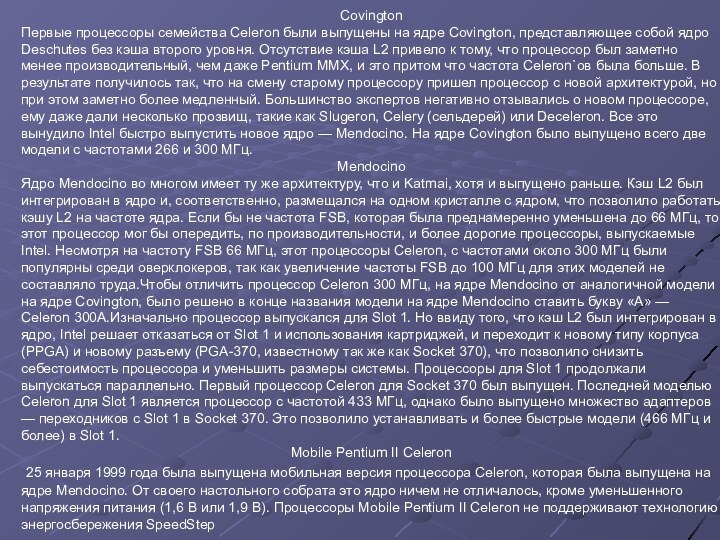

Covington

Первые процессоры семейства Celeron были выпущены на ядре

Covington, представляющее собой ядро Deschutes без кэша второго уровня.

Отсутствие кэша L2 привело к тому, что процессор был заметно менее производительный, чем даже Pentium MMX, и это притом что частота Celeron`ов была больше. В результате получилось так, что на смену старому процессору пришел процессор с новой архитектурой, но при этом заметно более медленный. Большинство экспертов негативно отзывались о новом процессоре, ему даже дали несколько прозвищ, такие как Slugeron, Celery (сельдерей) или Deceleron. Все это вынудило Intel быстро выпустить новое ядро — Mendocino. На ядре Covington было выпущено всего две модели с частотами 266 и 300 МГц.

Mendocino

Ядро Mendocino во многом имеет ту же архитектуру, что и Katmai, хотя и выпущено раньше. Кэш L2 был интегрирован в ядро и, соответственно, размещался на одном кристалле с ядром, что позволило работать кэшу L2 на частоте ядра. Если бы не частота FSB, которая была преднамеренно уменьшена до 66 МГц, то этот процессор мог бы опередить, по производительности, и более дорогие процессоры, выпускаемые Intel. Несмотря на частоту FSB 66 МГц, этот процессоры Celeron, с частотами около 300 МГц были популярны среди оверклокеров, так как увеличение частоты FSB до 100 МГц для этих моделей не составляло труда.Чтобы отличить процессор Celeron 300 МГц, на ядре Mendocino от аналогичной модели на ядре Covington, было решено в конце названия модели на ядре Mendocino ставить букву «A» — Celeron 300A.Изначально процессор выпускался для Slot 1. Но ввиду того, что кэш L2 был интегрирован в ядро, Intel решает отказаться от Slot 1 и использования картриджей, и переходит к новому типу корпуса (PPGA) и новому разъему (PGA-370, известному так же как Socket 370), что позволило снизить себестоимость процессора и уменьшить размеры системы. Процессоры для Slot 1 продолжали выпускаться параллельно. Первый процессор Celeron для Socket 370 был выпущен. Последней моделью Celeron для Slot 1 является процессор с частотой 433 МГц, однако было выпущено множество адаптеров — переходников с Slot 1 в Socket 370. Это позволило устанавливать и более быстрые модели (466 МГц и более) в Slot 1.

Mobile Pentium II Celeron

25 января 1999 года была выпущена мобильная версия процессора Celeron, которая была выпущена на ядре Mendocino. От своего настольного собрата это ядро ничем не отличалось, кроме уменьшенного напряжения питания (1,6 В или 1,9 В). Процессоры Mobile Pentium II Celeron не поддерживают технологию энергосбережения SpeedStep

Слайд 26

1999 год – Pentium III

Как и в случае

с Pentium II, компания Intel выпустила несколько модификаций процессора

Pentium III: Pentium III Xeon, Pentium III Celeron, Mobile Pentium III и обычный Pentium III для персональных компьютеров. Процессор Pentium III унаследовал большую часть архитектуры Pentium II — это и блок MMX и динамическое выполнение команд и многое другое, однако, он получил и новые уникальные возможности, которых не было в Pentium II, и которые давали ему неоспоримое преимущество в производительности при той же тактовой частоте

Katmai

Первое ядро используемое в Pentium III. Оно во многом было аналогично ядру Deschutes, используемому в последних моделях Pentium II. Но в новом ядре был расширен набор SIMD-расширений, который теперь включал в себя набор команд известный как SSE. Был усовершенствован механизм потокового доступа к памяти. Но процессор всё ещё выпускался в корпусе SECC2 и устанавливался в разъем Slot 1. Изначально процессор работал с частотой FSB равной 100МГц, однако затем, 27 сентября 1999 года, Intel выпустила процессор, который имел шину FSB работающую на частоте 133МГц. Чтобы отличать версии процессоров, имеющих разную частоту системной шины, было решено добавлять в конце названия процессора литеру «B», которая должна обозначать процессоры имеющие системную шину 133МГц.

Слайд 27

Coppermine

25 октября 1999 года корпорация Intel выпускает новую

версию Pentium III, построенную на новом ядре Coppermine. Coppermine

очень похож на своего предшественника — ядро Katmai (разработчики это и не скрывали), он выполнен с использованием 180 нм техпроцесса, теперь кэш L2 интегрирован в ядро и работает на частоте ядра. Были выпущены модели имевшие частоту FSB как 100МГц, так и 133МГц, для их различия по прежнему использовалась литера «B» в конце названия. А чтобы отличать процессоры, работающие на одной частоте ядра, но имевшие разные ядра (Katmai или Coppermine) было решено в конце названия процессора, основанного на ядре Coppermine, писать литеру «E» (например, Pentium III-533EB основан на ядре Coppermine и имеет частоту FSB равной 133МГц). Новый процессор имел новый тип корпуса — 370-контактный FC-PGA и устанавливался в разъём Socket 370, однако многие модели были выпущены и в модификации для Slot 1. В новом процессоре удалось снизить напряжение питания, что существенно уменьшило количество тепла, выделяемое процессором. В процессорах на ядре Coppermine, работающих на частотах, больших 1ГГц у Intel возникли сложности с интегрированным кэшем L2, который не мог работать на частоте большей 1ГГц. И первые из этих процессоров были нестабильны в работе.

Tualatin

На новом процессоре испытали новую технологию производства — их изготавливали по 130 нм техпроцессу. Других изменений в этом ядре было не много, среди них — технология «Data Prefetch Logic», которая должна была повысить производительность, загружая в кэш-память данные, необходимые в данный момент приложению. В результате процессор оказался быстрее чем Pentium 4, работающий на большой частоте. Так как разработчики не хотели, чтобы этот процессор конкурировал с Pentium 4, они урезали кэш-память L2, в настольной версии процессора, до 256Кб. Процессоры для серверов же выпускались с 512Кб кэш-памяти L2 (у них в конце названия имеется буква «S»). Процессор был предназначен для Socket 370, но имел тип корпуса FCPGA2 (похож на первые Pentium 4) и работал, в основном, с напряжением питания 1,5 В, поэтому он не был совместим со старыми материнскими платами.

Mobile Pentium III

Мобильные версии процессора Pentium III выпускались на ядрах Coppermine и Tualatin, Эти процессоры отличались от настольных (desktop) версий пониженным напряжением питания и поддержкой технологии SpeedStep, которая уменьшала частоту ядра процессора (следовательно, и потребляемую мощность). Все процессоры серии Mobile в режиме энергосбережения также уменьшали и напряжение питания.

Слайд 28

1999 год – Celeron

Coppermine-128

Процессор относится к семейству Pentium

III Celeron. Часто, чтобы отличать процессоры Pentium III Celeron

от процессоров Pentium II Celeron, первые часто именуют Celeron II. Ядро Coppermine-128 построено на ядре Coppermine, при этом, как и раньше, кэш L2 равен 128Кбайт, что отражено в названии ядра; частота шины FSB составляет 66 МГц. В остальном ядра фактически идентичны. 3 января 2001 года Intel представляет Celeron 800, первый процессор семейства Celeron, который использовал шину FSB частотой 100МГц.

Первые процессоры Celeron на ядре Coppermine-128 (степпинг cB0) работали при напряжении питания ядра 1,5 В, однако позже были выпущены процессоры, которые были основаны на новой ревизии ядра, и использовали напряжение 1,7 В (степпинг cC0) и 1,75 В (степпинг cD0). В отличие от процессоров на степпинге cB0 обновленные процессоры были более стабильны и легче разгонялись

Новые процессоры, как и Pentium III, производились для Socket 370 и использовали тип корпуса FC-PGA.

Mobile Pentium III Celeron

В процессорах использовались ядро Coppermine-128, но процессоры изначально использовали системную шину частотой 100МГц, а позже были выпущены процессоры и с шиной 133МГц. Процессоры серии Mobile Pentium III Celeron не поддерживают технологию SpeedStep. В серии Pentium III Celeron на ядре Coppermine-128 так же были выпущены мобильные процессоры с пониженным напряжением, предназначенные для установки в недорогие портативные мобильные ПК. Были выпущены модели Mobile Pentium III Celeron 600 L и 500 L (21 мая 2001 года). Процессоры обладали пониженным напряжением (1,35В, против 1,6 у обычной мобильной версии Celeron Coppermine-128). Были выпущены процессоры Mobile Pentium III Celeron со сверхнизким потреблением.А также Mobile Pentium III Celeron 600 U и 500 U. Процессоры серии Mobile Pentium III Celeron на ядре Coppermine-128 выпускались в 495-контактных корпусах типа mPGA2 или BGA2 и предназначались для установки, соответственно, в Socket 495 или припаивались непосредственно к материнской плате.

Слайд 29

Tualatin

Следующая серия процессоров Celeron была построена на ядре

Tualatin. В новом Celeron`е Intel использовала кэш-память L2 объемом

256 Кбайт и шину FSB частотой 100МГц. Первоначально, 3 января 2002 года, стали доступны модели с частотами 1,0 и 1,1 ГГц, чтобы отличать их от аналогичных моделей на ядре Coppermine-128, в конце названия новых процессоров добавляли букву «A». Данное ядро является последним, использующее архитектуру P6, хотя в дальнейшем были выпущены Celeron M, он предназначался только для мобильных ПК.

Mobile Pentium III Celeron

21 января 2002 года Intel выпускает процессоры Celeron на ядре Tualatin для мобильных ПК. От настольных процессоров они отличались пониженным напряжением питания. В мобильной серии Celeron`ов на ядре Tualatin были выпущены процессоры, у которых частота FSB составляла 133МГц. Как и прежде было доступно три серии процессоров: мобильные процессоры, процессоры с пониженным энергопотреблением (серия Low Voltage) и процессоры со сверхнизким энергопотреблением (серия Ultra Low Voltage). Как и раньше, процессоры серии Mobile Pentium III Celeron не поддерживают технологию SpeedStep.

Слайд 30

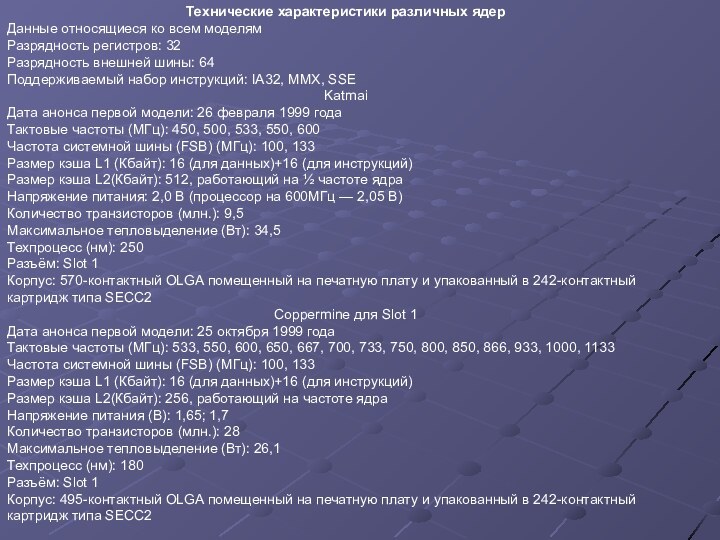

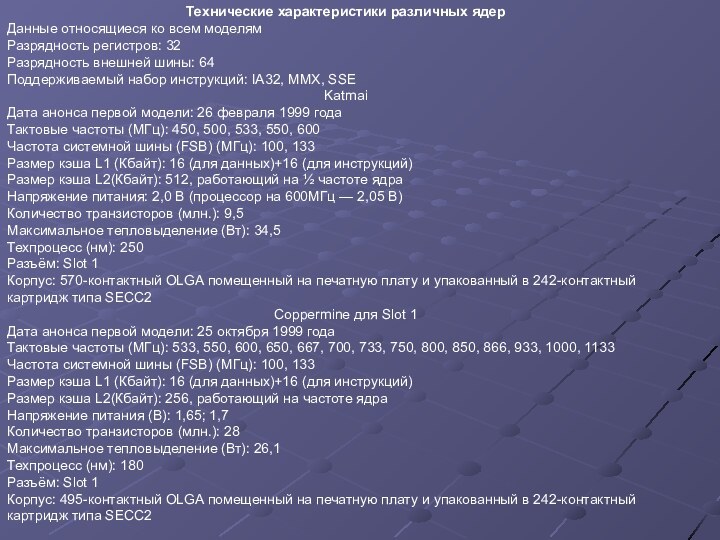

Технические характеристики различных ядер

Данные относящиеся ко всем моделям

Разрядность регистров: 32

Разрядность внешней шины: 64

Поддерживаемый набор инструкций: IA32,

MMX, SSE

Katmai

Дата анонса первой модели: 26 февраля 1999 года

Тактовые частоты (МГц): 450, 500, 533, 550, 600

Частота системной шины (FSB) (МГц): 100, 133

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 512, работающий на ½ частоте ядра

Напряжение питания: 2,0 В (процессор на 600МГц — 2,05 В)

Количество транзисторов (млн.): 9,5

Максимальное тепловыделение (Вт): 34,5

Техпроцесс (нм): 250

Разъём: Slot 1

Корпус: 570-контактный OLGA помещенный на печатную плату и упакованный в 242-контактный картридж типа SECC2

Coppermine для Slot 1

Дата анонса первой модели: 25 октября 1999 года

Тактовые частоты (МГц): 533, 550, 600, 650, 667, 700, 733, 750, 800, 850, 866, 933, 1000, 1133

Частота системной шины (FSB) (МГц): 100, 133

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 256, работающий на частоте ядра

Напряжение питания (В): 1,65; 1,7

Количество транзисторов (млн.): 28

Максимальное тепловыделение (Вт): 26,1

Техпроцесс (нм): 180

Разъём: Slot 1

Корпус: 495-контактный OLGA помещенный на печатную плату и упакованный в 242-контактный картридж типа SECC2

Слайд 31

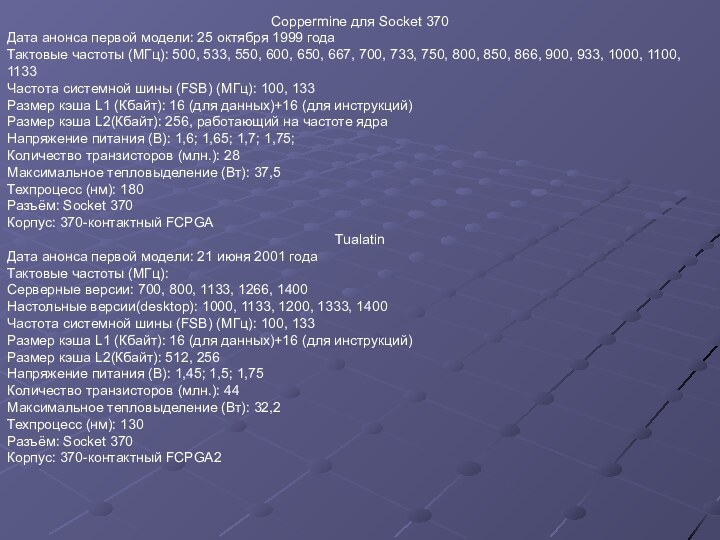

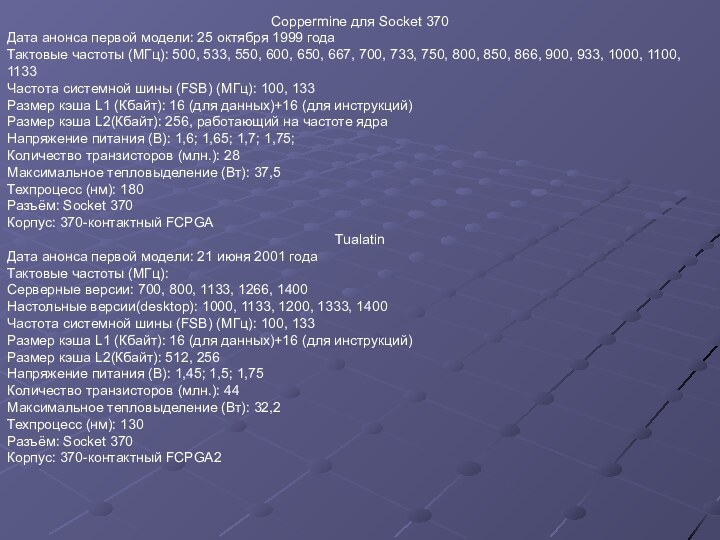

Coppermine для Socket 370

Дата анонса первой модели: 25

октября 1999 года

Тактовые частоты (МГц): 500, 533, 550, 600,

650, 667, 700, 733, 750, 800, 850, 866, 900, 933, 1000, 1100, 1133

Частота системной шины (FSB) (МГц): 100, 133

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 256, работающий на частоте ядра

Напряжение питания (В): 1,6; 1,65; 1,7; 1,75;

Количество транзисторов (млн.): 28

Максимальное тепловыделение (Вт): 37,5

Техпроцесс (нм): 180

Разъём: Socket 370

Корпус: 370-контактный FCPGA

Tualatin

Дата анонса первой модели: 21 июня 2001 года

Тактовые частоты (МГц):

Серверные версии: 700, 800, 1133, 1266, 1400

Настольные версии(desktop): 1000, 1133, 1200, 1333, 1400

Частота системной шины (FSB) (МГц): 100, 133

Размер кэша L1 (Кбайт): 16 (для данных)+16 (для инструкций)

Размер кэша L2(Кбайт): 512, 256

Напряжение питания (В): 1,45; 1,5; 1,75

Количество транзисторов (млн.): 44

Максимальное тепловыделение (Вт): 32,2

Техпроцесс (нм): 130

Разъём: Socket 370

Корпус: 370-контактный FCPGA2

![North [noӨ]- северwest [west]- западeast [i:st]-востокsouth [sauӨ]- юг](/img/tmb/14/1373284/a7b4677c05e90056bd0fec95fddc6775-210x.jpg)