Слайд 2

Компью́терная па́мять (устройство хранения информации, запоминающее устройство) —

часть вычислительной машины, физическое устройство или среда для хранения

данных в течение определённого времени.

В основе работы запоминающего устройства может лежать любой физический эффект, обеспечивающий приведение системы к двум или более устойчивым состояниям. В современной компьютерной технике часто используются физические свойства полупроводников. Устойчивые состояния, определяемые направлением намагниченности, позволяют использовать для хранения данных разнообразные магнитные материалы. Наличие или отсутствие заряда в конденсаторе также может быть положено в основу системы хранения.

Средства машинного хранения данных, используемые в персональных компьютерах: — это модули оперативной памяти, жёсткие диски (винчестеры), дискеты (гибкие магнитные диски), CD или DVD диски, а также устройства флэш-памяти.

В зависимости от назначения и особенностей реализации устройств компьютерной памяти, по-разному подходят и к вопросам их классификации.

Так, при рассмотрении удалённости и доступности памяти для центрального процессорного устройства различают: первичную, вторичную или третичную память.

Способность или неспособность к хранению данных в условиях отключения внешних источников питания определяют энергонезависимость или энергозависимость устройств хранения данных.

Слайд 3

Особенности механизмов чтения-записи отличают устройства памяти только для

чтения (ПЗУ), доступные для разовой записи и множества считываний

(WORM) или пригодные для полноценного выполнения операций чтения-записи. Порядок выборки определяет память произвольного или последовательного доступа с блочной или файловой адресацией.

Впрочем, довольно часто к вопросу классификации подходят проще, например, различая устройства в зависимости от используемого типа носителя — полупроводниковая память, оптическая память, магнитооптическая память, магнитная память и т.п.

Различные типы памяти обладают разными преимуществами, из-за чего в большинстве современных компьютеров используются сразу несколько типов устройств хранения данных.

Слайд 4

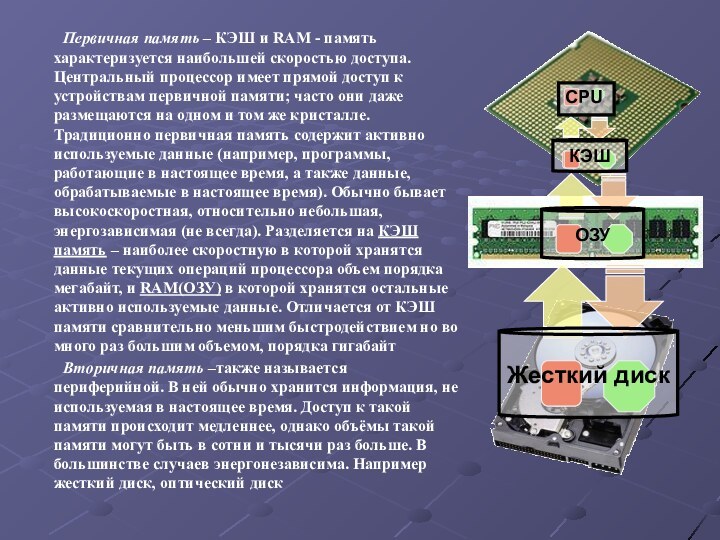

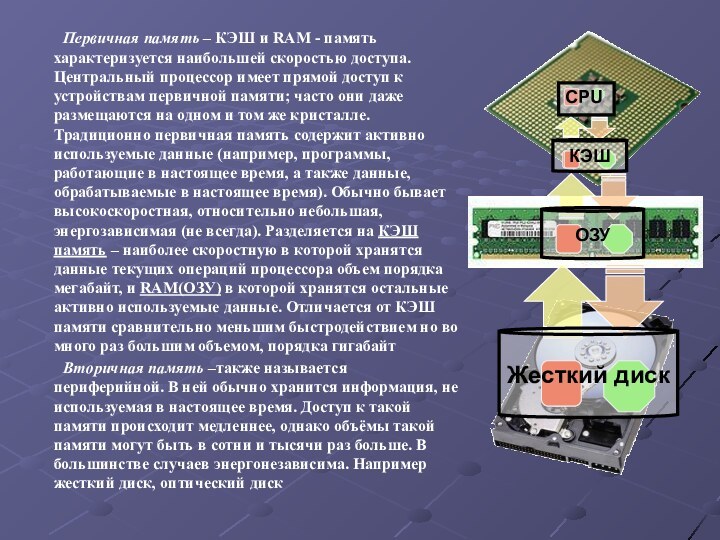

Первичная память – КЭШ и RAM - память

характеризуется наибольшей скоростью доступа. Центральный процессор имеет прямой доступ

к устройствам первичной памяти; часто они даже размещаются на одном и том же кристалле. Традиционно первичная память содержит активно используемые данные (например, программы, работающие в настоящее время, а также данные, обрабатываемые в настоящее время). Обычно бывает высокоскоростная, относительно небольшая, энергозависимая (не всегда). Разделяется на КЭШ память – наиболее скоростную в которой хранятся данные текущих операций процессора объем порядка мегабайт, и RAM(ОЗУ) в которой хранятся остальные активно используемые данные. Отличается от КЭШ памяти сравнительно меньшим быстродействием но во много раз большим объемом, порядка гигабайт

Вторичная память –также называется периферийной. В ней обычно хранится информация, не используемая в настоящее время. Доступ к такой памяти происходит медленнее, однако объёмы такой памяти могут быть в сотни и тысячи раз больше. В большинстве случаев энергонезависима. Например жесткий диск, оптический диск

ОЗУ

КЭШ

CPU

Жесткий диск

Слайд 5

Основные понятия

Быстродействие – время выполнения операции записи и

чтения данных

Производительность – скорость потока записываемых или считываемых данных

Разрядность

шины памяти – количество байт с которыми операция чтения или записи может быть выполнена одновременно

Банк памяти – комплект микросхем или модулей и их посадочных мест обеспечивающих разрядность хранения данных

Достоверность хранения данных

Для контроля достоверность хранимых в электронной памяти данных используются специальные средства:

Контроль четности (Parity bit);

ECC Memory – контроль и исправление ошибок. При использовании данного метода к 64 битному слову добавляется 7-8 бит. Настраивается система в CMOS Setup. Применяется, в частности, в кэш-памяти процессоров серии P6 и выше

Достоверность информации хранимой в ROM BIOS проверяется с помощью контрольной суммы (Cheksum) – обычно это байт дополняющий до нуля сумму по модулю 256 всех байт контролируемых данных. Проверка этой суммы выполняется во время теста POST

Слайд 6

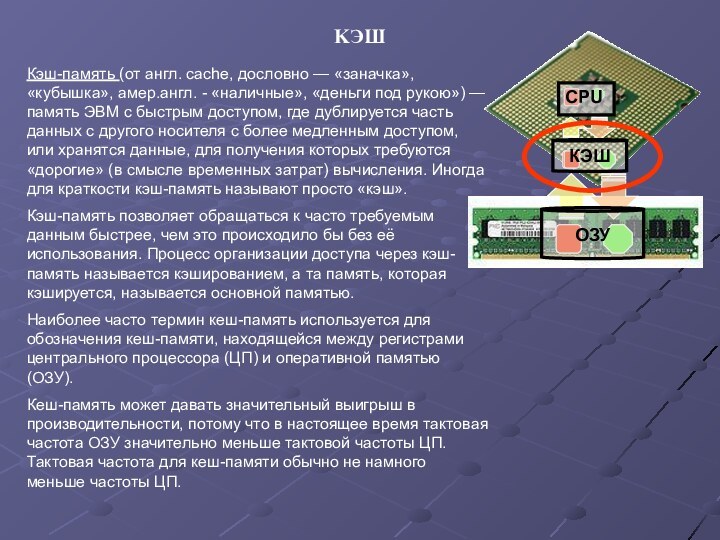

KЭШ

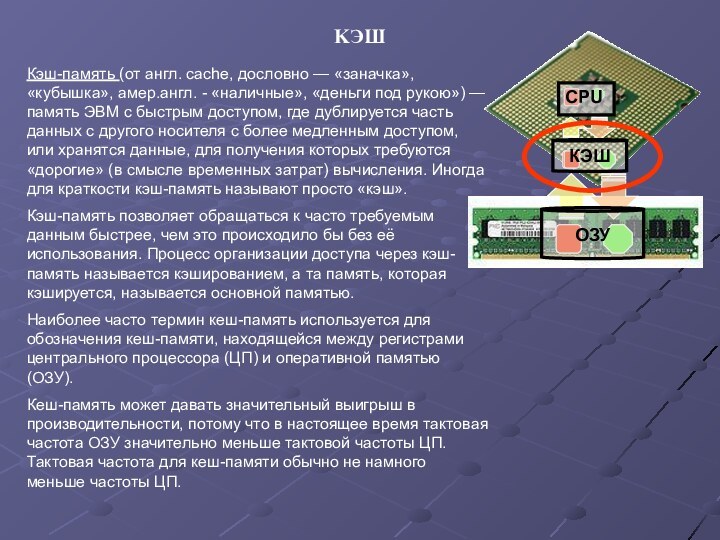

Кэш-память (от англ. cache, дословно — «заначка», «кубышка»,

амер.англ. - «наличные», «деньги под рукою») — память ЭВМ

с быстрым доступом, где дублируется часть данных с другого носителя с более медленным доступом, или хранятся данные, для получения которых требуются «дорогие» (в смысле временных затрат) вычисления. Иногда для краткости кэш-память называют просто «кэш».

Кэш-память позволяет обращаться к часто требуемым данным быстрее, чем это происходило бы без её использования. Процесс организации доступа через кэш-память называется кэшированием, а та память, которая кэшируется, называется основной памятью.

Наиболее часто термин кеш-память используется для обозначения кеш-памяти, находящейся между регистрами центрального процессора (ЦП) и оперативной памятью (ОЗУ).

Кеш-память может давать значительный выигрыш в производительности, потому что в настоящее время тактовая частота ОЗУ значительно меньше тактовой частоты ЦП. Тактовая частота для кеш-памяти обычно не намного меньше частоты ЦП.

ОЗУ

КЭШ

CPU

Слайд 7

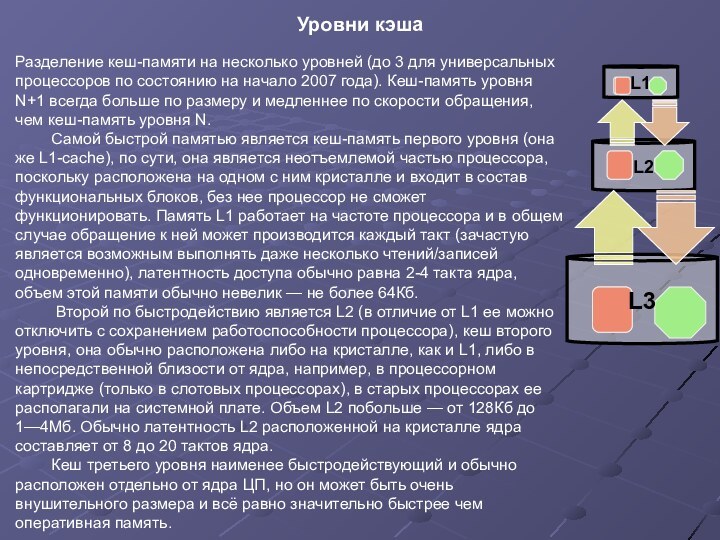

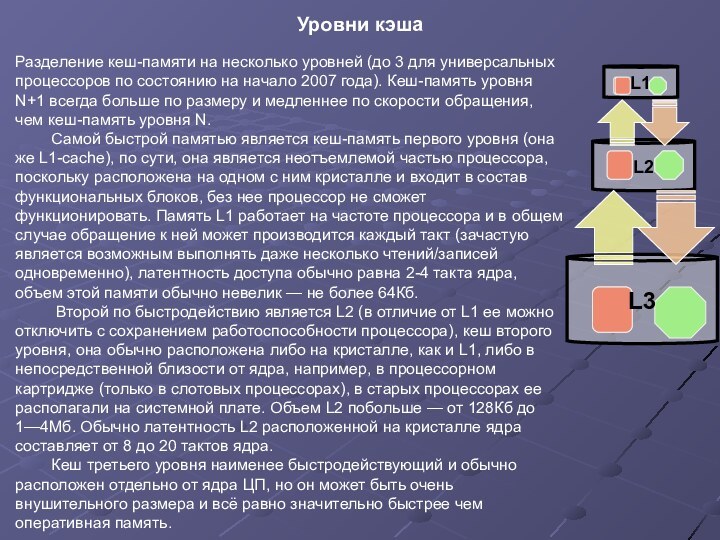

Разделение кеш-памяти на несколько уровней (до 3 для

универсальных процессоров по состоянию на начало 2007 года). Кеш-память

уровня N+1 всегда больше по размеру и медленнее по скорости обращения, чем кеш-память уровня N.

Самой быстрой памятью является кеш-память первого уровня (она же L1-cache), по сути, она является неотъемлемой частью процессора, поскольку расположена на одном с ним кристалле и входит в состав функциональных блоков, без нее процессор не сможет функционировать. Память L1 работает на частоте процессора и в общем случае обращение к ней может производится каждый такт (зачастую является возможным выполнять даже несколько чтений/записей одновременно), латентность доступа обычно равна 2-4 такта ядра, объем этой памяти обычно невелик — не более 64Кб.

Второй по быстродействию является L2 (в отличие от L1 ее можно отключить с сохранением работоспособности процессора), кеш второго уровня, она обычно расположена либо на кристалле, как и L1, либо в непосредственной близости от ядра, например, в процессорном картридже (только в слотовых процессорах), в старых процессорах ее располагали на системной плате. Объем L2 побольше — от 128Кб до 1—4Мб. Обычно латентность L2 расположенной на кристалле ядра составляет от 8 до 20 тактов ядра.

Кеш третьего уровня наименее быстродействующий и обычно расположен отдельно от ядра ЦП, но он может быть очень внушительного размера и всё равно значительно быстрее чем оперативная память.

Уровни кэша

L2

L3

L1

Слайд 8

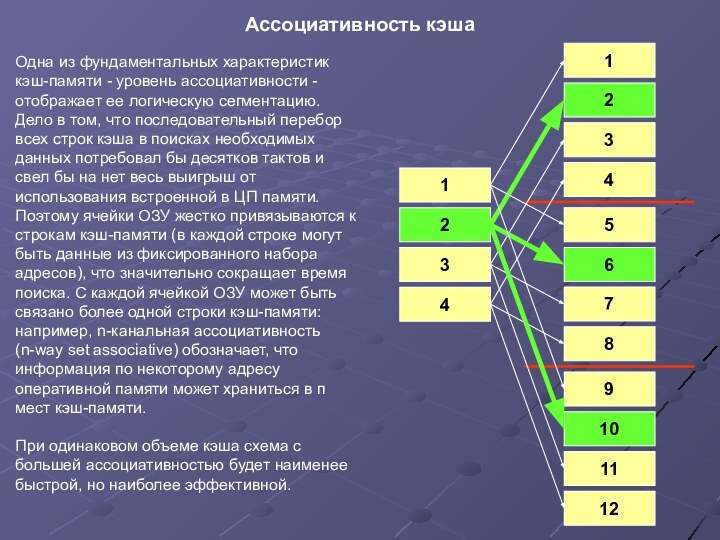

Одна из фундаментальных характеристик кэш-памяти - уровень ассоциативности

- отображает ее логическую сегментацию. Дело в том, что

последовательный перебор всех строк кэша в поисках необходимых данных потребовал бы десятков тактов и свел бы на нет весь выигрыш от использования встроенной в ЦП памяти. Поэтому ячейки ОЗУ жестко привязываются к строкам кэш-памяти (в каждой строке могут быть данные из фиксированного набора адресов), что значительно сокращает время поиска. С каждой ячейкой ОЗУ может быть связано более одной строки кэш-памяти: например, n-канальная ассоциативность (n-way set associative) обозначает, что информация по некоторому адресу оперативной памяти может храниться в п мест кэш-памяти.

При одинаковом объеме кэша схема с большей ассоциативностью будет наименее быстрой, но наиболее эффективной.

Ассоциативность кэша

1

2

3

4

1

2

3

4

5

6

7

8

9

10

11

12

Слайд 9

При чтении данных кеш-память даёт однозначный выигрыш в

производительности. При записи данных выигрыш можно получить только ценой

снижения надёжности. Поэтому в различных приложениях может быть выбрана та или иная политика записи кеш-памяти..

Существуют две основные политики записи кеш-памяти — сквозная запись (write-through) и отложенная запись (write-back).

сквозная запись подразумевает, что при изменении содержимого ячейки памяти, запись происходит синхронно и в кеш и в основную память.

отложенная запись подразумевает, что можно отложить момент записи данных в основную память, а записать их только в кеш. При этом данные будут выгружены в оперативную память только в случае обращения к ним какого либо другого устройства (другой ЦП контроллер DMA) либо нехватки места в кеше для размещения других данных. Производительность, по сравнению со сквозной записью, повышается, но это может поставить под угрозу целостность данных в основной памяти, поскольку программный или аппаратный сбой может привести к тому, что данные так и не будут переписаны из кеша в основную память. Кроме того, в случае кеширования оперативной памяти, когда используются два и более процессоров, нужно обеспечивать согласованность данных в разных кешах.

Политика записи при кешировании

Слайд 10

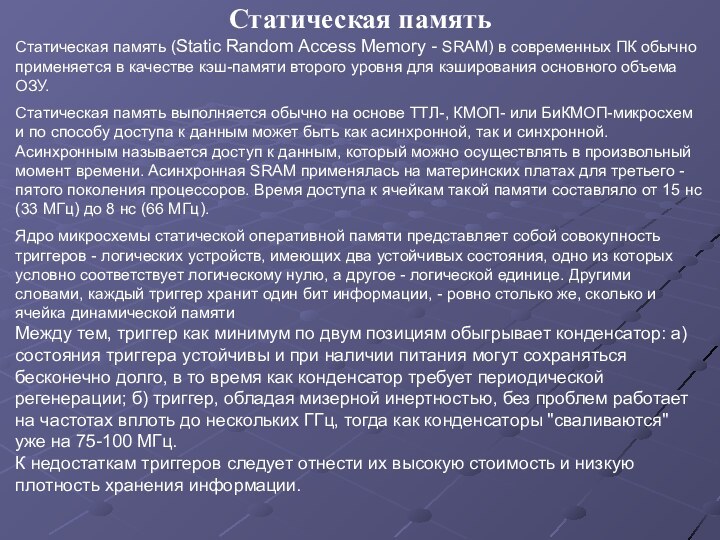

Статическая память

Статическая память (Static Random Access Memory -

SRAM) в современных ПК обычно применяется в качестве кэш-памяти

второго уровня для кэширования основного объема ОЗУ.

Статическая память выполняется обычно на основе ТТЛ-, КМОП- или БиКМОП-микросхем и по способу доступа к данным может быть как асинхронной, так и синхронной. Асинхронным называется доступ к данным, который можно осуществлять в произвольный момент времени. Асинхронная SRAM применялась на материнских платах для третьего - пятого поколения процессоров. Время доступа к ячейкам такой памяти составляло от 15 нс (33 МГц) до 8 нс (66 МГц).

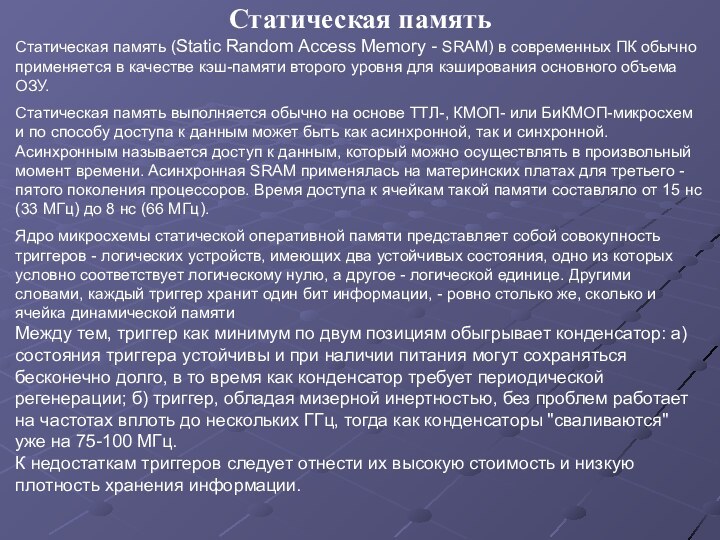

Ядро микросхемы статической оперативной памяти представляет собой совокупность триггеров - логических устройств, имеющих два устойчивых состояния, одно из которых условно соответствует логическому нулю, а другое - логической единице. Другими словами, каждый триггер хранит один бит информации, - ровно столько же, сколько и ячейка динамической памяти

Между тем, триггер как минимум по двум позициям обыгрывает конденсатор: а) состояния триггера устойчивы и при наличии питания могут сохраняться бесконечно долго, в то время как конденсатор требует периодической регенерации; б) триггер, обладая мизерной инертностью, без проблем работает на частотах вплоть до нескольких ГГц, тогда как конденсаторы "сваливаются" уже на 75-100 МГц.

К недостаткам триггеров следует отнести их высокую стоимость и низкую плотность хранения информации.

Слайд 11

Триггеры объединяются в единую матрицу, состоящую из строк

(row) и столбцов (column), последние из которых так же

называются битами (bit).

В отличии от ячейки динамической памяти, для управления которой достаточно всего одного ключевого транзистора, ячейка статической памяти управляется как минимум двумя. Это не покажется удивительным, если вспомнить, что триггер, в отличии от конденсатора, имеет раздельные входы для записи логического нуля и единицы соответственно. Таким образом, на ячейку статической памяти расходуется целых восемь транзисторов - четыре идут, собственно, на сам триггер и еще два - на управляющие "защелки".

Основной недостаток шести транзисторной ячейки заключается в том, что в каждый момент времени может обрабатываться всего лишь одна строка матрицы памяти. Параллельное чтение ячеек, расположенных в различных строках одного и того же банка невозможно, равно как невозможно и чтение одной ячейки одновременно с записью другой.

Слайд 12

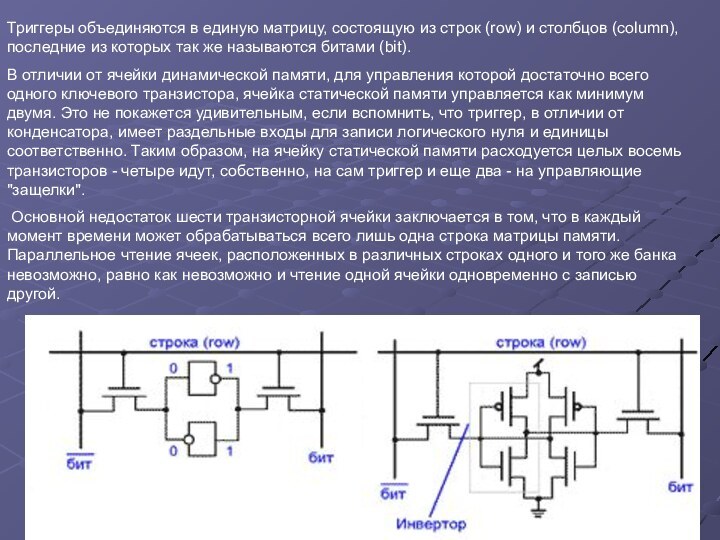

Этого ограничения лишена многопортовая память. Каждая ячейка многопортовой

памяти содержит один-единственный триггер, но имеет несколько комплектов управляющих

транзисторов, каждый из которых подключен к "своим" линиям ROW и BIT, благодаря чему различные ячейки матрицы могут обрабатываться независимо. Такой подход намного более прогрессивен, чем деление памяти на банки. Ведь, в последнем случае параллелизм достигается лишь при обращении к ячейкам различных банков, что не всегда выполнимо, а много портовая память допускает одновременную обработку любых ячеек, избавляя программиста от необходимости вникать в особенности ее архитектуры.

Наиболее часто встречается двух - портовая память, Нетрудно подсчитать, что для создания одной ячейки двух - портовой памяти расходуется аж восемь транзисторов. Пусть емкость кэш-памяти составляет 32 Кб, тогда только на одно ядро уйдет свыше двух миллионов транзисторов.

Слайд 13

Типы SRAM

Асинхронная статическая память работает независимо от контроллера

и потому, контроллер не может быть уверен, что окончание

цикла обмена совпадет с началом очередного тактового импульса. В результате, цикл обмена удлиняется по крайней мере на один такт, снижая тем самым эффективную производительность. "Благодаря" последнему обстоятельству, в настоящее время асинхронная память практически нигде не применяется (последними компьютерами, на которых она еще использовались в качестве кэша второго уровня, стали машины, построенные на базе процессора Intel 80386).

Асинхронная статическая память

Синхронная статическая память выполняет все операции одновременно с тактовыми сигналами, в результате чего время доступа к ячейке укладывается в один-единственный такт. Именно на синхронной статической памяти реализуется кэш первого уровня современных процессоров.

Синхронная статическая память

Конвейерная статическая память представляет собой синхронную статическую память, оснащенную специальными "защелками", удерживающими линии данных, что позволяет читать (записывать) содержимое одной ячейки параллельно с передачей адреса другой.

Так же, конвейерная память может обрабатывать несколько смежных ячеек за один рабочий цикл.

За счет большей аппаратной сложности конвейерной памяти, время доступа к первой ячейке пакета увеличивается на один такт, однако, это практически не снижает производительности/

Конвейерная статическая память используется в частности в кэше второго уровня микропроцессоров Pentium-II и ее формула выглядит так: 2 - 1 - 1 - 1.

Конвейерная статическая память

Слайд 14

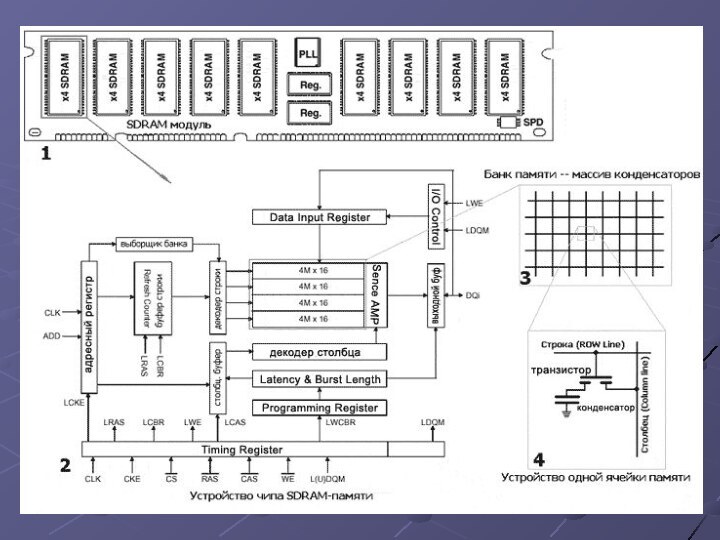

Динамическая память

DRAM (Dynamic Random Access Memory) — один

из видов компьютерной памяти с произвольным доступом (RAM), наиболее

широко используемый в качестве ОЗУ современных компьютеров.

Конструктивно память DRAM состоит из «ячеек» размером в 1 или 4 бит, в каждой из которых можно хранить определённый объём данных. Совокупность «ячеек» такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор «ячеек» условно делится на несколько областей.

В современных компьютерах физически память представляет собой электрическую плату — модуль, на котором расположены микросхемы памяти и разъём, необходимый для подключения модуля к материнской плате. Роль «ячеек» играют конденсаторы и транзисторы, расположенные внутри микросхем памяти. Конденсаторы заряжаются в случае, когда в «ячейку» заносится единичный бит, либо разряжаются в случае, когда в «ячейку» заносится нулевой бит. Транзисторы необходимы для удержания заряда внутри конденсатора. При отсутствии подачи электроэнергии к оперативной памяти, происходит разряжение конденсаторов, и память опустошается. Это динамическое изменение заряда конденсатора является основополагающим принципом работы памяти типа DRAM. Элементом памяти типа DRAM является чувствительный усилитель (англ. sense amp), подключенный к каждому из столбцов «прямоугольника». Он, реагируя на слабый поток электронов, устремившихся через открытые транзисторы с обкладок конденсаторов, считывает всю страницу целиком. Именно страница является минимальной порцией обмена с динамической памятью, потому что обмен данными с отдельно взятой ячейкой невозможен.

Слайд 16

Регенерация DRAM

Независимо от того, какова конкретная модификация динамической

памяти, запоминающие конденсаторы ее запоминающих элементов разряжаются из-за наличия

токов утечки. Постоянная разряда, как известно, зависит от емкости запоминающего конденсатора и сопротивления цепи тока утечки и может различаться для разных модификаций. Время, в течение которого информация сохраняется в элементе памяти, составляет до нескольких десятков миллисекунд.

Это приводит к необходимости периодического (с периодом не больше, чем время сохранения информации) восстановления зарядов емкостей. Такая процедура и получила название регенерации (refresh) динамической памяти. Выполняется она одновременно для целой строки матрицы (банка) элементов памяти, поскольку регенерировать информацию по элементам или по словам (по 8 байт) слишком долго.

Действительно, если даже считать, что регенерация выполняется одним длинным пакетным циклом, то для микросхем памяти PС2700, в которых на одну передачу данных приходится 3 нс (165 МГц × 2), при емкости 256 Мбит на поэлементную регенерацию всех элементов потребуется 3 × 10-9 × 228 = 0,8 с, а на регенерацию по словам, точнее, ячейкам, разрядность которых не может быть выше разрядности микросхемы (как правило, не более 16 бит), потребуется в 16 раз меньше времени, т.е. 50 мс. Учитывая, что для таких микросхем максимальный период регенерации TREF = 64 мс, поэлементная регенерация оказывается принципиально невозможной, а регенерация по словам будет занимать более 75 % времени работы памяти.

Количество же строк в одном банке в данной микросхеме составит 8192, а построчная регенерация в таком случае будет занимать всего 24,5 мкс или около 0,5 % времени.

Слайд 17

Распределить циклы регенерации строк по полному периоду регенерации

можно различными способами. Рассмотренный выше вариант пакетной регенерации, при

котором все циклы регенерации строк группируются в начале или в конце периода, хотя и может быть более экономичным по времени из-за отсутствия дополнительных переключений, не является достаточно удобным, так как блокирует работу памяти на относительно длительный интервал времени. Поэтому чаще применяют так называемую распределенную регенерацию (иногда используется термин “синхронная”), при которой циклы регенерации строк равномерно распределяются по периоду.

Длительность периода регенерации не обязательно устанавливается равной максимальному значению. Например, в ряде ПЭВМ для управления регенерацией часто используют сигналы одного из счетчиков (счетчик 1) системного таймера, на который поступают сигналы от кварцевого генератора (частотой 14.31818 МГц), установленного на системной плате. Этот счетчик вырабатывает импульсы примерно каждые 15 мкс, и эти импульсы могут использоваться для запуска регенерации. Однако для памяти большого объема такая частота оказывается недостаточной.

Возможны и более сложные схемы регенерации: пакетная с возможностью прерывания пакета или скрытая – во время свободных циклов памяти, если таковые имеются.

За последовательностью циклов регенерации строк следит контроллер памяти, который может организовывать очередь из этих циклов. Этот же контроллер может формировать адреса строк для регенерации, но часто эти адреса формируются внутренним счетчиком, имеющимся в самой микросхеме динамической памяти. Известна также квазистатическая память, в которой регенерация полностью контролируется внутренней логикой микросхемы и не требует никаких внешних сигналов.

Собственно циклы регенерации также могут различаться по порядку выполнения и запускающим их управляющим сигналам.

Слайд 18

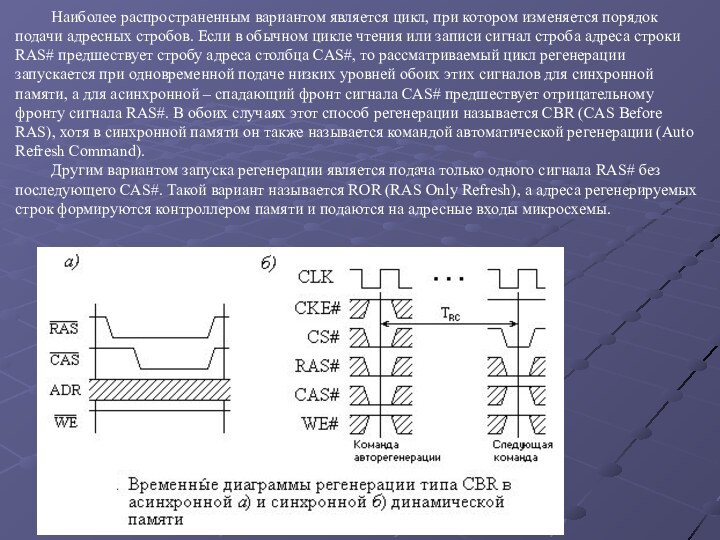

Наиболее распространенным вариантом является цикл, при котором изменяется

порядок подачи адресных стробов. Если в обычном цикле чтения

или записи сигнал строба адреса строки RAS# предшествует стробу адреса столбца CAS#, то рассматриваемый цикл регенерации запускается при одновременной подаче низких уровней обоих этих сигналов для синхронной памяти, а для асинхронной – спадающий фронт сигнала CAS# предшествует отрицательному фронту сигнала RAS#. В обоих случаях этот способ регенерации называется CBR (CAS Before RAS), хотя в синхронной памяти он также называется командой автоматической регенерации (Auto Refresh Command).

Другим вариантом запуска регенерации является подача только одного сигнала RAS# без последующего CAS#. Такой вариант называется ROR (RAS Only Refresh), а адреса регенерируемых строк формируются контроллером памяти и подаются на адресные входы микросхемы.

Слайд 19

Функционирование DRAM

В спокойном состоянии на обоих выводах поддерживается

высокий уровень сигнала,

При попытке прочесть содержимое некоторой ячейки

памяти:

Контроллер преобразует физический адрес в пару чисел - номер строки и номер столбца, а затем посылает первый из них на адресные линии.

Дождавшись, когда сигнал стабилизируется, контроллер сбрасывает сигнал RAS в низкий уровень, сообщая микросхеме памяти о наличии информации на линии.

Микросхема считывает этот адрес и подает на соответствующую строку матрицы электрический сигнал. Все транзисторы, подключенные к этой строке, открываются и конденсатор разряжается на входы чувствительного усилителя.

Чувствительный усилитель декодирует всю строку, преобразуя ее в последовательность нулей и единиц, и сохраняет полученную информацию в специальном буфере. Все это (в зависимости от конструктивных особенностей и качества изготовления микросхемы) занимает от двадцати до сотни наносекунд, в течение которых контроллер памяти выдерживает терпеливую паузу.

Наконец, когда микросхема завершает чтение строки и вновь готова к приему информации, контроллер подает на адресные линии номер колонки и, дав сигналу стабилизироваться, сбрасывает CAS в низкое состояние.

Микросхема номер колонки в смещение ячейки внутри буфера. Остается всего лишь прочесть ее содержимое и выдать его на линии данных. Это занимает еще какое-то время, в течение которого контроллер ждет запрошенную информацию.

На финальной стадии цикла обмена контроллер считывает состояние линий данных, дезактивирует сигналы RAS и CAS, устанавливая их в высокое состояние, а микросхема берет определенный тайм-аут на перезарядку внутренних цепей и восстановительную перезапись строки.

Задержка между подачей номера строки и номера столбца на техническом жаргоне называется "RAS to CAS delay" (на сухом официальном языке - tRCD). Задержка между подачей номера столбца и получением содержимого ячейки на выходе - "CAS delay" (или tCAC), а задержка между чтением последней ячейки и подачей номера новой строки - "RAS precharge" (tRP).

Основными характеристиками DRAM являются тайминги и рабочая частота.

Для обращения к ячейке, контроллер задаёт номер банка, номер страницы в нём, номер строки и номер столбца, на все запросы тратится время, помимо этого довольно большая затрата уходит на открытие и закрытие банка после самой операции. На каждое действие требуется время, называемое таймингом.

Основными таймингами DRAM являются:

задержка между подачей номера строки и номера столбца, называемая временем полного доступа (англ. RAS to CAS delay),

задержка между подачей номера столбца и получением содержимого ячейки, называемая временем рабочего цикла (англ. CAS delay),

задержка между чтением последней ячейки и подачей номера новой строки (англ. RAS precharge).

Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память. Рабочая частота измеряется в мегагерцах, и увеличение рабочей частоты памяти приводит к увеличению её быстродействия.

Слайд 20

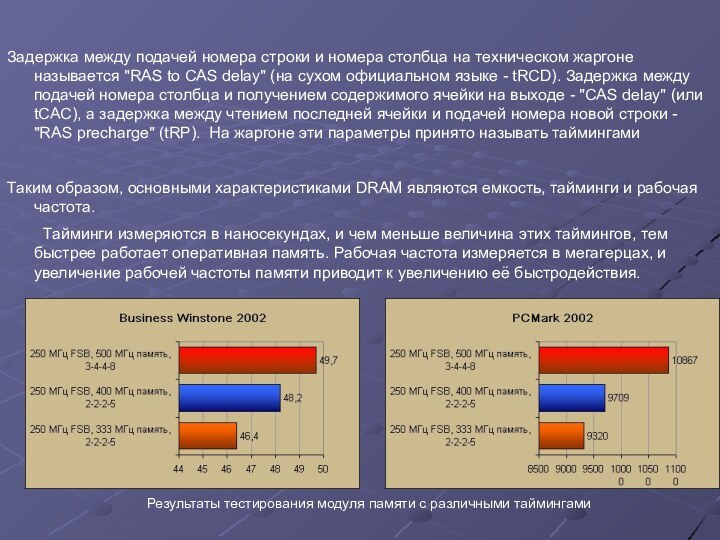

Задержка между подачей номера строки и номера столбца

на техническом жаргоне называется "RAS to CAS delay" (на

сухом официальном языке - tRCD). Задержка между подачей номера столбца и получением содержимого ячейки на выходе - "CAS delay" (или tCAC), а задержка между чтением последней ячейки и подачей номера новой строки - "RAS precharge" (tRP). На жаргоне эти параметры принято называть таймингами

Таким образом, основными характеристиками DRAM являются емкость, тайминги и рабочая частота.

Тайминги измеряются в наносекундах, и чем меньше величина этих таймингов, тем быстрее работает оперативная память. Рабочая частота измеряется в мегагерцах, и увеличение рабочей частоты памяти приводит к увеличению её быстродействия.

Результаты тестирования модуля памяти с различными таймингами

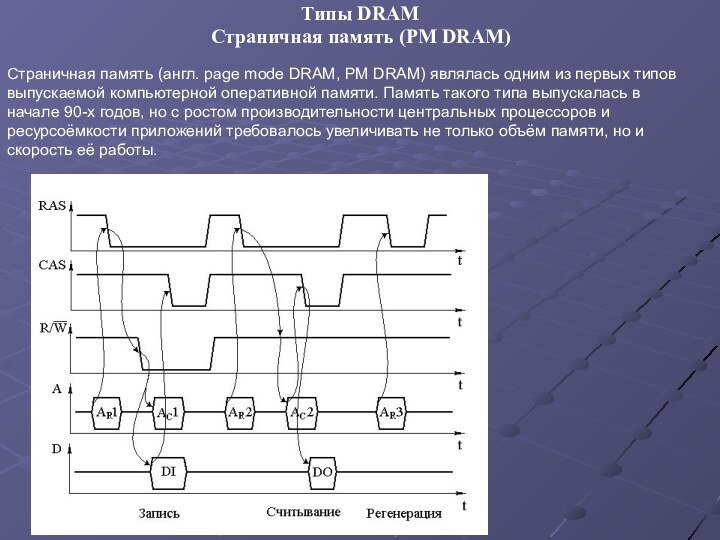

Слайд 21

Типы DRAM

Страничная память (англ. page mode DRAM, PM

DRAM) являлась одним из первых типов выпускаемой компьютерной оперативной

памяти. Память такого типа выпускалась в начале 90-х годов, но с ростом производительности центральных процессоров и ресурсоёмкости приложений требовалось увеличивать не только объём памяти, но и скорость её работы.

Страничная память (PM DRAM)

Слайд 22

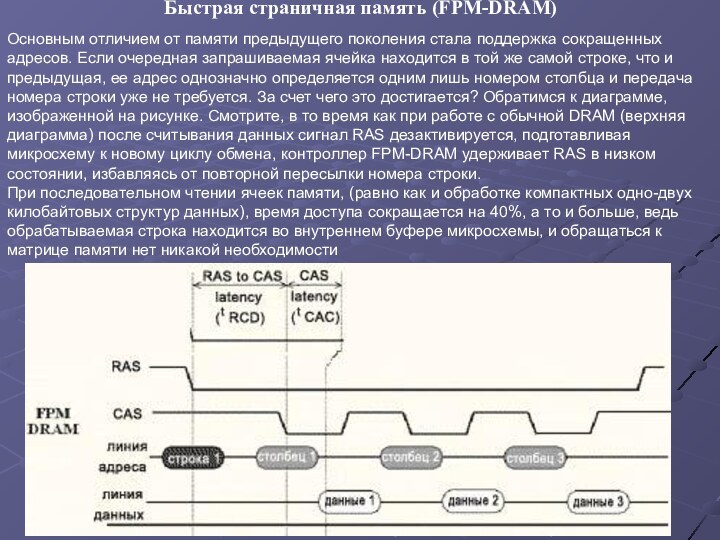

Основным отличием от памяти предыдущего поколения стала поддержка

сокращенных адресов. Если очередная запрашиваемая ячейка находится в той

же самой строке, что и предыдущая, ее адрес однозначно определяется одним лишь номером столбца и передача номера строки уже не требуется. За счет чего это достигается? Обратимся к диаграмме, изображенной на рисунке. Смотрите, в то время как при работе с обычной DRAM (верхняя диаграмма) после считывания данных сигнал RAS дезактивируется, подготавливая микросхему к новому циклу обмена, контроллер FPM-DRAM удерживает RAS в низком состоянии, избавляясь от повторной пересылки номера строки.

При последовательном чтении ячеек памяти, (равно как и обработке компактных одно-двух килобайтовых структур данных), время доступа сокращается на 40%, а то и больше, ведь обрабатываемая строка находится во внутреннем буфере микросхемы, и обращаться к матрице памяти нет никакой необходимости

Быстрая страничная память (FPM-DRAM)

Слайд 23

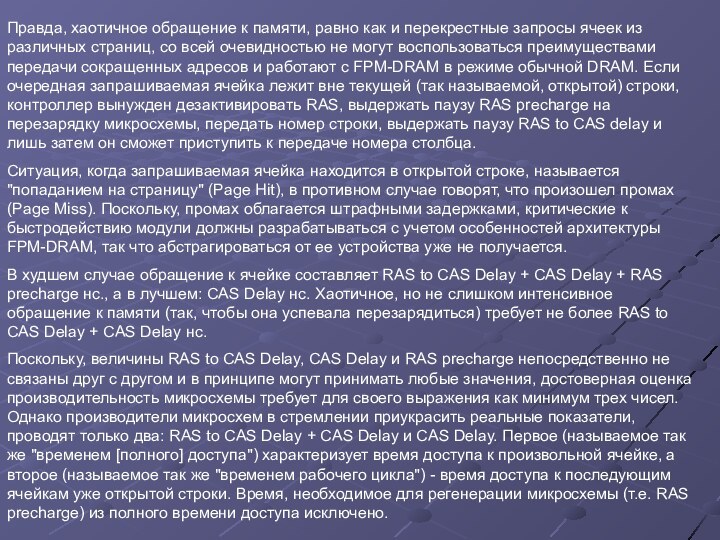

Правда, хаотичное обращение к памяти, равно как и

перекрестные запросы ячеек из различных страниц, со всей очевидностью

не могут воспользоваться преимуществами передачи сокращенных адресов и работают с FPM-DRAM в режиме обычной DRAM. Если очередная запрашиваемая ячейка лежит вне текущей (так называемой, открытой) строки, контроллер вынужден дезактивировать RAS, выдержать паузу RAS precharge на перезарядку микросхемы, передать номер строки, выдержать паузу RAS to CAS delay и лишь затем он сможет приступить к передаче номера столбца.

Ситуация, когда запрашиваемая ячейка находится в открытой строке, называется "попаданием на страницу" (Page Hit), в противном случае говорят, что произошел промах (Page Miss). Поскольку, промах облагается штрафными задержками, критические к быстродействию модули должны разрабатываться с учетом особенностей архитектуры FPM-DRAM, так что абстрагироваться от ее устройства уже не получается.

В худшем случае обращение к ячейке составляет RAS to CAS Delay + CAS Delay + RAS precharge нс., а в лучшем: CAS Delay нс. Хаотичное, но не слишком интенсивное обращение к памяти (так, чтобы она успевала перезарядиться) требует не более RAS to CAS Delay + CAS Delay нс.

Поскольку, величины RAS to CAS Delay, CAS Delay и RAS precharge непосредственно не связаны друг с другом и в принципе могут принимать любые значения, достоверная оценка производительность микросхемы требует для своего выражения как минимум трех чисел. Однако производители микросхем в стремлении приукрасить реальные показатели, проводят только два: RAS to CAS Delay + CAS Delay и CAS Delay. Первое (называемое так же "временем [полного] доступа") характеризует время доступа к произвольной ячейке, а второе (называемое так же "временем рабочего цикла") - время доступа к последующим ячейкам уже открытой строки. Время, необходимое для регенерации микросхемы (т.е. RAS precharge) из полного времени доступа исключено.

Слайд 24

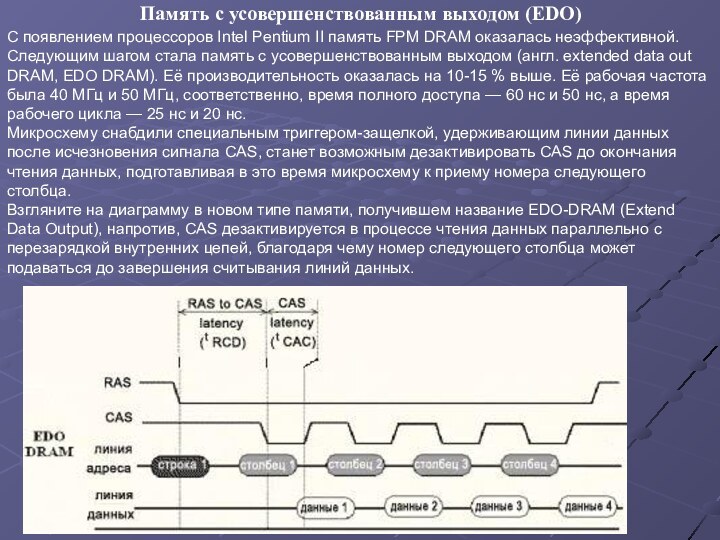

С появлением процессоров Intel Pentium II память FPM

DRAM оказалась неэффективной. Следующим шагом стала память с усовершенствованным

выходом (англ. extended data out DRAM, EDO DRAM). Её производительность оказалась на 10-15 % выше. Её рабочая частота была 40 МГц и 50 МГц, соответственно, время полного доступа — 60 нс и 50 нс, а время рабочего цикла — 25 нс и 20 нс.

Микросхему снабдили специальным триггером-защелкой, удерживающим линии данных после исчезновения сигнала CAS, станет возможным дезактивировать CAS до окончания чтения данных, подготавливая в это время микросхему к приему номера следующего столбца.

Взгляните на диаграмму в новом типе памяти, получившем название EDO-DRAM (Extend Data Output), напротив, CAS дезактивируется в процессе чтения данных параллельно с перезарядкой внутренних цепей, благодаря чему номер следующего столбца может подаваться до завершения считывания линий данных.

Память с усовершенствованным выходом (EDO)

Слайд 25

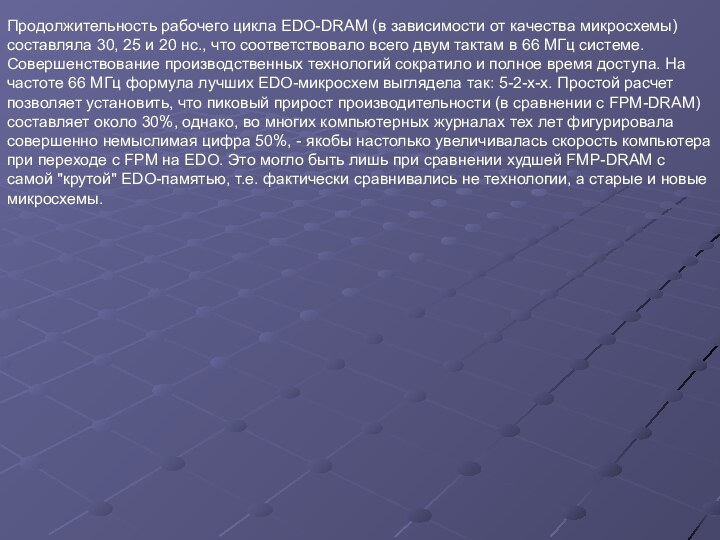

Продолжительность рабочего цикла EDO-DRAM (в зависимости от качества

микросхемы) составляла 30, 25 и 20 нс., что соответствовало

всего двум тактам в 66 МГц системе. Совершенствование производственных технологий сократило и полное время доступа. На частоте 66 МГц формула лучших EDO-микросхем выглядела так: 5-2-x-x. Простой расчет позволяет установить, что пиковый прирост производительности (в сравнении с FPM-DRAM) составляет около 30%, однако, во многих компьютерных журналах тех лет фигурировала совершенно немыслимая цифра 50%, - якобы настолько увеличивалась скорость компьютера при переходе с FPM на EDO. Это могло быть лишь при сравнении худшей FMP-DRAM с самой "крутой" EDO-памятью, т.е. фактически сравнивались не технологии, а старые и новые микросхемы.

Слайд 26

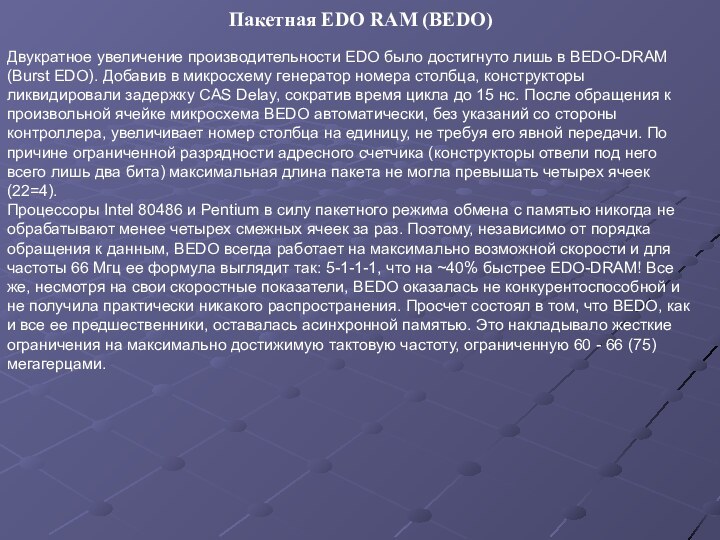

Двукратное увеличение производительности EDO было достигнуто лишь в

BEDO-DRAM (Burst EDO). Добавив в микросхему генератор номера столбца,

конструкторы ликвидировали задержку CAS Delay, сократив время цикла до 15 нс. После обращения к произвольной ячейке микросхема BEDO автоматически, без указаний со стороны контроллера, увеличивает номер столбца на единицу, не требуя его явной передачи. По причине ограниченной разрядности адресного счетчика (конструкторы отвели под него всего лишь два бита) максимальная длина пакета не могла превышать четырех ячеек (22=4).

Процессоры Intel 80486 и Pentium в силу пакетного режима обмена с памятью никогда не обрабатывают менее четырех смежных ячеек за раз. Поэтому, независимо от порядка обращения к данным, BEDO всегда работает на максимально возможной скорости и для частоты 66 Мгц ее формула выглядит так: 5-1-1-1, что на ~40% быстрее EDO-DRAM! Все же, несмотря на свои скоростные показатели, BEDO оказалась не конкурентоспособной и не получила практически никакого распространения. Просчет состоял в том, что BEDO, как и все ее предшественники, оставалась асинхронной памятью. Это накладывало жесткие ограничения на максимально достижимую тактовую частоту, ограниченную 60 - 66 (75) мегагерцами.

Пакетная EDO RAM (BEDO)

Слайд 27

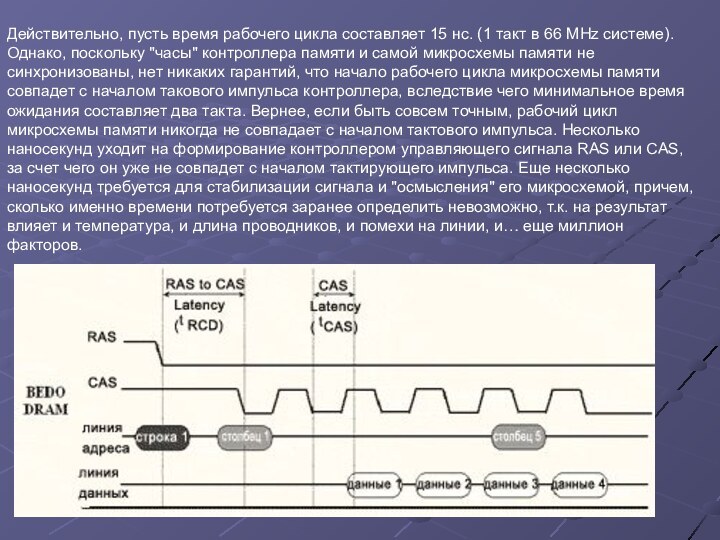

Действительно, пусть время рабочего цикла составляет 15 нс.

(1 такт в 66 MHz системе). Однако, поскольку "часы"

контроллера памяти и самой микросхемы памяти не синхронизованы, нет никаких гарантий, что начало рабочего цикла микросхемы памяти совпадет с началом такового импульса контроллера, вследствие чего минимальное время ожидания составляет два такта. Вернее, если быть совсем точным, рабочий цикл микросхемы памяти никогда не совпадает с началом тактового импульса. Несколько наносекунд уходит на формирование контроллером управляющего сигнала RAS или CAS, за счет чего он уже не совпадет с началом тактирующего импульса. Еще несколько наносекунд требуется для стабилизации сигнала и "осмысления" его микросхемой, причем, сколько именно времени потребуется заранее определить невозможно, т.к. на результат влияет и температура, и длина проводников, и помехи на линии, и… еще миллион факторов.

Слайд 28

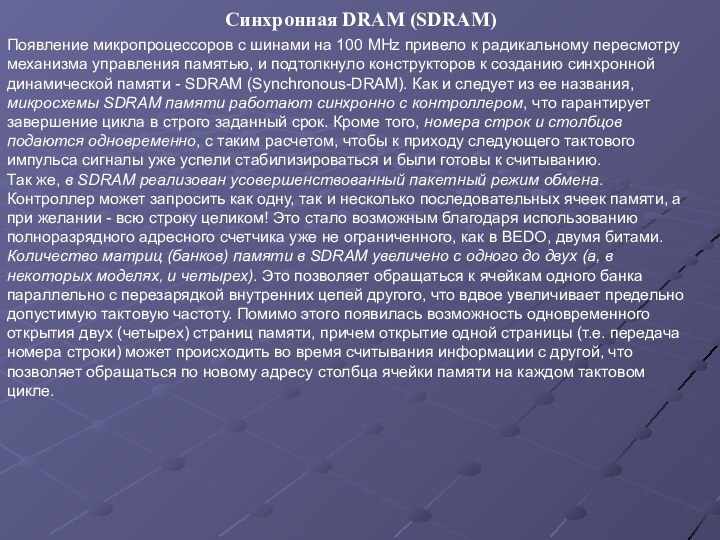

Появление микропроцессоров с шинами на 100 MHz привело

к радикальному пересмотру механизма управления памятью, и подтолкнуло конструкторов

к созданию синхронной динамической памяти - SDRAM (Synchronous-DRAM). Как и следует из ее названия, микросхемы SDRAM памяти работают синхронно с контроллером, что гарантирует завершение цикла в строго заданный срок. Кроме того, номера строк и столбцов подаются одновременно, с таким расчетом, чтобы к приходу следующего тактового импульса сигналы уже успели стабилизироваться и были готовы к считыванию.

Так же, в SDRAM реализован усовершенствованный пакетный режим обмена. Контроллер может запросить как одну, так и несколько последовательных ячеек памяти, а при желании - всю строку целиком! Это стало возможным благодаря использованию полноразрядного адресного счетчика уже не ограниченного, как в BEDO, двумя битами.

Количество матриц (банков) памяти в SDRAM увеличено с одного до двух (а, в некоторых моделях, и четырех). Это позволяет обращаться к ячейкам одного банка параллельно с перезарядкой внутренних цепей другого, что вдвое увеличивает предельно допустимую тактовую частоту. Помимо этого появилась возможность одновременного открытия двух (четырех) страниц памяти, причем открытие одной страницы (т.е. передача номера строки) может происходить во время считывания информации с другой, что позволяет обращаться по новому адресу столбца ячейки памяти на каждом тактовом цикле.

Синхронная DRAM (SDRAM)

Слайд 29

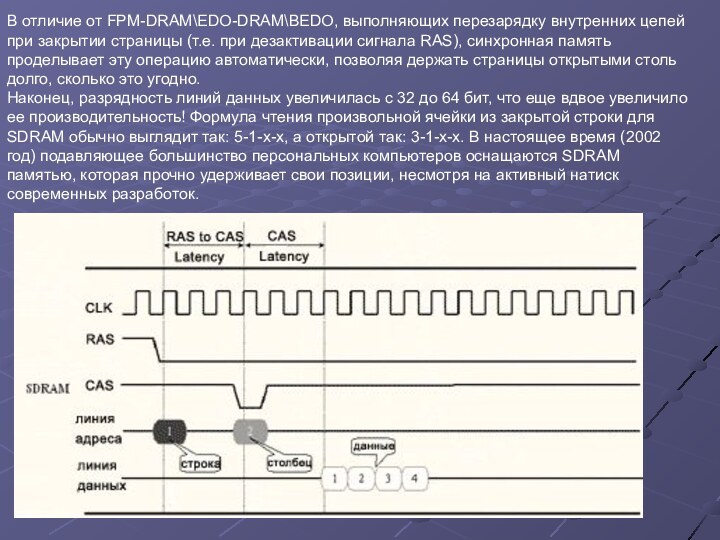

В отличие от FPM-DRAM\EDO-DRAM\BEDO, выполняющих перезарядку внутренних цепей

при закрытии страницы (т.е. при дезактивации сигнала RAS), синхронная

память проделывает эту операцию автоматически, позволяя держать страницы открытыми столь долго, сколько это угодно.

Наконец, разрядность линий данных увеличилась с 32 до 64 бит, что еще вдвое увеличило ее производительность! Формула чтения произвольной ячейки из закрытой строки для SDRAM обычно выглядит так: 5-1-x-x, а открытой так: 3-1-х-х. В настоящее время (2002 год) подавляющее большинство персональных компьютеров оснащаются SDRAM памятью, которая прочно удерживает свои позиции, несмотря на активный натиск современных разработок.

Слайд 30

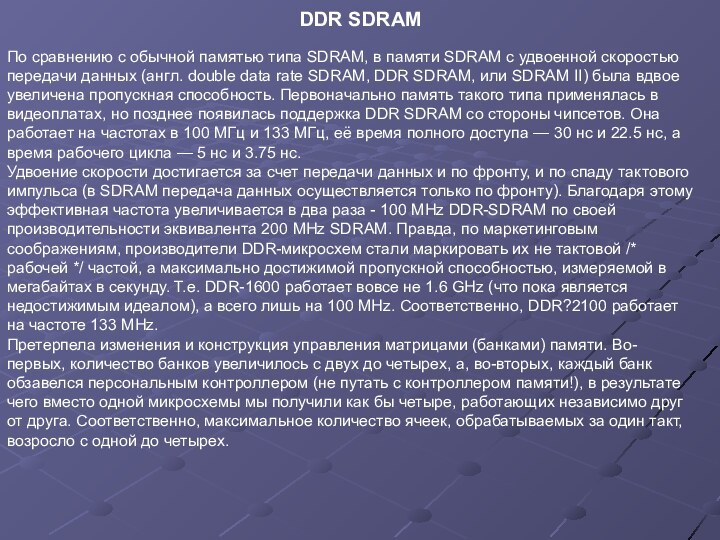

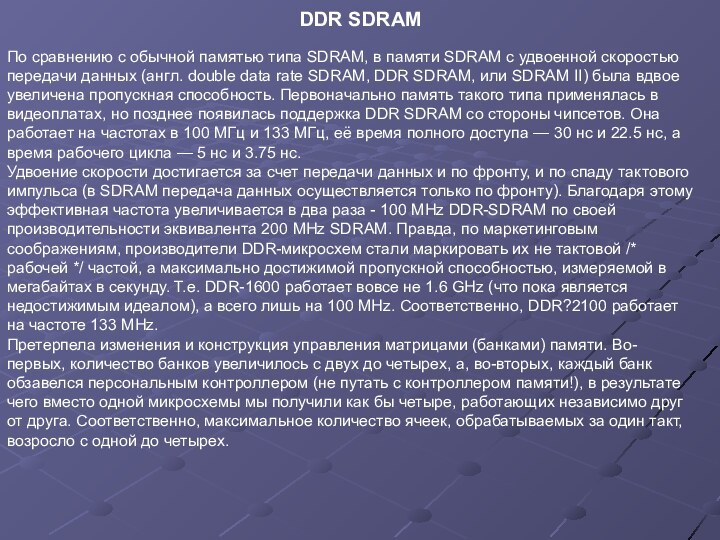

По сравнению с обычной памятью типа SDRAM, в

памяти SDRAM с удвоенной скоростью передачи данных (англ. double

data rate SDRAM, DDR SDRAM, или SDRAM II) была вдвое увеличена пропускная способность. Первоначально память такого типа применялась в видеоплатах, но позднее появилась поддержка DDR SDRAM со стороны чипсетов. Она работает на частотах в 100 МГц и 133 МГц, её время полного доступа — 30 нс и 22.5 нс, а время рабочего цикла — 5 нс и 3.75 нс.

Удвоение скорости достигается за счет передачи данных и по фронту, и по спаду тактового импульса (в SDRAM передача данных осуществляется только по фронту). Благодаря этому эффективная частота увеличивается в два раза - 100 MHz DDR-SDRAM по своей производительности эквивалента 200 MHz SDRAM. Правда, по маркетинговым соображениям, производители DDR-микросхем стали маркировать их не тактовой /* рабочей */ частой, а максимально достижимой пропускной способностью, измеряемой в мегабайтах в секунду. Т.е. DDR-1600 работает вовсе не 1.6 GHz (что пока является недостижимым идеалом), а всего лишь на 100 MHz. Соответственно, DDR?2100 работает на частоте 133 MHz.

Претерпела изменения и конструкция управления матрицами (банками) памяти. Во-первых, количество банков увеличилось с двух до четырех, а, во-вторых, каждый банк обзавелся персональным контроллером (не путать с контроллером памяти!), в результате чего вместо одной микросхемы мы получили как бы четыре, работающих независимо друг от друга. Соответственно, максимальное количество ячеек, обрабатываемых за один такт, возросло с одной до четырех.

DDR SDRAM

Слайд 31

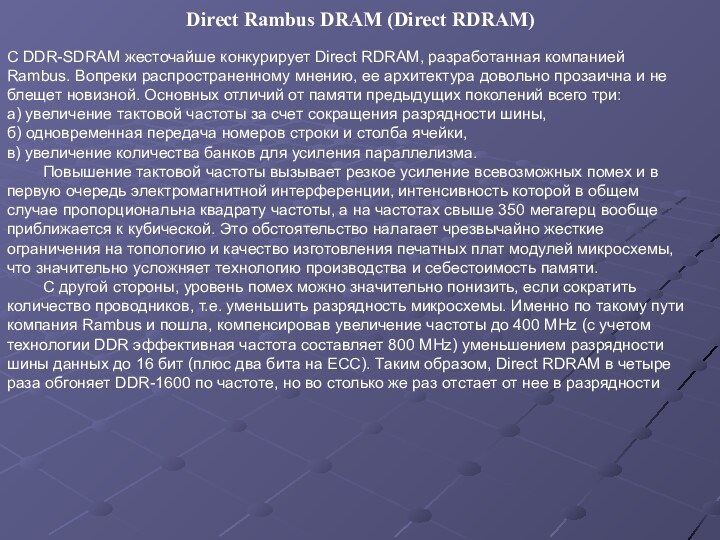

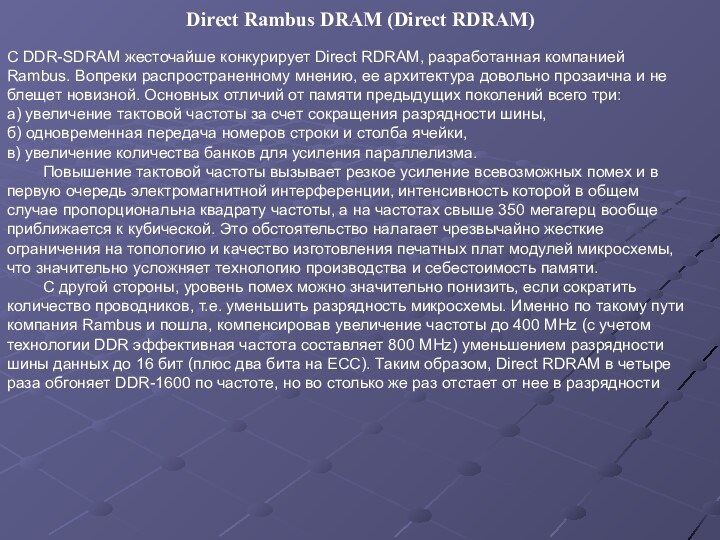

С DDR-SDRAM жесточайше конкурирует Direct RDRAM, разработанная компанией

Rambus. Вопреки распространенному мнению, ее архитектура довольно прозаична и

не блещет новизной. Основных отличий от памяти предыдущих поколений всего три:

а) увеличение тактовой частоты за счет сокращения разрядности шины,

б) одновременная передача номеров строки и столба ячейки,

в) увеличение количества банков для усиления параллелизма.

Повышение тактовой частоты вызывает резкое усиление всевозможных помех и в первую очередь электромагнитной интерференции, интенсивность которой в общем случае пропорциональна квадрату частоты, а на частотах свыше 350 мегагерц вообще приближается к кубической. Это обстоятельство налагает чрезвычайно жесткие ограничения на топологию и качество изготовления печатных плат модулей микросхемы, что значительно усложняет технологию производства и себестоимость памяти.

С другой стороны, уровень помех можно значительно понизить, если сократить количество проводников, т.е. уменьшить разрядность микросхемы. Именно по такому пути компания Rambus и пошла, компенсировав увеличение частоты до 400 MHz (с учетом технологии DDR эффективная частота составляет 800 MHz) уменьшением разрядности шины данных до 16 бит (плюс два бита на ECC). Таким образом, Direct RDRAM в четыре раза обгоняет DDR-1600 по частоте, но во столько же раз отстает от нее в разрядности

Direct Rambus DRAM (Direct RDRAM)

Слайд 32

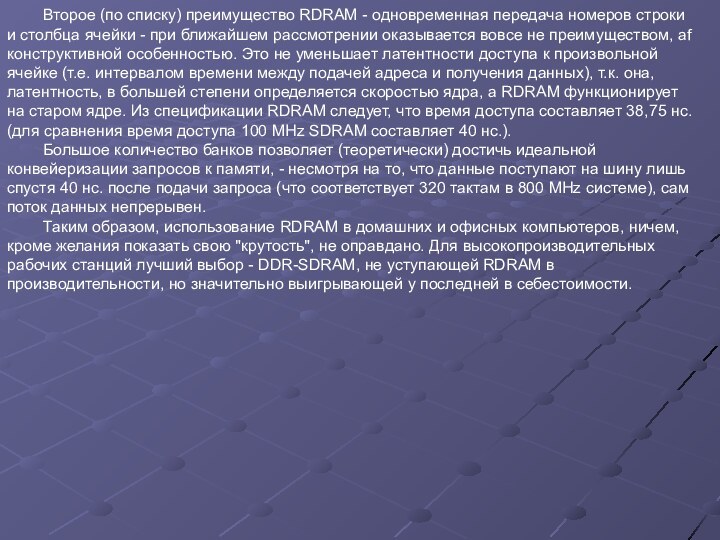

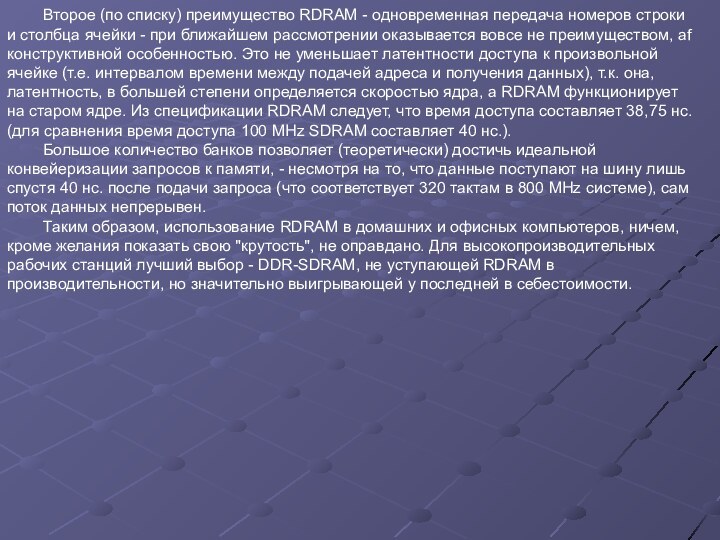

Второе (по списку) преимущество RDRAM - одновременная передача

номеров строки и столбца ячейки - при ближайшем рассмотрении

оказывается вовсе не преимуществом, аf конструктивной особенностью. Это не уменьшает латентности доступа к произвольной ячейке (т.е. интервалом времени между подачей адреса и получения данных), т.к. она, латентность, в большей степени определяется скоростью ядра, а RDRAM функционирует на старом ядре. Из спецификации RDRAM следует, что время доступа составляет 38,75 нс. (для сравнения время доступа 100 MHz SDRAM составляет 40 нс.).

Большое количество банков позволяет (теоретически) достичь идеальной конвейеризации запросов к памяти, - несмотря на то, что данные поступают на шину лишь спустя 40 нс. после подачи запроса (что соответствует 320 тактам в 800 MHz системе), сам поток данных непрерывен.

Таким образом, использование RDRAM в домашних и офисных компьютеров, ничем, кроме желания показать свою "крутость", не оправдано. Для высокопроизводительных рабочих станций лучший выбор - DDR-SDRAM, не уступающей RDRAM в производительности, но значительно выигрывающей у последней в себестоимости.

Слайд 33

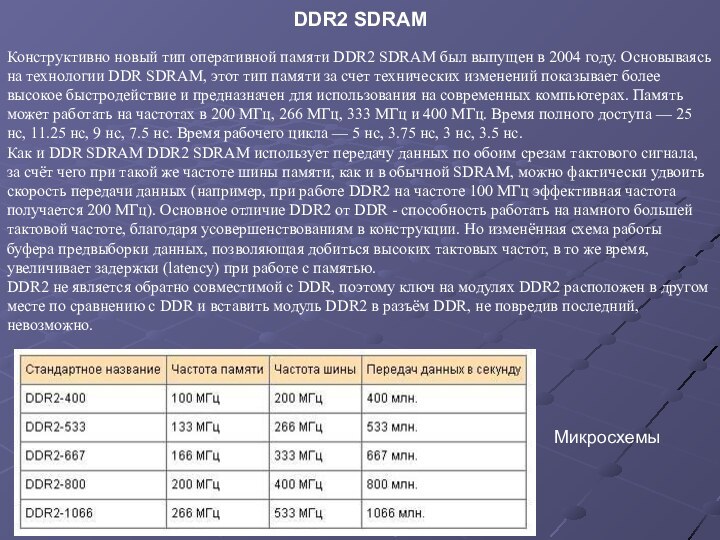

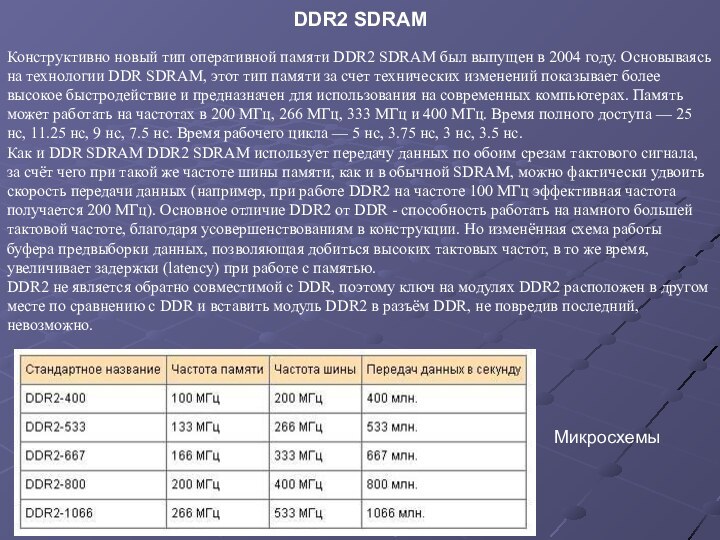

Конструктивно новый тип оперативной памяти DDR2 SDRAM был

выпущен в 2004 году. Основываясь на технологии DDR SDRAM,

этот тип памяти за счет технических изменений показывает более высокое быстродействие и предназначен для использования на современных компьютерах. Память может работать на частотах в 200 МГц, 266 МГц, 333 МГц и 400 МГц. Время полного доступа — 25 нс, 11.25 нс, 9 нс, 7.5 нс. Время рабочего цикла — 5 нс, 3.75 нс, 3 нс, 3.5 нс.

Как и DDR SDRAM DDR2 SDRAM использует передачу данных по обоим срезам тактового сигнала, за счёт чего при такой же частоте шины памяти, как и в обычной SDRAM, можно фактически удвоить скорость передачи данных (например, при работе DDR2 на частоте 100 МГц эффективная частота получается 200 МГц). Основное отличие DDR2 от DDR - способность работать на намного большей тактовой частоте, благодаря усовершенствованиям в конструкции. Но изменённая схема работы буфера предвыборки данных, позволяющая добиться высоких тактовых частот, в то же время, увеличивает задержки (latency) при работе с памятью.

DDR2 не является обратно совместимой с DDR, поэтому ключ на модулях DDR2 расположен в другом месте по сравнению с DDR и вставить модуль DDR2 в разъём DDR, не повредив последний, невозможно.

DDR2 SDRAM

Микросхемы

Слайд 34

Модули

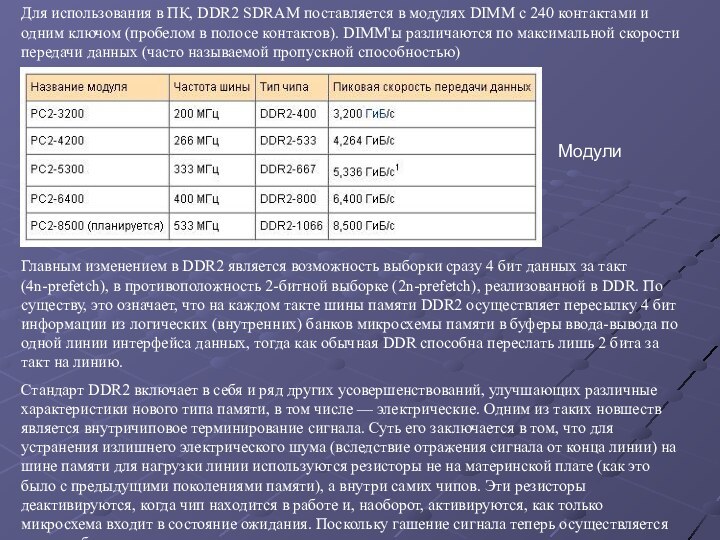

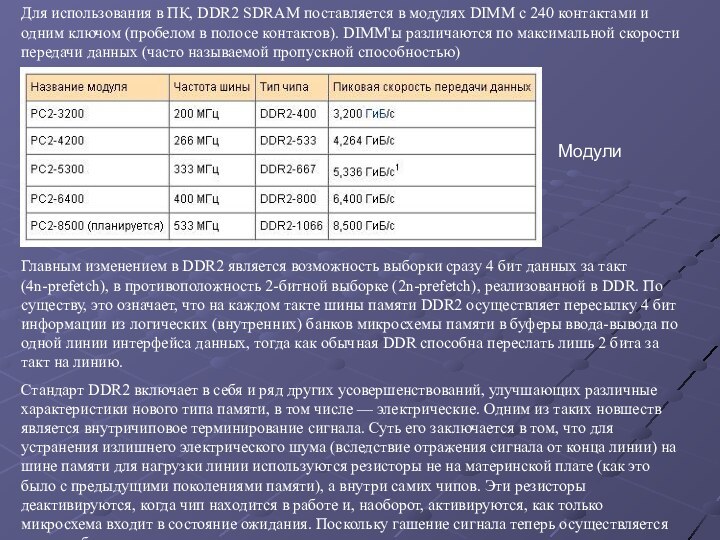

Для использования в ПК, DDR2 SDRAM поставляется в

модулях DIMM с 240 контактами и одним ключом (пробелом

в полосе контактов). DIMM'ы различаются по максимальной скорости передачи данных (часто называемой пропускной способностью)

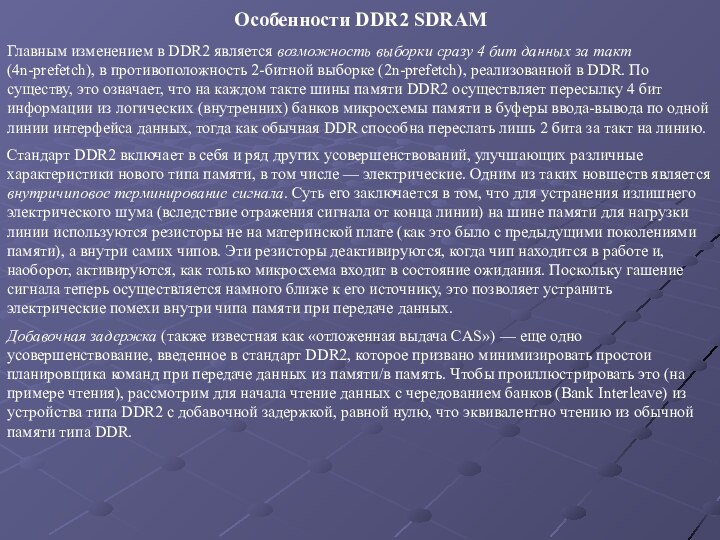

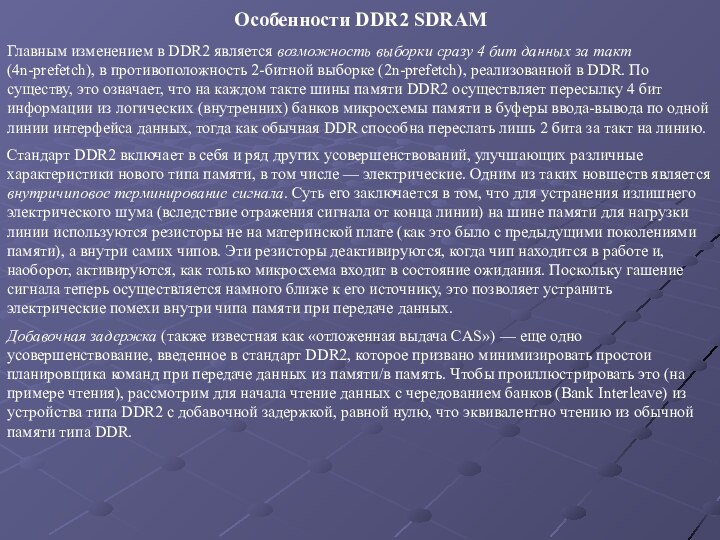

Главным изменением в DDR2 является возможность выборки сразу 4 бит данных за такт (4n-prefetch), в противоположность 2-битной выборке (2n-prefetch), реализованной в DDR. По существу, это означает, что на каждом такте шины памяти DDR2 осуществляет пересылку 4 бит информации из логических (внутренних) банков микросхемы памяти в буферы ввода-вывода по одной линии интерфейса данных, тогда как обычная DDR способна переслать лишь 2 бита за такт на линию.

Стандарт DDR2 включает в себя и ряд других усовершенствований, улучшающих различные характеристики нового типа памяти, в том числе — электрические. Одним из таких новшеств является внутричиповое терминирование сигнала. Суть его заключается в том, что для устранения излишнего электрического шума (вследствие отражения сигнала от конца линии) на шине памяти для нагрузки линии используются резисторы не на материнской плате (как это было с предыдущими поколениями памяти), а внутри самих чипов. Эти резисторы деактивируются, когда чип находится в работе и, наоборот, активируются, как только микросхема входит в состояние ожидания. Поскольку гашение сигнала теперь осуществляется намного ближе к его источнику, это позволяет устранить электрические помехи внутри чипа памяти при передаче данных.

Слайд 35

Особенности DDR2 SDRAM

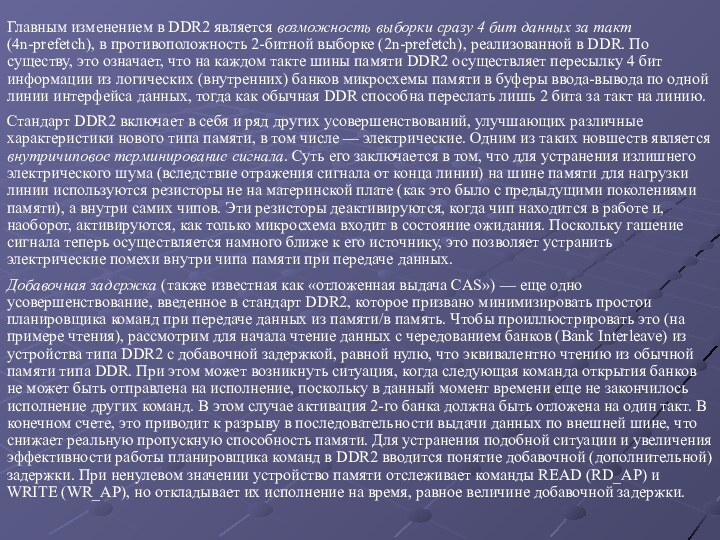

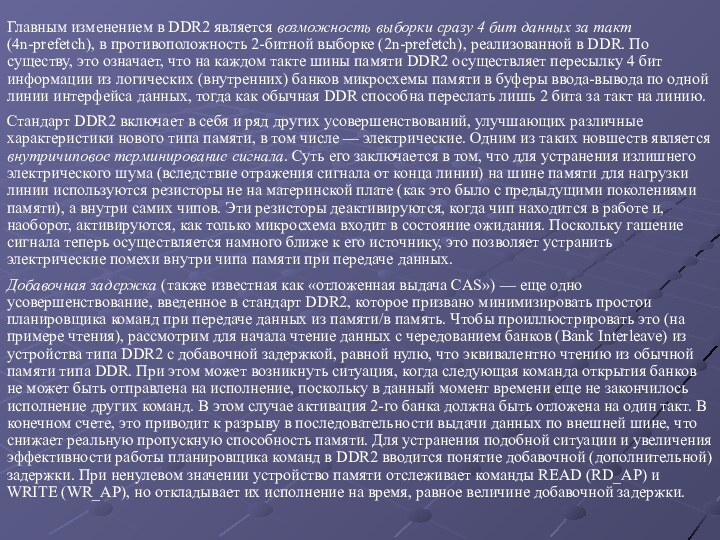

Главным изменением в DDR2 является возможность

выборки сразу 4 бит данных за такт (4n-prefetch), в

противоположность 2-битной выборке (2n-prefetch), реализованной в DDR. По существу, это означает, что на каждом такте шины памяти DDR2 осуществляет пересылку 4 бит информации из логических (внутренних) банков микросхемы памяти в буферы ввода-вывода по одной линии интерфейса данных, тогда как обычная DDR способна переслать лишь 2 бита за такт на линию.

Стандарт DDR2 включает в себя и ряд других усовершенствований, улучшающих различные характеристики нового типа памяти, в том числе — электрические. Одним из таких новшеств является внутричиповое терминирование сигнала. Суть его заключается в том, что для устранения излишнего электрического шума (вследствие отражения сигнала от конца линии) на шине памяти для нагрузки линии используются резисторы не на материнской плате (как это было с предыдущими поколениями памяти), а внутри самих чипов. Эти резисторы деактивируются, когда чип находится в работе и, наоборот, активируются, как только микросхема входит в состояние ожидания. Поскольку гашение сигнала теперь осуществляется намного ближе к его источнику, это позволяет устранить электрические помехи внутри чипа памяти при передаче данных.

Добавочная задержка (также известная как «отложенная выдача CAS») — еще одно усовершенствование, введенное в стандарт DDR2, которое призвано минимизировать простои планировщика команд при передаче данных из памяти/в память. Чтобы проиллюстрировать это (на примере чтения), рассмотрим для начала чтение данных с чередованием банков (Bank Interleave) из устройства типа DDR2 с добавочной задержкой, равной нулю, что эквивалентно чтению из обычной памяти типа DDR.

Слайд 36

Главным изменением в DDR2 является возможность выборки сразу

4 бит данных за такт (4n-prefetch), в противоположность 2-битной

выборке (2n-prefetch), реализованной в DDR. По существу, это означает, что на каждом такте шины памяти DDR2 осуществляет пересылку 4 бит информации из логических (внутренних) банков микросхемы памяти в буферы ввода-вывода по одной линии интерфейса данных, тогда как обычная DDR способна переслать лишь 2 бита за такт на линию.

Стандарт DDR2 включает в себя и ряд других усовершенствований, улучшающих различные характеристики нового типа памяти, в том числе — электрические. Одним из таких новшеств является внутричиповое терминирование сигнала. Суть его заключается в том, что для устранения излишнего электрического шума (вследствие отражения сигнала от конца линии) на шине памяти для нагрузки линии используются резисторы не на материнской плате (как это было с предыдущими поколениями памяти), а внутри самих чипов. Эти резисторы деактивируются, когда чип находится в работе и, наоборот, активируются, как только микросхема входит в состояние ожидания. Поскольку гашение сигнала теперь осуществляется намного ближе к его источнику, это позволяет устранить электрические помехи внутри чипа памяти при передаче данных.

Добавочная задержка (также известная как «отложенная выдача CAS») — еще одно усовершенствование, введенное в стандарт DDR2, которое призвано минимизировать простои планировщика команд при передаче данных из памяти/в память. Чтобы проиллюстрировать это (на примере чтения), рассмотрим для начала чтение данных с чередованием банков (Bank Interleave) из устройства типа DDR2 с добавочной задержкой, равной нулю, что эквивалентно чтению из обычной памяти типа DDR. При этом может возникнуть ситуация, когда следующая команда открытия банков не может быть отправлена на исполнение, поскольку в данный момент времени еще не закончилось исполнение других команд. В этом случае активация 2-го банка должна быть отложена на один такт. В конечном счете, это приводит к разрыву в последовательности выдачи данных по внешней шине, что снижает реальную пропускную способность памяти. Для устранения подобной ситуации и увеличения эффективности работы планировщика команд в DDR2 вводится понятие добавочной (дополнительной) задержки. При ненулевом значении устройство памяти отслеживает команды READ (RD_AP) и WRITE (WR_AP), но откладывает их исполнение на время, равное величине добавочной задержки.

Слайд 37

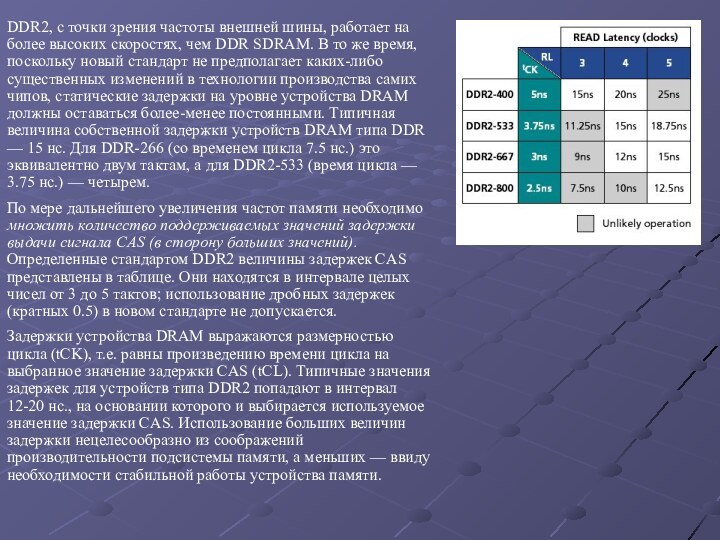

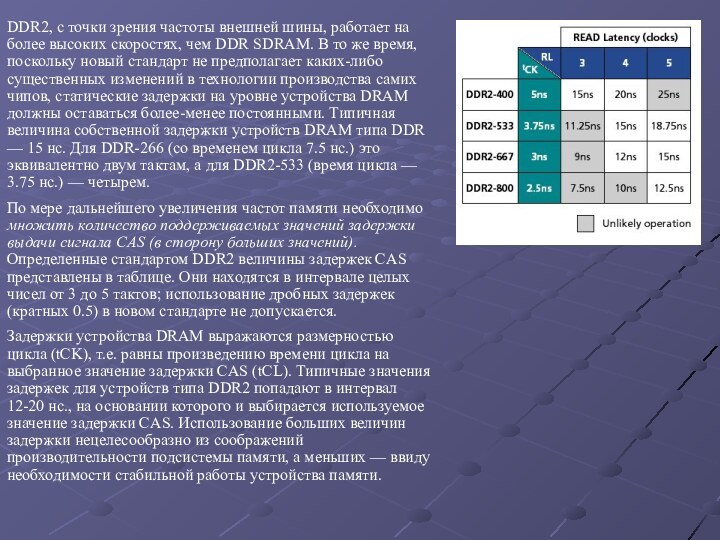

DDR2, с точки зрения частоты внешней шины, работает

на более высоких скоростях, чем DDR SDRAM. В то

же время, поскольку новый стандарт не предполагает каких-либо существенных изменений в технологии производства самих чипов, статические задержки на уровне устройства DRAM должны оставаться более-менее постоянными. Типичная величина собственной задержки устройств DRAM типа DDR — 15 нс. Для DDR-266 (со временем цикла 7.5 нс.) это эквивалентно двум тактам, а для DDR2-533 (время цикла — 3.75 нс.) — четырем.

По мере дальнейшего увеличения частот памяти необходимо множить количество поддерживаемых значений задержки выдачи сигнала CAS (в сторону больших значений). Определенные стандартом DDR2 величины задержек CAS представлены в таблице. Они находятся в интервале целых чисел от 3 до 5 тактов; использование дробных задержек (кратных 0.5) в новом стандарте не допускается.

Задержки устройства DRAM выражаются размерностью цикла (tCK), т.е. равны произведению времени цикла на выбранное значение задержки CAS (tCL). Типичные значения задержек для устройств типа DDR2 попадают в интервал 12-20 нс., на основании которого и выбирается используемое значение задержки CAS. Использование больших величин задержки нецелесообразно из соображений производительности подсистемы памяти, а меньших — ввиду необходимости стабильной работы устройства памяти.

Слайд 38

DDR SDRAM имеет задержку записи, равную 1 такту.

Это означает, что устройство DRAM приступает к «захвату» информации

по шине данных в среднем через один такт после поступления команды WRITE. Тем не менее, учитывая возросшую скорость устройств DDR2, этот промежуток времени оказывается слишком малым для того, чтобы устройство DRAM (а именно, его буфер ввода-вывода) могло успешно подготовиться к «захвату» данных. В связи с этим, стандарт DDR2 определяет задержку записи как задержку выдачи CAS за вычетом 1. Отмечается, что привязка задержки WRITE к задержке CAS не только позволяет достичь более высоких частот, но и упрощает синхронизацию команд чтения и записи (настройку таймингов Read-to-Write).

Процедура записи в память типа SDRAM аналогична операции чтения с разницей в дополнительном интервале, характеризующем период восстановления интерфейса после проведения операции (обычно это двухтактная задержка между окончанием выдачи данных на шину и инициированием нового цикла). Этот временной интервал, измеряемый от момента окончания операции записи до момента вхождения в стадию регенерации (Auto Precharge), обеспечивает восстановление интерфейса после проведения операции записи и гарантирует корректность ее выполнения. Отметим, что стандарт DDR2 не вносит изменений в спецификацию периода восстановления после записи.

Таким образом, задержки устройств типа DDR2 в целом можно считать одной из немногих характеристик, по которой новый стандарт проигрывает спецификации DDR. В связи с чем совершенно очевидно, что использование равночастотной DDR2 вряд ли будет иметь какие-либо преимущества в плане скорости по отношению к DDR. Как это обстоит на самом деле — как всегда, покажут результаты соответствующих тестов.

Слайд 39

Cпециальный тип оперативной памяти Video RAM (VRAM) был

разработан на основе памяти типа SDRAM для использования в

видеоплатах. Он позволял обеспечить непрерывный поток данных в процессе обновления изображения, что было необходимо для реализации изображений высокого качества. На основе памяти типа VRAM, появилась спецификация памяти типа Windows RAM (WRAM), иногда её ошибочно связывают с операционными системами семейства Windows. Её производительность стала на 25 % выше, чем у оригинальной памяти типа SDRAM, благодаря некоторым техническим изменениям.

Video RAM

Слайд 40

Микросхемы динамической памяти

Модули памяти состоят из набора микросхем

памяти объединенных общей шиной.

Микросхемы имеют определенную емкость. Внутри одного

модуля обычно используются микросхемы одного типа и объема.

Маркировка микросхем памяти несет информацию об изготовителе, объеме, типе памяти, быстродействии, напряжении питания, дате изготовления и т.д.

Единой строгой системы обозначений нет. Однако в большинстве случаев буквенный код перед цифровой частью маркировки означает фирму-производителя микросхемы. Например:

HM – Hitachi;

HY – Hyundai;

KM – Samsung;

M-OKI;

MCM-Motorola

MT-Micron;

TMM-Toshiba;

TMS-Texas Instruments;

(n)PD-NEC.

Слайд 41

Корпуса микросхем

Микросхемы упаковываются в корпуса различных типов:

DIP –

корпус с двухрядным расположением штырьковых выводов

DIP-16

DIP-20

Слайд 42

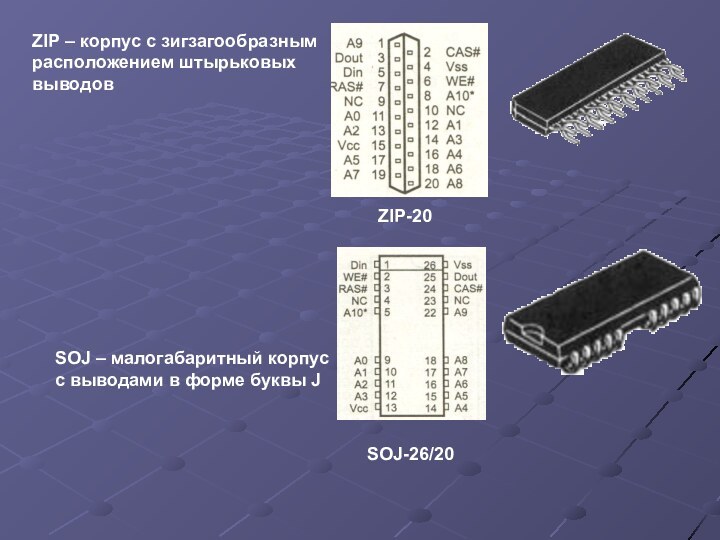

ZIP – корпус с зигзагообразным расположением штырьковых выводов

ZIP-20

SOJ

– малогабаритный корпус с выводами в форме буквы J

SOJ-26/20

Слайд 43

TSOP – тонкий пластмассовый корпус (примерно в 2

раза тоньше SOJ) для поверхностного монтажа. Шаг выводов 0,85мм

TSOP-II

– тоже что и TSOP но с шагом выводов 0,65мм

TSOP-II

Слайд 44

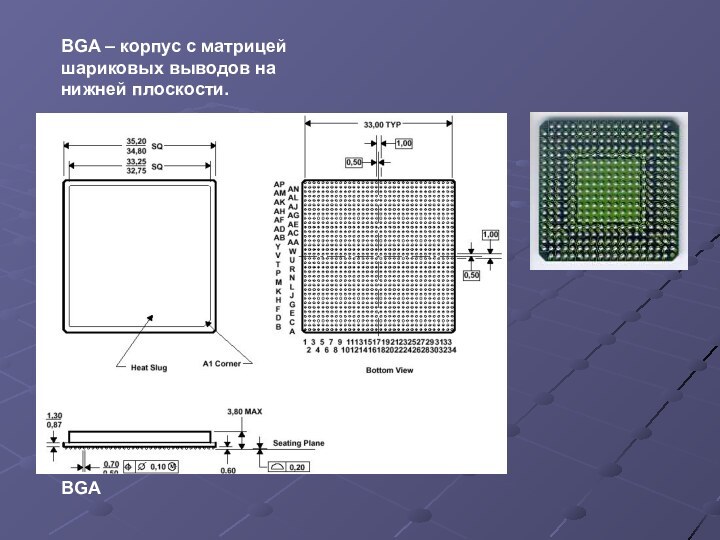

BGA – корпус с матрицей шариковых выводов на

нижней плоскости.

BGA

Слайд 45

Модули динамической памяти

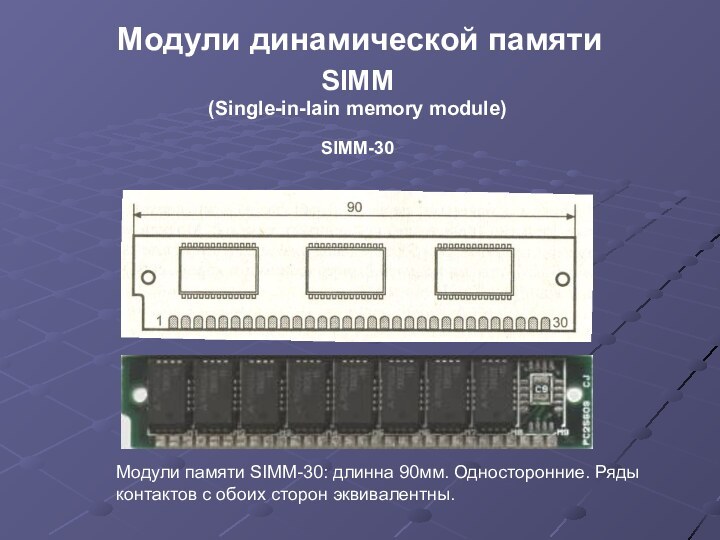

SIMM

(Single-in-lain memory module)

SIMM-30

Модули памяти SIMM-30: длинна

90мм. Односторонние. Ряды

контактов с обоих сторон эквивалентны.

Слайд 46

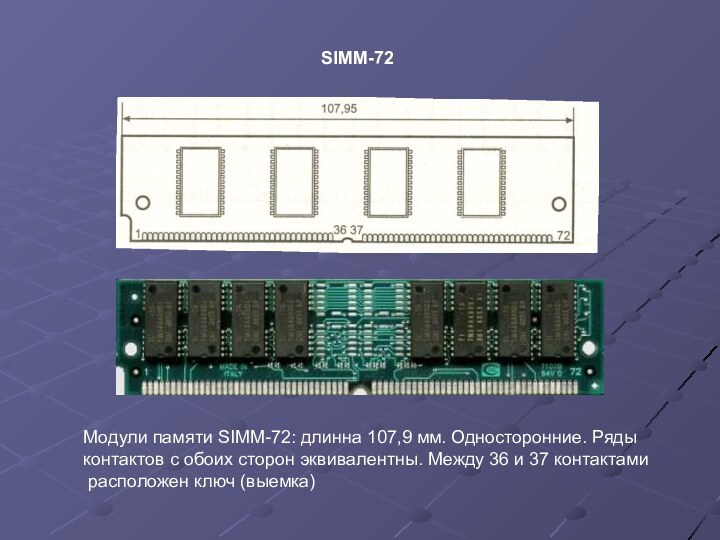

SIMM-72

Модули памяти SIMM-72: длинна 107,9 мм. Односторонние. Ряды

контактов с обоих сторон эквивалентны. Между 36 и 37

контактами

расположен ключ (выемка)

Слайд 47

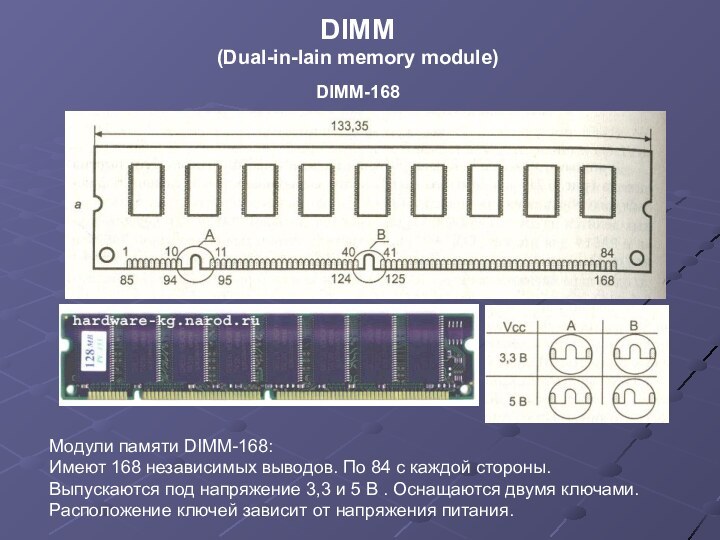

DIMM

(Dual-in-lain memory module)

DIMM-168

Модули памяти DIMM-168:

Имеют 168 независимых

выводов. По 84 с каждой стороны. Выпускаются под напряжение

3,3 и 5 В . Оснащаются двумя ключами. Расположение ключей зависит от напряжения питания.

Слайд 48

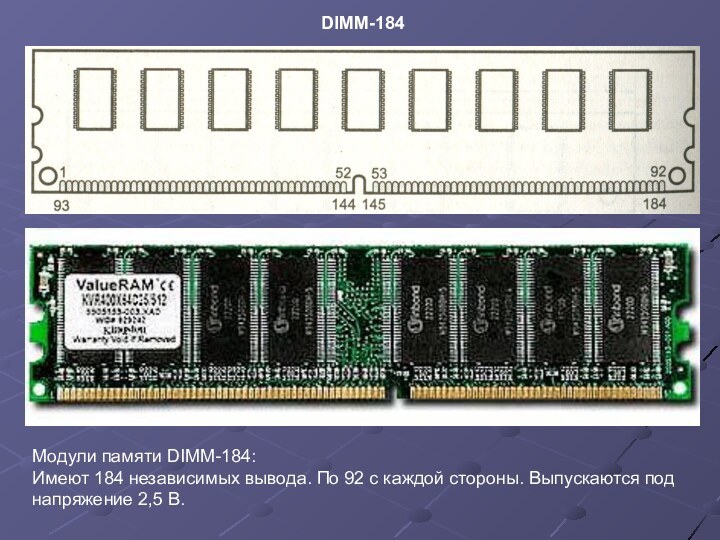

DIMM-184

Модули памяти DIMM-184:

Имеют 184 независимых вывода. По

92 с каждой стороны. Выпускаются под напряжение 2,5 В.

Слайд 49

SO DIMM-144

Модули памяти SO DIMM:

Малогабаритные модули памяти.

Напряжение питания 3,3 или 5 В контролируется при помощи

ключей расположенных сбоку – у 72pin модулей и расположенных снизу – у 144pin

SO DIMM

SO DIMM-72

Слайд 50

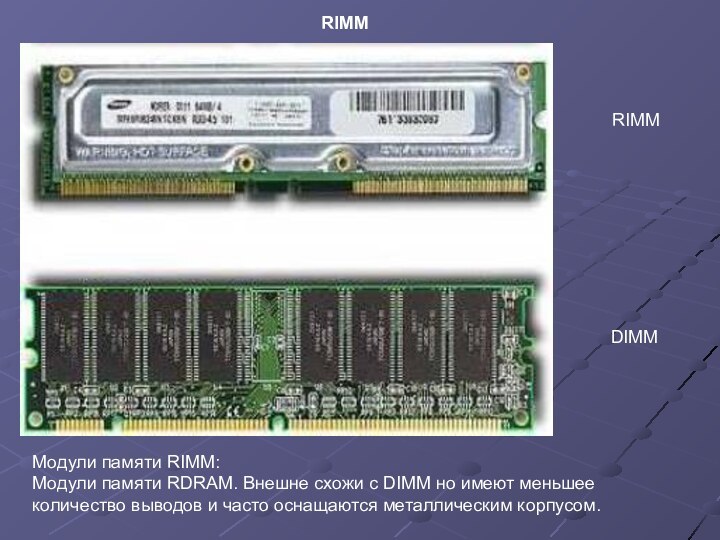

RIMM

Модули памяти RIMM:

Модули памяти RDRAM. Внешне схожи

с DIMM но имеют меньшее количество выводов и часто

оснащаются металлическим корпусом.

RIMM

DIMM

Слайд 51

Наиболее вероятным направлением развития считается память на базе

технологии DDR2

Эта технология является продолжением технологии DDR. Но, благодаря

новым

Разработкам позволяет поддерживать большую частоту.

Развитие

Слайд 53

Установка модулей DIMM и RIMM

Открыть слот (откинуть защелки)

Сориентировать

ключи модуля

относительно ключей слота.

Установить модуль памяти в слот

Нажать

сверху вниз, так,

чтобы защелки закрылись

Модуль установлен

Слайд 54

При установке модулей памяти любого типа следует учитывать

следующие моменты:

Внимательно следить за ориентированием модуля относительно слота –

ключи должны совпадать!

Контроллер отвечающий за управление памятью рассчитывается на определенный максимальный объем памяти (банк памяти). Модули памяти большего объема работать не будут. Уточнить размер банков памяти можно в описании материнской платы.

Некоторые версии BIOS могут некорректно определять размер установленной памяти. В этом случае некоторый объем ее будет не доступен и нужно корректировать настройки вручную.

При установке модулей памяти в мат.плату оснащенную системой DualCannal следует равномерно заполнять оба канала.

Рекомендуется использовать одинаковые модули памяти

В ПК на процессорах Pentium 100-133 и т.п. встречается ситуация когда модули SIMM работают только если установлено более 2-х.

Общие вопросы установки модулей памяти

Слайд 55

Чтобы увеличить количество слотов для модулей памяти используют

модули расширения которые позволяют установить в один слот

несколько

модулей памяти.

Модуль расширения SIMM

Модули расширения

Модуль расширения DIMM на 16 Gb

Слайд 56

Некоторые современные модули памяти требуют дополнительного охлаждения.

Особенно

если производился «разгон». Большинство специальных систем

охлаждения модулей памяти

– пассивные и представляют собой радиаторы,

укрепляемые на модулях памяти.

Радиатор, пластины, крепления

Охлаждение

Радиатор Thermaltake

Модуль памяти с охлаждением