- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Видеоадаптеры Radeon

Содержание

- 2. Содержание :::::::::::::История создания ATiХарактеристики видеокарт на базе

- 3. История создания

- 4. Первые месяцы ушли на борьбу с неизвестностью.

- 5. Серия RV3xxВ эту серию входят видеокарты: X300,

- 6. Серия RV4xx Входят видеокарты X700, X800, X850Серия

- 7. Серия RV5xx. Рассмотрим ее более подробноВходят видеокарты

- 8. Архитектура R520/RV530/RV515 Архитектура вершинных процессоров

- 9. Архитектура пиксельной части (часть 1) в отличие

- 10. Архитектура пиксельной части (часть 2)

- 11. и может выполнить за такт

- 12. Как видно, RV530

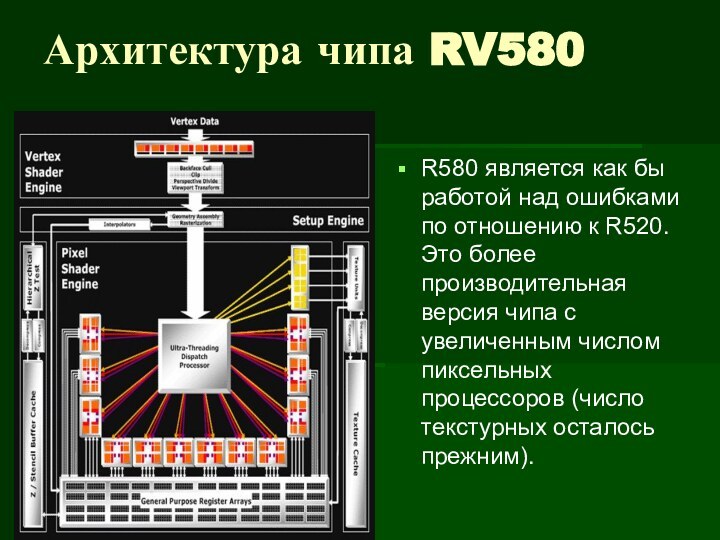

- 13. Архитектура чипа RV580R580 является как бы работой

- 14. Скачать презентацию

- 15. Похожие презентации

Содержание :::::::::::::История создания ATiХарактеристики видеокарт на базе чипов семейств RV5xx, RV4xx и RV3xx Архитектура чипа RV5xxИнтерфейсы вывода

Слайд 2

Содержание :::::::::::::

История создания ATi

Характеристики видеокарт на базе чипов

семейств RV5xx, RV4xx и RV3xx

Слайд 3 История создания

или

…как все начиналось

Сейчас необходимость

графических процессоров понятна всем, однако в 1985 году, когда Хо и два его партнера основали ATI, все было не так просто. Хо, незадолго до того эмигрировавший из Гонконга, по образованию был инженером-электронщиком и успел поработать на родине в таких компаниях, как Control Data Systems, Philips Electronics и National Semiconductor. В Канаде, однако, он не смог найти работу - поскольку он был эмигрантом, считалось, что у него недостаточно "соответствующего опыта". Тем не менее, когда был выпущен Macintosh с его графическим интерфейсом, Хо правильно оценил направление движения компьютерной отрасли. Рискнув своими сбережениями, он и два его друга - Ли Лау и Бенни Лау (не родственники) вложили в общей сложности 300 тысяч долларов в создание компании ATI. Фирма была значительно компактнее, чем можно было ожидать - в ней было всего шесть сотрудников. "Функции секретаря, дежурного в приемной и отдела поставок исполнял один человек," - смеется Хо. У компании не было средств на создание собственного производства микросхем - дело, требующее многих миллионов долларов, - и она заказывала схемы на заводе в Калифорнии. Слайд 4 Первые месяцы ушли на борьбу с неизвестностью. ATI

разработала графический процессор, но она была лишь маленькой непроверенной

канадской фирмой. Хо вспоминает: "Изготовители компьютеров говорили: - Зачем вы нам нужны?" Через четыре месяца начальный капитал был истрачен. На выручку пришел Overseas Union Bank of Singapore, предоставивший кредит в 300 тысяч долларов, который потом был увеличен до 1.5 миллионов. Однако по меньшей мере один фактор сыграл в пользу ATI: большие объемы заказов, характерные для производства графической продукции. Если графический процессор понравился изготовителю компьютеров, счет начинает идти на сотни тысяч. В случае ATI объемы продаж резко возросли во второй половине первого года существования фирмы, когда компания Commodore заказала поставки 7000 процессоров в неделю. К концу первого года ATI заработала 10 миллионов долларов. "Это был первый реальный фактор выживания," - говорит Хо.

Слайд 5

Серия RV3xx

В эту серию входят видеокарты: X300, X550,

X600 и их различные модификации-SE, HP, XT,PRO;

Основные характеристики: у

всей серии по 4 пиксельных и 2 вершинных конвейера; поддержка шейдера 2.0 (DirectX 9.0 и OpenGL 2.0); 128 или 256 mb памяти;

Слайд 6

Серия RV4xx

Входят видеокарты X700, X800, X850

Серия имеет

от 8(X700) до16(X850) пиксельных и 6 вершинных конвейеров. Память

устанавливается в объёме от 128 MB до 512 MB; обстановка не меняется в поддержке версии шейдера- по прежнему 2.0 (DirectX 9.0 и OpenGL 2.0)

Слайд 7

Серия RV5xx.

Рассмотрим ее более подробно

Входят видеокарты серии X1300,X1600,X1900

и X1950;

Radeon X1300 является начальным игровым решением с поддержкой

шейдера 3.0 (DirectX 9.0c). Основан на графическом процессоре RV515, имеет 4 пиксельных и 3 вершинных конвейера.Radeon X1600 основана на процессоре RV530. Конвейерная формула — 4x3 (4 текстурных блока и 12 пиксельных), 5 вершинных процессоров. Частота графического чипа— 500 МГц, в то время как память работает на частоте 390(780) МГц.Карта оснащается памятью типа GDDR3 объёмом от 128 MB до 512 MB и имеет шину памяти шириной 128 бит.

Radeon X1800 PROОснован на чипе R520, имеет 16 пиксельных и 8 вершинных конвейеров, работающих на частоте 625 МГц.Карта оснащается памятью типа GDDR3 объёмом 256 или 512 MB, работающей на частоте 750 (1500) МГц. Шина памяти имеет ширину 256 бит.

Radeon X1900 XT — high-end решение, основанное на процессоре R580. В отличие от своего прототипа R520, этот чип имеет более совершенную конвейерную формулу 16x3: 16 текстурных блоков, 16 блоков растеризации и 48 блоков пиксельных шейдеров. Вершинных процессоров 8. Частота процессора осталась неизменной по сравнению с X1800 XT и составляет 625 МГц.Карта оснащается памятью типа GDDR3 объёмом 512 MB, работающей на частоте 725 (1450) МГц и имеет шину памяти шириной 256 бит.

Слайд 8

Архитектура R520/RV530/RV515

Архитектура вершинных процессоров

В наличии

восемь одинаковых вершинных процессоров), соответствующих требованиям SM 3.0 и

построенных по стандартной для ATI схеме 3+1 (ALU каждого вершинного процессора может исполнять две разные операции одновременно, над тремя компонентами вектора и четвертой компонентой или скаляром). Фактически, вершинные процессоры стали очень похожими на NV4X и G7X.

Слайд 9

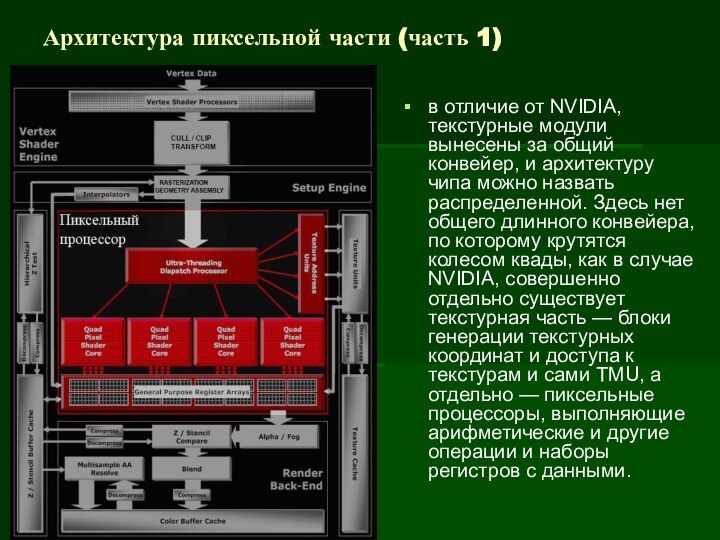

Архитектура пиксельной части (часть 1)

в отличие от NVIDIA,

текстурные модули вынесены за общий конвейер, и архитектуру чипа

можно назвать распределенной. Здесь нет общего длинного конвейера, по которому крутятся колесом квады, как в случае NVIDIA, совершенно отдельно существует текстурная часть — блоки генерации текстурных координат и доступа к текстурам и сами TMU, а отдельно — пиксельные процессоры, выполняющие арифметические и другие операции и наборы регистров с данными.

Слайд 10

Архитектура пиксельной части (часть 2)

Ultra Threading Dispatch Processor управляет исполнением —

одновременно в обработке находится 512 квадов, каждый из которых может быть на разных стадиях исполнения шейдера. Вместе с каждым квадом хранится его текущее состояние, текущая команда шейдера, значения ранее проверенных условий. В чипах NVIDIA квады идут по кругу, один за другим, и максимум, что возможно — пропуск квадов, не подпадающих под текущую ветку условия. В R520 работа организована по иному — Ultra Threading Dispatch Processor постоянно проверяет наличие свободных ресурсов (будь то текстурные блоки или пиксельные) и направляет стоящие на очереди квады в освободившиеся устройства. Если квад не прошел проверку на условие и не должен обрабатываться той или иной частью шейдера, то он не будет болтаться по кругу, занимая место и время, вместе с другими квадами, которые нуждаются в обработке. Он просто пропустит те команды, которые ему не нужны и не будет занимать работой текстурный или пиксельный блок. Если квад ждет данных из текстурного блока — он пропустит вперед другие квады, которые загрузят пиксельные вычислительные блоки.Слайд 11 и может выполнить за такт над

четырьмя пикселями пять операций, так же параллельно может происходить

операция адресации текстуры, то есть запроса данных из TMU. Таким образом, в случае оптимального кода шейдера мы получаем пиковую производительность в шесть операций за тактпиксельные процессоры сгруппированы по 4 , то есть фактически мы имеем не 16 отдельных процессоров, а 4 процессора квадов, обрабатывающих за один такт 4 пикселя. Каждый такой процессор квадов состоит из следующего набора блоков:

Слайд 12 Как видно, RV530 и

RV515 построены по той же самой схеме. В RV515

остался только один квад — это упрощает многие аспекты, в том числе и для Ultra Threading Dispatch Processor . В RV530 ситуация сложнее — там три пиксельных процессора квада, но только один текстурный блок. То есть, мы имеем 12 пиксельных процессоров и 4 TMU, пусть и используемых оптимальным путем, практически без простоев.Логично предположить, что такая архитектура с разделенными текстурными и пиксельными блоками может очень хорошо масштабироваться :