- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Сумматоры. Виды

Содержание

- 2. Двоичный сумматор Двоичный сумматор (SM) служит для

- 3. Полусумматор Полусумматор (HS - HalfSum - полусумма),

- 4. Полусумматор

- 5. Полусумматор

- 6. Полный одноразрядный сумматор Полный одноразрядный сумматор суммирует

- 7. Полный одноразрядный сумматорПолный одноразрядный сумматор можно построить

- 8. Многоразрядный сумматорДля сложения двух многоразрядных двоичных чисел

- 9. Многоразрядный сумматорВ корпусе микросхемы К155ИМ3 четыре полных одноразрядных сумматора объединены в схему четырехразрядного сумматора.

- 10. Схемы вычитанияВычитание можно осуществить, инвертируя число В и суммируя полученный результат с А.

- 11. Схемы вычитанияПри А > В получаем Р

- 12. При С=0 устройство работает как сумматор.При С=1 – как вычитатель.

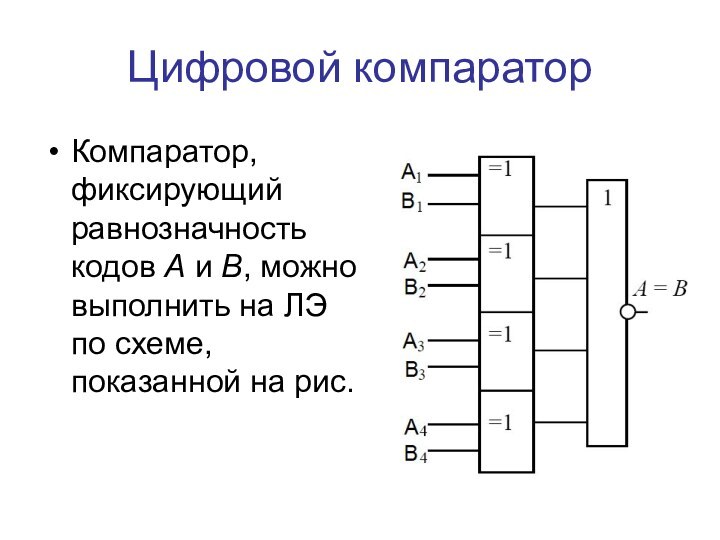

- 13. Цифровой компараторЦифровым компаратором называют устройство, фиксирующее результат

- 14. Цифровой компаратор

- 15. Скачать презентацию

- 16. Похожие презентации

Двоичный сумматор Двоичный сумматор (SM) служит для формирования арифметической суммы n-разрядных двоичных чисел А и В. Результатом сложения (при n = 4) является четырехразрядная сумма S и выход переноса Р, который можно рассматривать как пятый разряд