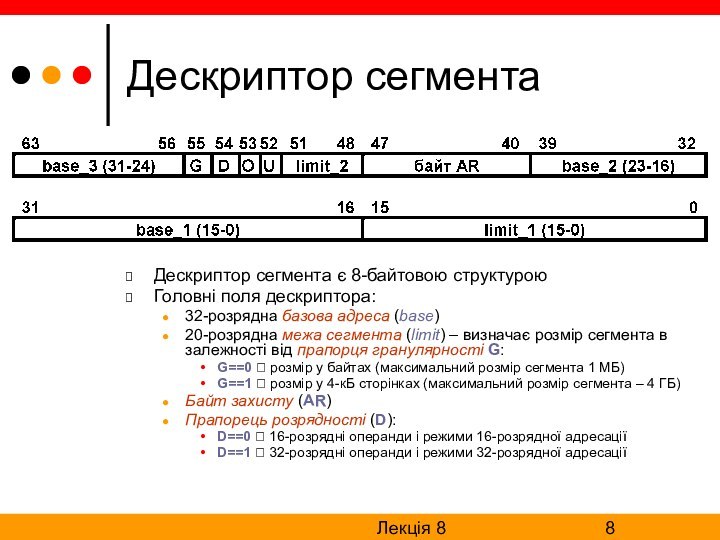

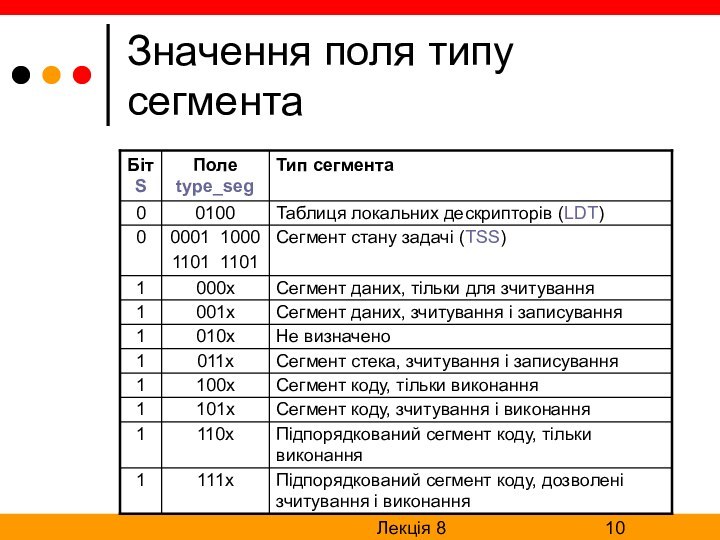

і дескриптор сегмента

Захист сегментів

Завантаження селектора у сегментний регістр

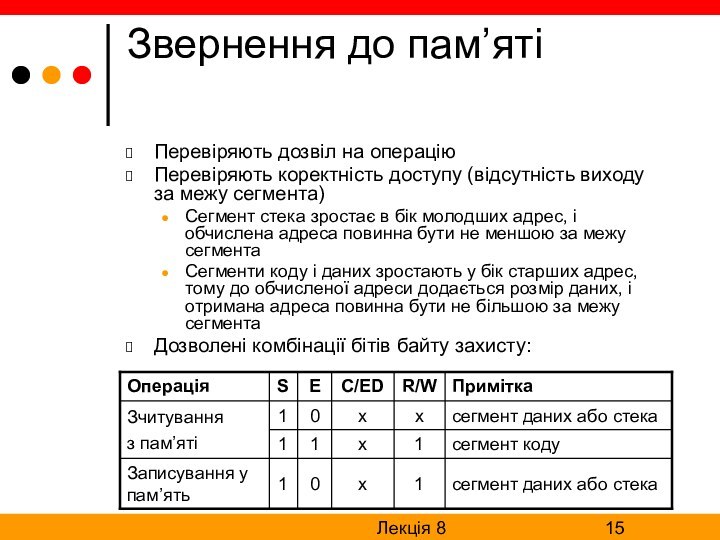

Звернення до

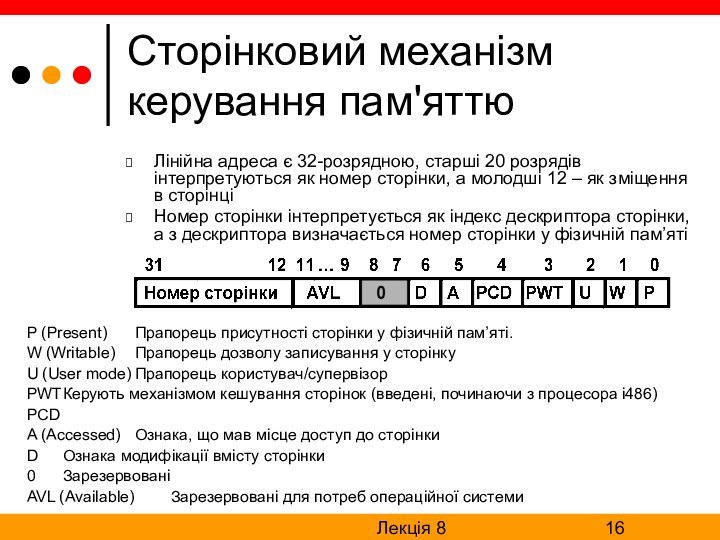

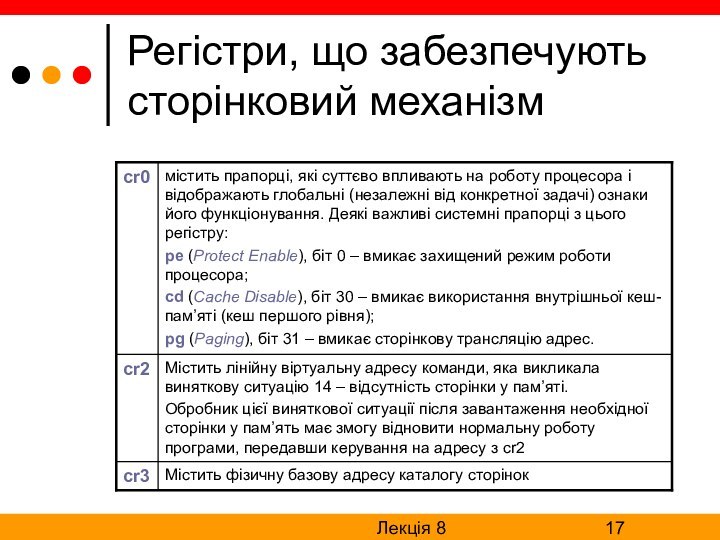

пам’ятіСторінковий механізм керування пам'яттю

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Email: Нажмите что бы посмотреть

Байт захисту

P (Present) Прапорець присутності сторінки у фізичній пам’яті.

W (Writable) Прапорець дозволу записування у сторінку

U (User mode) Прапорець користувач/супервізор

PWT Керують механізмом кешування сторінок (введені, починаючи з процесора i486)

PCD

A (Accessed) Ознака, що мав місце доступ до сторінки

D Ознака модифікації вмісту сторінки

0 Зарезервовані

AVL (Available) Зарезервовані для потреб операційної системи