- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Микросхемы памяти

Содержание

- 2. SRAMСтатическая оперативная память с произвольным доступом (SRAM,

- 3. Ячейка SRAMТипичная ячейка состоит из двух перекрёстно

- 4. Преимущества и недостатки SRAMПреимущества:Быстрый доступ. SRAM —

- 5. DRAMDRAM (Dynamic random access memory, Динамическая память

- 6. Принцип действия DRAMФизически DRAM-память представляет собой набор

- 7. nvSRAMnvSRAM (nonvolatile SRAM) – энергонезависимая память, основанная

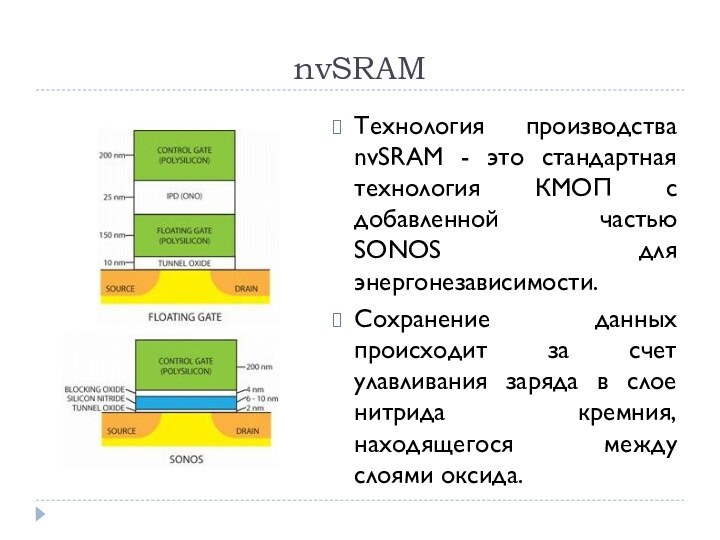

- 8. nvSRAMТехнология производства nvSRAM - это стандартная технология

- 9. Скачать презентацию

- 10. Похожие презентации

SRAMСтатическая оперативная память с произвольным доступом (SRAM, static random access memory) — полупроводниковая оперативная память, в которой каждый двоичный или троичный разряд хранится в схеме с положительной обратной связью, позволяющей поддерживать состояние без регенерации, необходимой в

Слайд 3

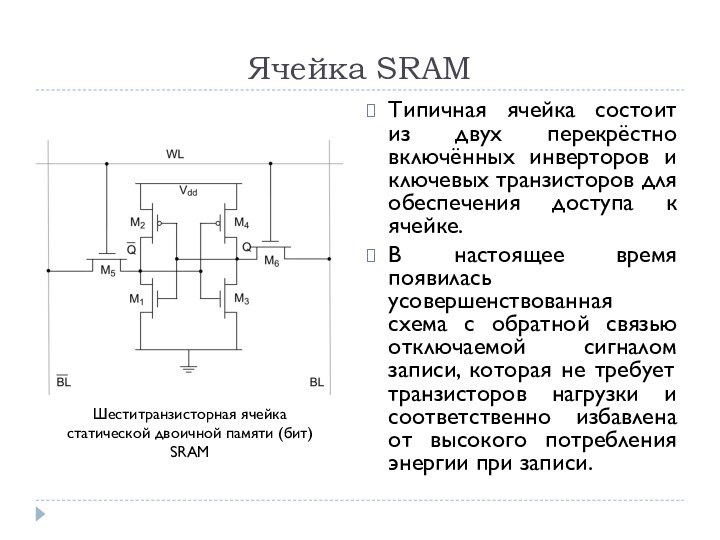

Ячейка SRAM

Типичная ячейка состоит из двух перекрёстно включённых

инверторов и ключевых транзисторов для обеспечения доступа к ячейке.

В

настоящее время появилась усовершенствованная схема с обратной связью отключаемой сигналом записи, которая не требует транзисторов нагрузки и соответственно избавлена от высокого потребления энергии при записи.Шеститранзисторная ячейка статической двоичной памяти (бит) SRAM

Слайд 4

Преимущества и недостатки SRAM

Преимущества:

Быстрый доступ. SRAM — это

действительно память произвольного доступа, доступ к любой ячейке памяти

в любой момент занимает одно и то же время.Простая схемотехника — SRAM не требуются сложные контроллеры. Возможны очень низкие частоты синхронизации, вплоть до полной остановки синхроимпульсов.

Недостатки:

Невысокая плотность записи (шесть-восемь элементов на бит, вместо двух у DRAM).

Вследствие чего — дороговизна килобайта памяти.

Слайд 5

DRAM

DRAM (Dynamic random access memory, Динамическая память с

произвольным доступом) — тип энергозависимой полупроводниковой памяти с произвольным

доступом; DRAM широко используемая в качестве оперативной памяти современных компьютеров, а также в качестве постоянного хранилища информации в системах, требовательных к задержкам.Физически DRAM состоит из ячеек, созданных в полупроводниковом материале, в каждой из которых можно хранить определённый объём данных, строку от 1 до 4 бит. Совокупность ячеек такой памяти образуют условный «прямоугольник», состоящий из определённого количества строк и столбцов. Один такой «прямоугольник» называется страницей, а совокупность страниц называется банком. Весь набор ячеек условно делится на несколько областей.

Слайд 6

Принцип действия DRAM

Физически DRAM-память представляет собой набор запоминающих

ячеек, которые состоят из конденсаторов и транзисторов, расположенных внутри

полупроводниковых микросхем памяти.Cтрока является минимальной порцией обмена с динамической памятью, поэтому обмен данными с отдельно взятой ячейкой невозможен

Принцип чтения DRAM