- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

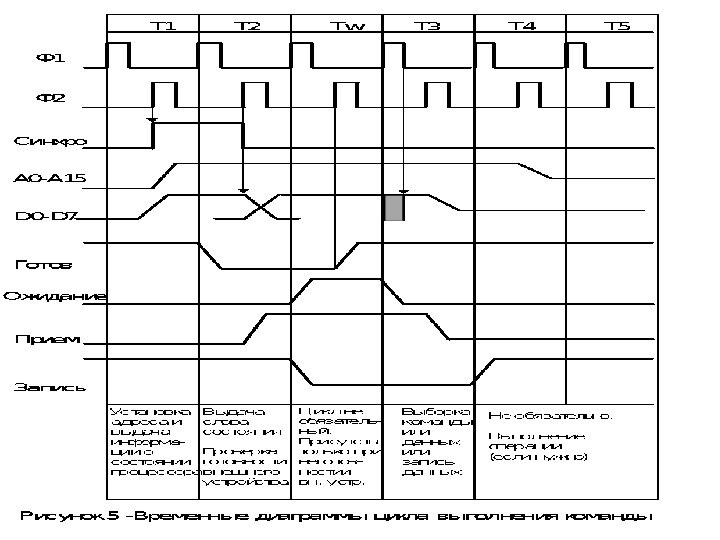

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Микропроцессор. Устройство и принцип действия ЭВМ. (Лекция 2)

Содержание

- 2. Микропроцессор. Структурная схема микроЭВМ. Система команд микроЭВМ. Организация памяти МП-системы.

- 3. С развитием технологии и схемотехники цифровых интегральных

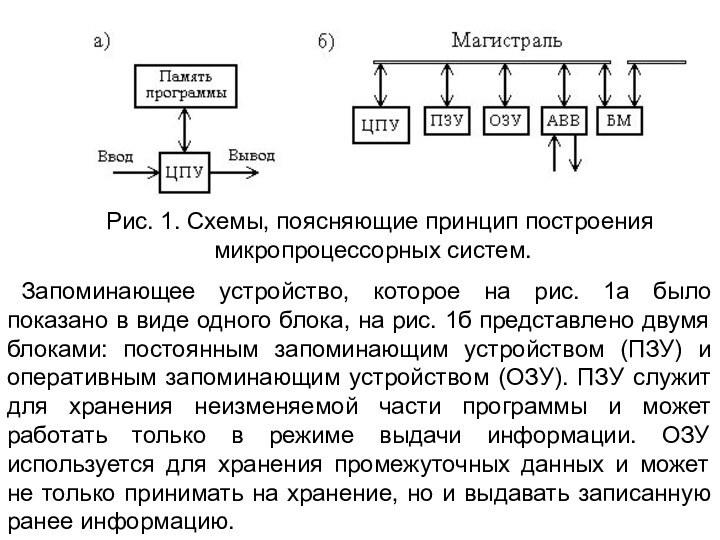

- 4. Рис. 1. Схемы, поясняющие принцип построения микропроцессорных

- 5. Для того чтобы согласовать устройства ввода-вывода информации

- 6. Микропроцессорные наборы, совместимые по принятым системам команд,

- 7. Наибольшей популярностью пользуется МП серии К580 ‑

- 8. В конце 1973 года фирма Intel выпустила

- 9. Состав МПК БИС К580Тип БИС

- 10. Отдельные задачи измерительной тех-ники могут эффективно решать

- 11. В 1981 г. фирма IBM выпустила на

- 12. Модель РС использовала до двух внешних накопителей

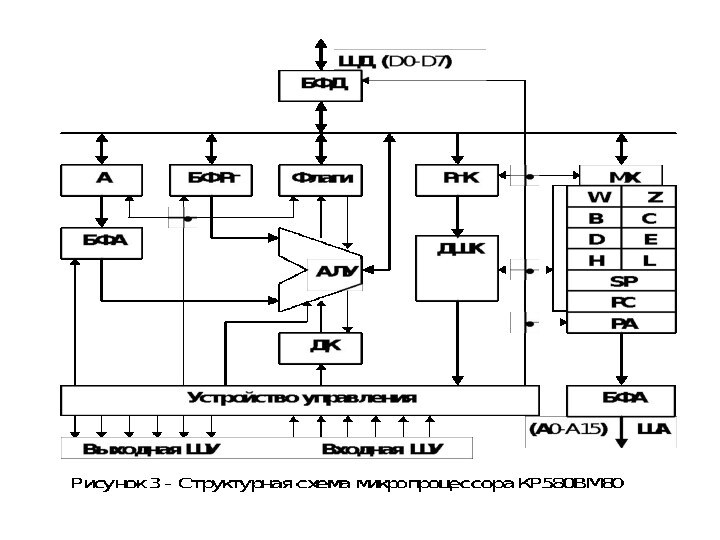

- 13. Упрощенная структурная схема, этого МП КР580ВМ80 построенная

- 14. Рис. 2. Структурная схема микропроцессорной системы на

- 15. Шина данных в МП-системе ‑ двунаправлен-ная. Информация

- 16. Поэтому часть сигналов управления передается по выводам

- 17. Разрядностью шины адреса (ША) определяется предельно возможный

- 18. Внутренняя функциональная схема МП 8080 на рис.

- 19. Непосредственно к АЛУ примыкает регистр флажков (RG

- 20. Бит переноса устанавливается равным 1 при переносе

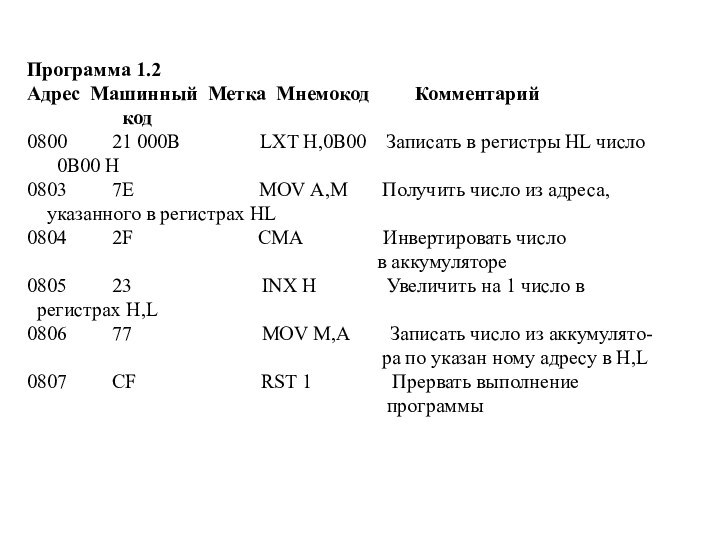

- 21. Не все операции, выполняемые в АЛУ, воздействуют

- 22. Шестнадцатиразрядный регистр SP (stack pointer) ‑это указатель

- 23. Соответственно при помещении в стек очередного слова

- 24. Показанный на схеме рис. 2 16-разрядный регистр

- 25. Устройство управления УУ, входящее в состав МП

- 27. Буферные регистры W,Z не являются программно доступными

- 28. Выполнение каждой команды производится в МП БИС

- 29. При анализе процессов будем использовать следующие понятия:Машинный

- 30. 1. Извлечение кода команды (М1).2. Чтение данных

- 31. Отдельные разряды слова состояния задей-ствуются в микро-ЭВМ

- 32. 1. Извлечение кода команды или данных из

- 34. На такте Т2 слово состояния записывается в

- 35. Если к моменту появления отрицательного фронта Ф2

- 36. На такте Т3 в момент отрицательного фронта

- 37. Отличие машинных циклов чтения данных из памяти

- 38. 2. Запись данных в память или внешнее

- 39. Начальная установка.В течение всего времени, пока входе

- 40. Режимы работы МП-системы. МП-система ‑ это, в

- 41. Установка в состояние 0000Н регистра РС приведет

- 42. Микропроцессор БИС КР580ВМ80 имеет фиксированный набор команд.

- 43. Ряд команд МП предусматривает обработку или передачу

- 44. В трехбайтных командах второй и третий байты

- 45. Для удобства сохранения и восстановления состояния МП

- 46. Для ускорения вычислений некоторые операнды хранятся в

- 47. 3. Система команд микроЭВМ. Последовательность (закон) преобразования

- 48. Поэтому в зависимости от разновидности операции и

- 49. Отличительной особенностью команды условного перехода от команд

- 50. Буферные регистры W,Z не являются программно доступными регистрами и используются для выполнения команд внутри МП БИС.

- 51. Кроме двоичной системы, в ЭВМ часто используется

- 52. Сначала двоичное число разбивается на тетрады, затем

- 53. Команды передачи данныхПервая группа команд обеспечивает выполнение

- 54. Команды MOV M,Rj осуществляют передачу содержимого одного

- 55. Команды MOV Ri,M осуществляют передачу содержимого ячейки

- 56. MVI M,V (код – 36(16)) осуществляет непосредственную

- 57. LHLD аа загружает регистровую пару H,L содержимым

- 58. Арифметические командыЭти команды предназначены для выполнения операции

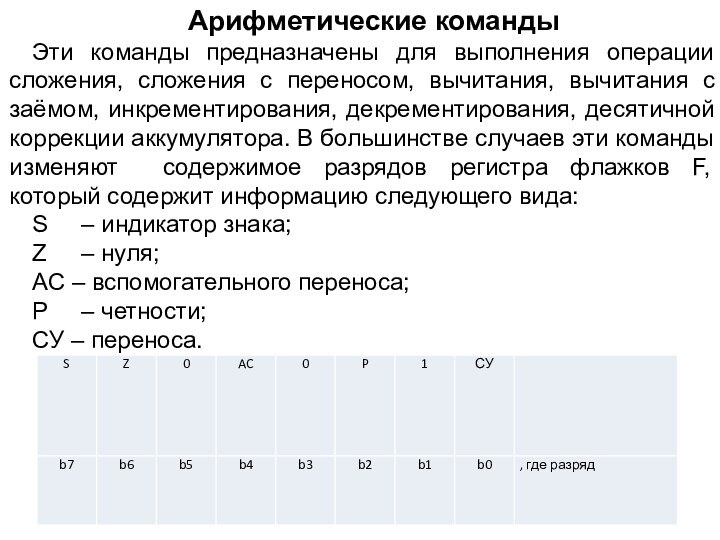

- 59. Рассмотрим команды этой группы:ADD Ri осуществляет сложение

- 60. ADI V выполняет сложение в АЛУ аккумулятора

- 61. Логические команды Задачей этих команд является выполнение поразрядной

- 62. Команды передачи управления Четвертая группа команд содержит команды

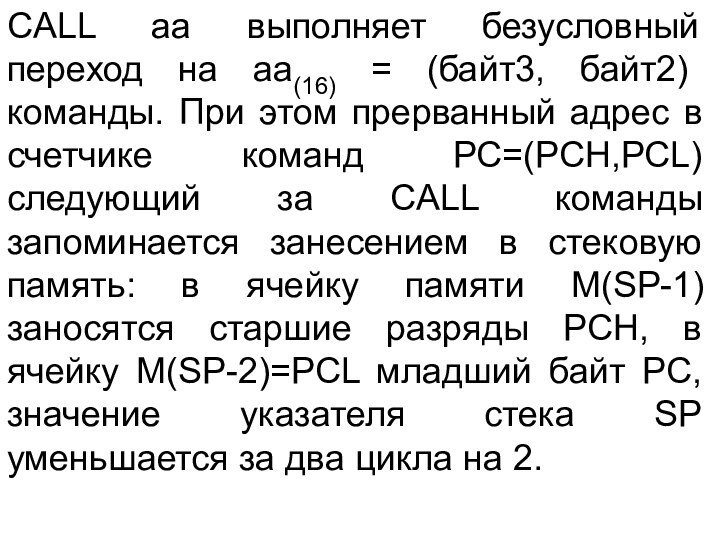

- 63. CALL aa выполняет безусловный переход на аа(16)

- 64. Данная команда осуществляет безусловный переход на аа,

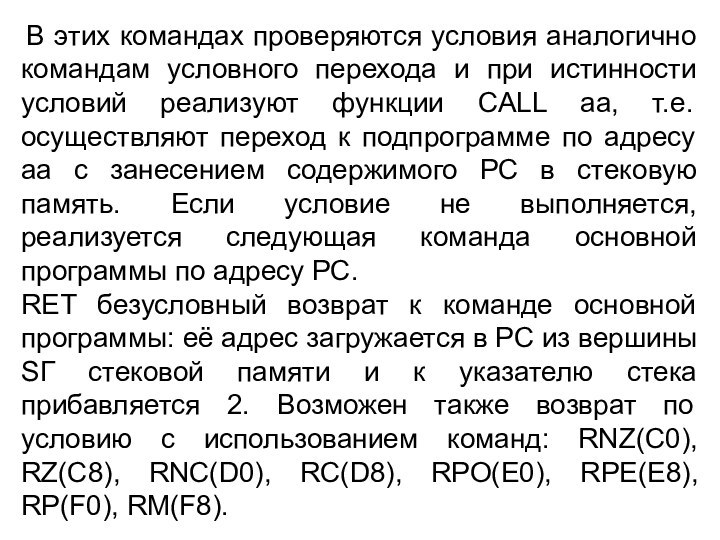

- 65. В этих командах проверяются условия аналогично

- 66. Команды ввода/вывода из периферийных устройств и организации

- 67. PUSH RP помещает содержимое регистровой пары RP

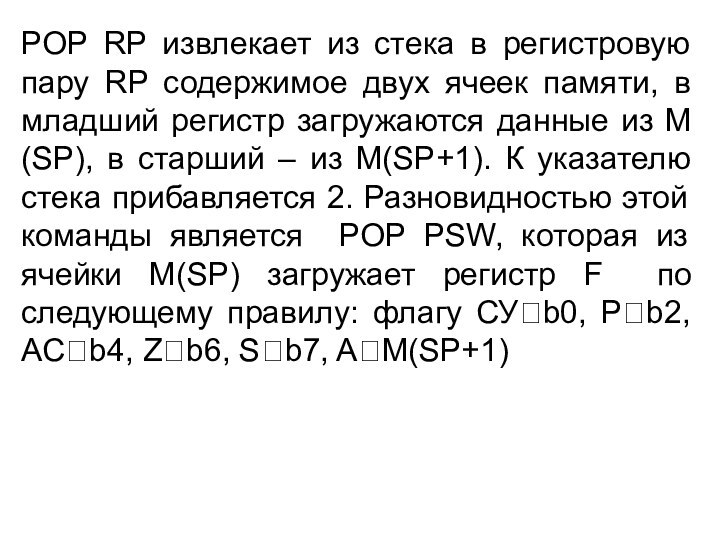

- 68. POP RP извлекает из стека в регистровую

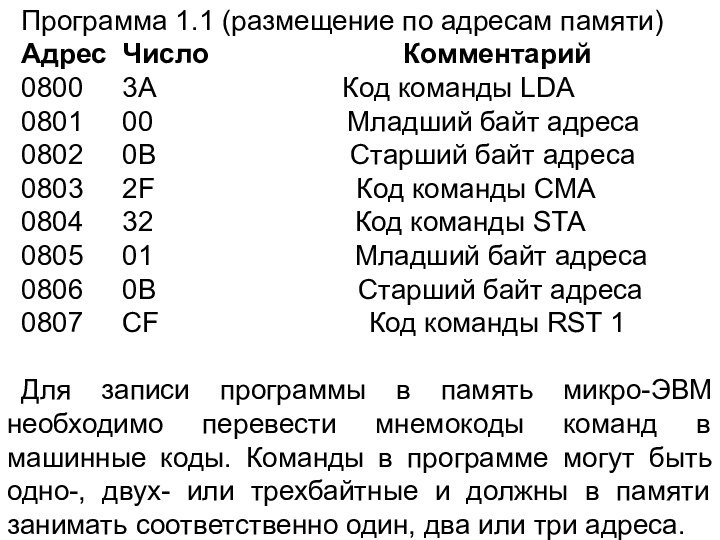

- 70. Программа 1.1 (размещение по адресам памяти)Адрес Число

- 71. Предварительную запись программ удобно проводить в более

- 72. Программа 1.2 Адрес Машинный Метка Мнемокод

- 73. Скачать презентацию

- 74. Похожие презентации

![Микропроцессор. Устройство и принцип действия ЭВМ. (Лекция 2) Рис. 2. Структурная схема микропроцессорной системы на основе МП КР580ВМ80 [1]. Конструктивно](/img/tmb/15/1459329/e54ac71a70ed7205afd71f9fb72d47c0-720x.jpg)

Слайд 2

Микропроцессор.

Структурная схема микроЭВМ.

Система команд микроЭВМ.

Организация

памяти МП-системы.

Слайд 3 С развитием технологии и схемотехники цифровых интегральных схем

появилась возможность создавать сложные устройства обработки цифровой информации в

виде компактных микросхем. Однако увеличение сложности реализуемого алгоритма обработки, как правило, сужает область его применения. Устранить противоречие между сложностью БИС и ее универсальностью удалось за счет программирования выполняемых микросхемой функций. В программируемых БИС потребитель может путем подачи определенных командных сигналов задать один из возможных режимов работы. Основным типом программируемых БИС являются БИС микропроцессоров. Микропроцессор (МП) ‑ это программно-управляемое устройство обработки информации, выполненное в виде одной или нескольких БИС.

Слайд 4

Рис. 1. Схемы, поясняющие принцип построения микропроцессорных систем.

Запоминающее

устройство, которое на рис. 1а было показано в виде

одного блока, на рис. 1б представлено двумя блоками: постоянным запоминающим устройством (ПЗУ) и оперативным запоминающим устройством (ОЗУ). ПЗУ служит для хранения неизменяемой части программы и может работать только в режиме выдачи информации. ОЗУ используется для хранения промежуточных данных и может не только принимать на хранение, но и выдавать записанную ранее информацию.Слайд 5 Для того чтобы согласовать устройства ввода-вывода информации с

магистралью, служат адаптеры ввода-вывода (АВВ) рис. 1б. Магистраль обычно

снабжается буфером магистрали (БМ), увеличивающим ее нагрузочную способность, или адаптером магистрали, но и преобразовывать сигналы.Рис. 1б показывает набор основных функциональных блоков, входящих в микропроцессорную систему (МП-систему). Каждый из этих блоков может состоять из одной или нескольких БИС. Существуют также однокристальные микро-ЭВМ, сконструированные таким образом, что одна микросхема содержит в том или ином виде все блоки, необходимые для построения МП-системы. Совокупности БИС, имеющих единые принципы организации и позволяющим строить на их основе функционально законченные МП-системы, называют обычно микропроцессорными наборами.

Слайд 6 Микропроцессорные наборы, совместимые по принятым системам команд, уровням

сигна-лов, принципам передачи сигналов по магистралям, носят название микропроцес-сорных

семейств. Широко известны за рубежом, например, МП-семейства типов 8080 и 6800. Первое семейство включает в себя МП-наборы типов 8080, 8085, Z80, 8088, 8086, Z8001, второе ‑ МП-наборы типов 6800, 6802, MD46802, 6809, 68000. Отечественные аналоги микропроцессоров 8080, 8085, 8088 ‑ это МП типов КР580ВМ80, КМ1821ВМ85, КР1810ВМ88.Слайд 7 Наибольшей популярностью пользуется МП серии К580 ‑ аналог

8080. В значительной степени это, вероятно, объясняется его доступностью

и наличием хороших описаний в технической литературе. За рубежом широко применяются более развитые представители семейства 8080, и в частности МП Z80 (в Германии выпускается его аналог U880). Отечественная промышленность также выпускает достаточно совершенные МП семейства 8080. Сюда относятся 8-разрядный микропроцессор типа КР1821ВМ85 (аналог 8085) и 16-разрядные МП КР1810ВМ86 (аналог 8086) и КР1810ВМ88 (аналог 8088).Слайд 8 В конце 1973 года фирма Intel выпустила микро-процессор

8080, который синхронизировался тактовой частотой 2 МГц. Он мог

адресовать к 64 Кб ячейкам памяти и работать с 8-разрядной шиной данных. На его основе фирма IBM выпустила в 1975 г. первую персональную ЭВМ модели 5100, которая стоила 9000 дол., и поэтому была недоступна многим пользователям. В 1976 г. новая компания Apple Computer выпускает ЭВМ Apple I, а через год вторую модель стоимостью 1 600 дол., имевшую большой успех на рынке. В СССР был изготовлен аналог МП 8080 микропроцессор КР580 (ИС КР580ВМ80А, КР580ИК80А), на котором были построены первые отечественные персональные ЭВМ типа СМ-1800. Эти и другие ранние компьютеры использовали операционную систему CP/M.

Слайд 9

Состав МПК БИС К580

Тип БИС

Наименование

КР580ВМ80 Микропроцессор

КР580ВВ55 Программируемый параллельный интерфейс

КР580ВВ51 Программируемый последовательный интерфейс

KP58GBH59 Программируемый

контроллер прерыванийКР580ВИ53 Программируемый таймер

KF58DBKT8 Системный контроллер

КР580ГФГ*] Генератор тактовых сигна пов

КР580ВТ57 Контроллер прямого доступа к памяти

КР580ВВ79 Программируемый интерфейс клавиатуры и индикации

КР580ВГ72 Контроллер КГМД

КР580ВГ75 Контроллер видеотерминала

КР580ВАВ6 Шинный формирователь

Слайд 10 Отдельные задачи измерительной тех-ники могут эффективно решать однокристальные

8-разрядные микро-ЭВМ серии К1816 (аналог MDS-48) и од-нокристальная микро-ЭВМ

КМ1813ВЕ1 со встроенными 4-канальным АЦП и 8- канальным ЦАП (аналог 2920 “Интел”). МП КР580ВМ80А является аналогом известного МП 8080А, разработанного фирмой “Интел” (США). Он изготавлива-ется по n-канальной МОП-технологии, позволяющей получить высокую степень интеграции компонентов на одном крис-талле.Слайд 11 В 1981 г. фирма IBM выпустила на базе

микро-процессора 8088 первую модель нового персо-нального компьютера РС с

операционной системой MS-DOS фирмы Microsoft, которую прекратила выпускать в 1987 г. Микропроцессор Intel 8088 адресует к 1 Мб ячейкам памяти и является аналогом 8086 с той лишь разницей, что имеет 8-разрядную внешнюю шину данных. Тактовая частота микропроцессора 8088, равная 4.77 МГц, позволяет в два раза увеличить быстродействие РС по сравнению с моделями ЭВМ на кристалле 8080.Слайд 12 Модель РС использовала до двух внешних накопителей на

гибких магнитных дисках емкостью 360 Кб и 83-клавишную клавиатуру.

Взаимодействие между блоками РС осуществлялось при помощи стандартной внешней шины ISA. Компьютеры с шиной ISA часто называют классическими персональными компьютерами семейства PC-XT. На системной плате РС устанавливался микропроцессор 8088, сопроцессор 8087, ОЗУ динамического типа с временем доступа 200 нс и емкостью от 64 до 256 Кб с контролем на четность. Кроме того, на системной плате в ПЗУ "зашит" встроенный интерпретатор Бейсика, система ввода/вывода BIOS и программа самопроверки при включении POST.Слайд 13 Упрощенная структурная схема, этого МП КР580ВМ80 построенная на

его основе МП-системы показана на рис. 2. В данном

случае МП выполняет роль центрального процессорного устройства (ЦПУ). Ограниченность энергии, которая может быть рассеяна в кристалле, не позволяет обеспечить достаточную нагрузочную способность выходов МП. Поэтому в большинстве случаев требуется включение внешних буферов. Внешняя магистраль в рассматриваемой системе представлена тремя отдельными шинами: шиной данных (ШД), шиной управления (ШУ) и шиной адреса (ША). Соответственно предусмотрены три буфера: буфер шины данных (БШД), буфер шины управления (БШУ), буфер шины адреса (БША).

Слайд 14

Рис. 2. Структурная схема микропроцессорной системы

на основе

МП КР580ВМ80 [1].

Конструктивно шины выполняются в виде набора

проводов или печатных проводников, соединяющих выводы БИС или контакты разъемов, к которым подключаются модули МП-системы. МП 8080 оперирует с восьмиразрядными словами данных. Поэтому ШД здесь состоит из восьми отдельных проводников, по которым передаются двоичные сигналы. Уровни этих сигналов соответствуют стандартным уровням ТТЛ-схем.Слайд 15 Шина данных в МП-системе ‑ двунаправлен-ная. Информация по

ней может передаваться как в ЦПУ, так и из

ЦПУ. Направление передачи по ШД устанавливает ЦПУ.Шина управления в рассматриваемой системе состоит из набора отдельных проводников, каждый из которых предназначен для передачи определенного сигнала в определенном направлении. МП 8080 выполнен в корпусе, имеющим 40 выводов. Это оказывается недостаточным для того, чтобы предоставить каждому сигналу управления отдельный вывод.

Слайд 16 Поэтому часть сигналов управления передается по выводам шины

данных в режиме разделения времени. Этим объясняется соединение на

схеме рис. 2 буфера шины управления как с внутренним устройством управления (УУ), так и с шиной данных.Слайд 17 Разрядностью шины адреса (ША) определяется предельно возможный объем

памяти, которой может быть укомплектована МП-система. Чем больше объем

памяти, тем более сложные программы может реализовать система и тем мощнее ее вычислительные и управляющие возможности. МП типа 8080 имеют 16-разрядную адресную шину. Это означает, что ЦПУ может адресоваться к 216 = 65536 ячейкам памяти. Учитывая, что по каждому адресу может храниться 8-разрядное слово (1 байт), получаем, что предельный объем памяти составляет в данном случае 64 КБайт (1 Кбайт = 1024 байт). Шина адреса ‑ однонаправленная, код адреса из ЦПУ поступает на ПЗУ, ОЗУ и АВВ.Слайд 18 Внутренняя функциональная схема МП 8080 на рис. 2

показана предельно схематично. Обозначены в основном лишь те узлы,

ссылки на которые имеются в системе команд. В состав МП входит арифметико-логическое устройство (АЛУ), способное выполнять простейшие арифметические и логические операции с одним или двумя кодовыми словами. Один из операндов (или единственный операнд), над которыми производится действие в АЛУ, как правило, хранится в регистре-аккумуляторе (RG A). В этот же регистр передается результат выполнения операции. В АЛУ имеются также регистры временного хранения операндов, которые на рис. 2 не показаны.Слайд 19 Непосредственно к АЛУ примыкает регистр флажков (RG F),

в котором хранится информация (5 разрядов) о признаках, характеризующих

результат, полученный в АЛУ после выполнения очередной операции. Эти признаки представлены следующими битами:1. битом переноса (С),

2. битом дополнительного переноса (ас),

3. битом знака (S),

4. битом нулевого признака (Z),

5. битом четности (P).

Слайд 20 Бит переноса устанавливается равным 1 при переносе из

старшего разряда (переполнение разрядной сетки). Дополнительный перенос ‑ это

перенос из младшего полубайта в старший. Информация об этом переносе нужна при переводе двоичных чисел в двоично-десятичные. Бит знака равен 1 тогда, когда в 7-м (старшем) разряде результата операции присутствует единица (отрицательные числа в ЦПУ представлены в дополнительном коде). Если Z = 1, то это означает, что получен нулевой результат. И, наконец, бит четности, равный единице, указывает на то, что в полученном результате содержится четное число кодовых единиц.Слайд 21 Не все операции, выполняемые в АЛУ, воздействуют на

содержание регистра флажков. Этот факт следует учитывать при программировании

условных переходов по состоянию отдельных разрядов регистра F. Содержание регистра F дополняется до стандартного 8-разрядного размера тремя постоянными нулями.Входящие в МП восьмиразрядные регистры общего назначения B, C, D, E, H, L играют роль сверхоперативного запоминающего устройства. Эти регистры могут использоваться отдельно и в виде 16-разрядных регистровых пар BC, DE, HL, называемых в командах по имени первых регистров B, D, H, содержащих старшие байты чисел.

Слайд 22 Шестнадцатиразрядный регистр SP (stack pointer) ‑это указатель стека,

т.е. регистр, информация в котором указывает адрес очередной свободной

ячейки стековой памяти. Стековая, или магазинная, память работает по принципу ”последний вошел, первый вышел”. Программист выделяет область ОЗУ, отводимую под стек, и помещает в регистр SP адрес последней ячейки этой области (в рассматриваемом МП стек заполняется с конца). Затем при необходимости по ходу выполне-ния программы на хранение в стек могут быть отп-равлены 16-разрядные кодовые слова из регистро-вых пар AF, BC, DE, HL . Каждое такое слово зани-мает две восьмиразрядные ячейки памяти с адреса-ми (SP) и (SP) ‑ 1, где (SP) ‑ содержимое регистра SP.Слайд 23 Соответственно при помещении в стек очередного слова содержимое

регистра SP автоматически уменьшается на 2. Затем при чтении

каждого записанного в стек слова содержимое регистра SP увеличивается на 2. Операции со стеком удобны тем, что реализуются короткими однобайтными командами и программисту не нужно в командах указывать адреса ячеек памяти, куда записывается или откуда читается информация. Однако нужно учитывать, в каком порядке слова были направлены в стек, так как при чтении они будут выдаваться в обратном порядке.Слайд 24 Показанный на схеме рис. 2 16-разрядный регистр PC

(programm counter) ‑ это программный счетчик. Слово, записанное в

регистре PC, выводится на 16-разрядную адресную шину и определяет, таким образом, адрес ячейки памяти, к которой в данный момент производится обращение. После выполнения каждой команды, за исключением команд переходов, число, записанное в PC, увеличивается на число единиц, равное числу байтов в коде этой команды. При выполнении команд переходов, содержимое PC может изменяться скачком.Слайд 25 Устройство управления УУ, входящее в состав МП (рис.

2), обеспечивает правильное функ-ционирование всех внутренних узлов ЦПУ, выдает

командные сигналы на внешнюю шину управления и воспринимает сигналы с этой шины.Функциональные узлы ЦПУ соединены между собой внутренней шиной данных, с помощью которой они могут обмениваться инфор-мацией. Шины данных и адреса, выходящие из ЦПУ, могут быть переведены в высокоимпедансное состояние (внутренние буфера этих шин на рис. 2 не показаны).

Слайд 27 Буферные регистры W,Z не являются программно доступными регистрами

и используются для выполнения команд внутри МП БИС.

Регистр команд

РгК и дешифратор команды ДШК используются в МП БИС для получения и дешифрации кода команды. При извлечении команды первый байт, содержащий ее код, помещается в регистр команды и поступает на дешифратор команд. Дешишифратор совместно с устройством управления и синхросигналами Ф1 и Ф2 формируют управляющие сигналы для всех внутренних блоков МП БИС, а также его выходные сигналы управления и состояния.Слайд 28 Выполнение каждой команды производится в МП БИС в

строго определенной последовательности, определяемой кодом команды, и синхронизируется во

времени сигналами Ф1 и Ф2 тактового генератора.Период синхросигналов CLK1 и CLK2 называется МАШИННЫМ ТАКТОМ (Т). Длительность машинного такта Т может быть установлена произвольно в диапазоне от 0.5 до 2 микросекунд. При использовании МП БИС необходимо ясно представлять динамику его работы, т.е. на каких магистралях, в зависимости от каких управляющих сигналов и когда МП БИС будет выдавать ту или иную информацию. Это в дальнейшем поможет понимать работу схем, позволяющих согласовывать ее с различными периферийными устройствами микро-ЭВМ.

Слайд 29

При анализе процессов будем использовать следующие понятия:

Машинный цикл

(М)-время , требуемое для извлечения из памяти один байт

информации или выполнение команды, определяемой одним машинным словом. Машинный цикл может состоять из 3-5 машинных тактов. Время выполнения команды - время получения, декодирования и выполнения команды.В зависимости от вида команды это время может состоять из 1-5 машинных циклов. Для МП БИС КР580ИК80 существует 10 различных типов машинных циклов:

Слайд 30

1. Извлечение кода команды (М1).

2. Чтение данных из

памяти.

3. Запись данных в память.

4. Извлечение из стека.

5. Запись

данных в стек.6. Ввод данных из внешнего устройства.

7. Запись данных во внешнее устройство.

8. Цикл обслуживания прерывания.

9. Останов.

10. Обслуживание прерываний при работе МП БИС в режиме останова.

Тип выполняемого цикла МП указывает на первом такте каждого машинного цикла с помощью 8-разрядного слова состояния, выдаваемого на ШД.

Слайд 31 Отдельные разряды слова состояния задей-ствуются в микро-ЭВМ для

формирования магистрали управления. Слово состояния выдается на ШД лишь

на интервале синхросигналов С (такты Т1 и Т2), а используется на протяжении всего машинного цикла, поэтому необходимо записать его в специальный регистр слова состояния РгСС.Запись осуществляется с использованием сигнала “Синхро” и тактового импульса Ф1. Сигнал “Синхро” появляется в начале каждого цикла и занимает промежуток времени между положительными фронтами тактового импульса Ф2 на тактах Т1 и Т2. Таким образом, запись слова состояния осуществляется сигналом Ф1 на такте Т2.

Слайд 32 1. Извлечение кода команды или данных из памяти

или внешнего устройства.

Цикл М1 является основным циклом с которого

начинается выполнение любой команды, поэтому временные процессы для него рассмотрим более подробно. Анализ процессов будем проводить по каждому машинному такту Т (рисунок 5).На такте Т1 программный счетчик МП выдает на ША адрес ячейки памяти, из которой будет считываться код команды. При этом схема приращения адреса МП автоматически увеличивает на единицу значение числа, записанного в программном счетчике. Положительным фронтом тактового импульса Ф2 формируется сигнал “Синхро” и выдается слово состояния на ШД. Сигнал “Прием”, управляющий двунаправленным шинным формирователем (ШФ) шины данных (рисунок 6), на этом такте равен нулю, что позволяет слову состояния поступить на ШД процессора.

Слайд 34 На такте Т2 слово состояния записывается в регистр.

Положительным фронтом Ф2 заканчивается сигнал “Синхро” и формируется единичный

сигнал “Прием”, позволяющий данным поступить на вход МП через ШФ.На такте Т2 из сигнала “Прием” и седьмого разряда слова состояния (Д7) формируется сигнал на чтение данных из памяти (Чт. памяти), позволяющий данным поступать из памяти на ШД (см. рисунок 5 ). На этом же такте анализируется состояние сигналов “Готов” и “Захват”. При нулевом сигнале на входе “З.Зх” и единичном сигнале на входе “Готов” МП переходит к выполнению такта Т3.

Слайд 35 Если к моменту появления отрицательного фронта Ф2 на

такте Т2 сигнал на входе “Готов” будет иметь нулевой

потенциал, то МП на такте Т3 переходит в режим ожидания. В этом режиме приостанавливается процесс обработки данных и формируется единичный сигнал на выходе “Ожидание”, подтверждающий это состояние. Время ожидания выражается целым числом тактов и может длиться бесконечно долго. На каждом такте в этом режиме при отрицательном фронте Ф2 будет проверяться состояние сигнала на входе “Готов”.Слайд 36 На такте Т3 в момент отрицательного фронта сигнала

Ф1 производится запись данных во внутренний регистр кода команды.

Положительным фронтом Ф2 снимается сигнал “Прием” на выходе МП и, следовательно, сигнал “Чт. памяти”.На последующих тактах Т4 и Т5 . дешифратор кода команды расшифровывает код команды, определяет количество байтов в команде, формирует команды на внутренние пересылки данных и подготавливает МП к выполнению следующих машинных циклов.

Слайд 37 Отличие машинных циклов чтения данных из памяти или

внешнего устройства будет заключаться лишь в том, что МП

будет воспринимать числа, полученные на такте Т3 по ШД не как код команды, а как данные. При приеме данных из внешнего устройства на ШУ формируется сигнал чтение устройства ввода-вывода (Чт.ВУ) из сигнала “Прием” и разряда Д6 регистра состояния. Этот сигнал позволяет именно ВУ выдать информацию на ШД процессора.

Слайд 38

2. Запись данных в память или внешнее устройство.

На

такте Т1 содержимое регистра адреса МП выдается на ША,

а на ШД выдается слово состояния.На такте Т2 на ШД выдаются данные для записи в память.

На такте Т3 формируется сигнал “Запись”, по которому будет проходить запись данных в память или ВУ.

На протяжении всего машинного цикла записи данных в память сигнал “Прием” находится на нулевом уровне, что позволяет двунаправленному шинному формирователю работать в режиме выдачи данных на ШД МП.

Процесс записи данных во внешнее устройство аналогичен записи данных в память. Единственное отличие этого процесса заключается в том, что вместо сигнала “Зп.память” формируется сигнал “Зп.в ВУ”, т.е. в первом случае выполнялась сборка по “И” для сигналов “Запись” с МП и “Память” с РгСС, а во втором - сборка по “И” для сигналов “Запись” и “Вывод”.

Слайд 39

Начальная установка.

В течение всего времени, пока входе R

установлен уровень “1”, все операции в МП будут приостановлены.

За это время обнуляются программный счетчик, триггер разрешения прерывания.Следовательно, первая выполняемая команда будет считываться по адресу 0000.

После начала выполнения программы прерывания остаются отключенными. Для восстановления возможности восприятия запросов прерывания в программу необходимо включить команду EI.

Слайд 40 Режимы работы МП-системы. МП-система ‑ это, в конечном

счете, цифровой автомат, который выполняет операции с цифровой информацией

в соответствии с хранящейся в памяти программой. Поэтому работа по программе и является основным режимом работы такой системы.После начального запуска (сброса) в программном счетчике (регистр РС) устанавливается число 0000Н. Буква Н в конце числа указывает, что число представлено в шестнадцатеричном коде, т. е. отношение весов данного и соседнего младшего разрядов числа равно 16 (в шестнадцатеричном коде используются цифры 0 ‑ 9, а также буквы A ‑ F латинского алфавита, соответствующие десятичным числам 10 ‑ 15).

Слайд 41 Установка в состояние 0000Н регистра РС приведет к

тому, что на адресную шину будет выдан адрес 0000Н

и ЦПУ произведет чтение байта информации, хранящегося в ячейке памяти, расположенной по этому адресу. Содержимое этого байта будет расшифровано в ЦПУ как код соответствующей операции. Получив код операции (КО), ЦПУ определяет число байт, которое должно содержать полный код команды. В рассматриваемом микропроцессоре команды бывают одно-, двух- и трехбайтные, причем по содержанию кода операции МП однозначно устанавливает длину кода команды. Если команда описывается двумя или тремя байтами, то ЦПУ считывает недостающие один или два байта из последующих ячеек памяти.Слайд 42 Микропроцессор БИС КР580ВМ80 имеет фиксированный набор команд. Время

выполнения команды определяется процессом получения, декодирования и выполнения команды.

Его можно представить состоящим из ряда временных интервалов. Наиб. короткий, равный периоду синхросигналов МП БИС, называется машинным тактом. Время, необходимое для извлечения 1 байт информации из памяти или внешнего устройства или выполнения команды, определяется одним машинным словом, называется машинным циклом.Слайд 43 Ряд команд МП предусматривает обработку или передачу чисел

двойной длины. В этих случаях пары регистров В и

С, D и Е или Н и L объединяются в 16-разрядные регистрыК двухбайтным командам в МП относятся команды с непосредственной адресацией и команды ввода-вывода. Соответственно второй байт команды этой группы содержит 8-разрядный операнд или 8-разрядный адрес устройства ввода или вывода.

Слайд 44 В трехбайтных командах второй и третий байты содержат

16-разрядные адреса (в командах с прямой адресацией) или 16-разрядные

операнды (в командах загрузки регистровых пар и указателя стека).После выполнения каждой операции а АЛУ вырабатывается пять признаков, значения которых могут влиять на выполнение последующих команд обработки информации и условной передачи управления. Однако следует иметь ввиду, что различные команды по-разному влияют на отдельные признаки.

Слайд 45 Для удобства сохранения и восстановления состояния МП во

время прерываний и перехода к подпрограммам все указанные признаки

сохраняются в специальном регистре - регистре признаков. Расположение признаков в разрядах регистра приведено в таблице.где S - признак “знака” (принимает значение старшего разряда

результата);

Z - признак нулевого результата;

АС -признак вспомогательного переноса (если есть перенос

между тетрадами байта, то АС=1, иначе АС=0;

Р - признак четности результата (если число единиц в байте

результата четно, то Р=1, иначе Р=0);

С - признак переноса или заема (если при выполнении коман-

ды возник перенос из старшего разряда или заем в стар-

ший разряд то С=1, иначе С=0).

Слайд 46 Для ускорения вычислений некоторые операнды хранятся в блоке

РОН. Команды, работающие с этими операндами, используют укороченные адресные

коды (регистровую адресацию).Эти команды позволяют исключить сравнительно длинный цикл обращения к ОЗУ и тем самым существенно повысить скорость выполнения операций. В связи с ограниченной разрядностью РОН и при работе с большим массивом данных, используются другие методы адресации, которые позволяют обращаться к операндам, расположенным во внешней по отношению к МП памяти. Наиболее распространенной является косвенная регистровая адресация, которая использует регистровую пару HL.

Слайд 47

3. Система команд микроЭВМ.

Последовательность (закон) преобразования информации

в ЭВМ задается программой. Программа размещается в ОЗУ в

виде команд, представленных в машинных кодах. Представление программ в машинных кодах требует много времени на ввод команд и их проверку. Поэтому для уменьшения времени на программирование, вероятности ошибок кодирования, повышения наглядности представления команд для задания закона преобразования информации используется машинно-ориентированный язык Ассемблер. Поскольку различные микроЭВМ отличаются структурой и конструктивными особенностями, изменяется содержание и языка Ассемблер.Слайд 48 Поэтому в зависимости от разновидности операции и участвующих

в ней устройств в микроЭВМ используются 1-, 2- и

3-байтные команды. В 1-байтной команде 5 разрядов отводится под КОП и 3 разряда – под адрес устройства микропроцессора. В 2- и 3-байтных командах под поле КОП отводится первый байт команды. Вторые и третьи байты используются или под операнд (непосредственная адресация), или под код адреса ячейки в ПЗУ или ОЗУ (прямая адресация).Слайд 49 Отличительной особенностью команды условного перехода от команд управления

безусловного перехода является проверка значения логического условия в соответствии

с типом команды перед последней микрооперацией передачи содержимого группы регистров W и Z в РС. Если условие выполняется, то содержимое из W,Z передается в РС; если нет, то содержимое остается адресом следующей команды. Содержимое РС затем передается в РА.Слайд 50 Буферные регистры W,Z не являются программно доступными регистрами

и используются для выполнения команд внутри МП БИС.

Слайд 51 Кроме двоичной системы, в ЭВМ часто используется шестнадцатеричная

система счисления. Более компактная запись чисел в этой системе

позволяет уменьшить вероятность ошибок и увеличить скорость ввода информации, уменьшить число индикаторов контроля правильности преобразования информации и расширить диапазон представления чисел. В этой системе алфавит состоит из 16 символов: 0,...,9,A,B,C,D,E,F, каждый из которых может быть размещен в одной из позиций числа. Ввиду кратности оснований систем счисления правила перевода чисел из двоичной системы счисления в шестнадцатеричную и обратно весьма просты.Слайд 52 Сначала двоичное число разбивается на тетрады, затем каждая

тетрада заменяется соответствующим шестнадцатеричным сим-волом. Например, разбиение целого числа

11110111 на тетрады справа налево даст 1111 0111, а в результате замены шестнадцатеричным эквивалентом полу-чаем число F7(16). Обратное преоб-разование шестнадцатеричного числа осуществляется заменой символов 0,1,...,F тетрадами двоичного эквивалента. Например, 6FD(16)= 0110 1111 1101(2) .

Слайд 53

Команды передачи данных

Первая группа команд обеспечивает выполнение операций

размещения, обмена, загрузки и перемещения данных. Число команд –

84. Наибольшее число команд пересылки типа MOV Ri,Rj. Команды однобайтные, предназначены для пересылки операндов из одного регистра в другой или обмена информацией между РОН и ОЗУ. Например, команда MOV A,B имеет код 78(16) (дополнение к таблице 5.1); адресация – регистровая, выполняет операцию передачи содержимого регистра B в регистр A (A⇐B).Слайд 54 Команды MOV M,Rj осуществляют передачу содержимого одного из

РОН в ячейку памяти с адресом, указанным в регистровой

паре H,L. Поэтому перед выполнением данных команд необходимо предварительно помес-тить младший байт адреса ячейки М в регистр L, старший байт адреса в регистр H.Слайд 55 Команды MOV Ri,M осуществляют передачу содержимого ячейки памяти

М с адресом, указанным в регистровой паре H,L, в

один из РОН.Рассмотрим назначение других команд:

MVI Ri,V осуществляют непосредственную передачу операнда, находящегося во втором байте команды, в РОН или ячейку памяти.

MVI B,V (код – 06(16)) загружает в регистр В второй байт команды, равный V.

Слайд 56 MVI M,V (код – 36(16)) осуществляет непосредственную передачу

второго байта команды V в ячейку с адресом, указанным

в регистровой паре H,L.LDA аа осуществляет прямую загрузку аккумулятора содержимым ячейки памяти с адресом аа, причем второй байт команды – младшие разряды адреса, третий байт – старшие.

STA аа осуществляет передачу содержимого аккумулятора в ячейку с адресом аа , т.е. М (байт3, байт2)⇐А.

Слайд 57 LHLD аа загружает регистровую пару H,L содержимым ячеек

памяти с адресами аа, аа+1, т.е. Н⇐М (аа+1), L⇐М

(аа).LDAX B, LDAX D загружают аккумулятор содержимым ячейки по адресу, находящемуся в регистровой паре B,C; D,E соответственно.

STAX B, STAX D передают содержимое аккумулятора в ячейку памяти по адресу, находящемуся в регистровой паре B,C; D,E соответственно.

XCHG осуществляет обмен данными между регистрами H и D, L и E.

SHLD аа загружает две соседние ячейки памяти содержимым регистров H,L: М(байт3, байт2 = аа(16))⇐L, М(аа+1)⇐H.

Слайд 58

Арифметические команды

Эти команды предназначены для выполнения операции сложения,

сложения с переносом, вычитания, вычитания с заёмом, инкрементирования, декрементирования,

десятичной коррекции аккумулятора. В большинстве случаев эти команды изменяют содержимое разрядов регистра флажков F, который содержит информацию следующего вида:S – индикатор знака;

Z – нуля;

AC – вспомогательного переноса;

P – четности;

CУ – переноса.

Слайд 59

Рассмотрим команды этой группы:

ADD Ri осуществляет сложение в

прямых кодах содержимого аккумулятора и операнда, находящегося в РОН

или ячейке памяти.ADD B (код – 80(16)) выполняет операцию А=А+В без учета знака, результат сложения остается в А.

ADD M (код – 86(16)) складывает содержимое аккумулятора с операндом ячейки памяти по адресу, указанному в регистровой паре H,L.

Слайд 60 ADI V выполняет сложение в АЛУ аккумулятора с

операндом в команде, результат сложения заносит в А. В

данной команде в первом байте располагается КОП, во втором – операнд V.ADC Ri складывает содержимое А с РОН или ячейкой памяти и в младший разряд сумматора АЛУ прибавляет содержимое младшего разряда регистра F.

Слайд 61

Логические команды

Задачей этих команд является выполнение поразрядной конъюнкции,

дизъюнкции , сложения по модулю 2, сравнения содержимого А

и Ri или А и V, а также циклического сдвига операндов в А (таблица 5.1). Например, команда XRA M (код – AE(16)) осуществляет сложение по модулю 2 содержимого ячейки памяти М, расположенной по адресу, находящемуся в H,L, с аккумулятором, результат операции размещает в А.

Слайд 62

Команды передачи управления

Четвертая группа команд содержит команды перехода,

вызова, возврата и повторного запуска. Эта группа предназначена для

изменения естественного порядка следования команд.JMP aa безусловный переход к команде, находящейся в ячейке (байт3, байт2 = аа). Второй и третий байты команды загружаются в W,Z и затем в РС, а через регистр адреса команда извлекает очередную необходимую команду программы.

JNZ аа извлекает команду аналогично JMP только при Z=0, в противном случае извлекается следующая по порядку команда, PC=PC+1.

JZ aa извлекает команду по адресу aa при Z=1, а при Z=0 по адресу РС=(РС*+1), т.е. по состоянию счетчика команд на 3 больше адреса предыдущего РС*.

Слайд 63 CALL aa выполняет безусловный переход на аа(16) =

(байт3, байт2) команды. При этом прерванный адрес в счетчике

команд РС=(РСН,РСL) следующий за CALL команды запоминается занесением в стековую память: в ячейку памяти М(SP-1) заносятся старшие разряды РСН, в ячейку М(SP-2)=PCL младший байт РС, значение указателя стека SP уменьшается за два цикла на 2.Слайд 64 Данная команда осуществляет безусловный переход на аа, однако

часто требуется переход к подпрограмме в зависимости от состояния

регистра F. Для этой цели используются следующие разновид-ности команды CALL аа:CNZ аа(С4), CZ аа(СС), CNC аа(D4), CC aa(DC), CPO aa(E4), CPE aa(EC), CP aa(F4), CM aa(FC).

Слайд 65 В этих командах проверяются условия аналогично командам

условного перехода и при истинности условий реализуют функции CALL

aa, т.е. осуществляют переход к подпрограмме по адресу аа с занесением содержимого РС в стековую память. Если условие не выполняется, реализуется следующая команда основной программы по адресу РС.RET безусловный возврат к команде основной программы: её адрес загружается в РС из вершины SГ стековой памяти и к указателю стека прибавляется 2. Возможен также возврат по условию с использованием команд: RNZ(C0), RZ(C8), RNC(D0), RC(D8), RPO(E0), RPE(E8), RP(F0), RM(F8).

Слайд 66

Команды ввода/вывода из периферийных устройств и организации прерываний

Последняя

группа команд выполняет операции помещения в стек и извлечения

из него, ввода и вывода данных, обмена данными, подтверждения и неподтверждения прерываний, управления отсутствием операций и останова, установления маски прерываний.IN aр вводит данные в А из порта периферийного устройства, адрес которого определяется вторым байтом команды.

OUT ap выводит данные из А в порт, адрес которого определяется вторым байтом команды.

Слайд 67 PUSH RP помещает содержимое регистровой пары RP в

стек. В ячейку М(SP-1) помещает значение старшего регистра, в

М(SP-2) – значение младшего регистра пары, указатель стека дважды декрементируется SP=SP-2. Разновидностью этой команды является команда занесения в стек слова состояния процессора PUSH PSW, которая помещает в М(SP-1) содержимое А, а в ячейку М(SP-2) содержимое F, причем разрядам ячейки М(SP-2) присваиваются b0СУ, b2P, b4АС, b6Z, b7S.Слайд 68 POP RP извлекает из стека в регистровую пару

RP содержимое двух ячеек памяти, в младший регистр загружаются

данные из М(SP), в старший – из М(SP+1). К указателю стека прибавляется 2. Разновидностью этой команды является POP PSW, которая из ячейки М(SP) загружает регистр F по следующему правилу: флагу СУb0, Pb2, ACb4, Zb6, Sb7, AM(SP+1)Слайд 69

Программа 1.1 (в мнемокодах)

Мнемокод

Комментарий LDA 0В00 Получить число из адреса 0В00.

CMA Инвертировать число.

STA 0В01 Записать результат по адресу 0В01.

RST 1 Прервать выполнение программы.

При записи программ все числа представляются в шестнадцатеричной системе счисления.

Слайд 70

Программа 1.1 (размещение по адресам памяти)

Адрес Число

Комментарий

0800 3А Код команды LDA

0801 00 Младший байт адреса

0802 0В Старший байт адреса

0803 2F Код команды СМА

0804 32 Код команды SТА

0805 01 Младший байт адреса

0806 0В Старший байт адреса

0807 СF Код команды RSТ 1

Для записи программы в память микро-ЭВМ необходимо перевести мнемокоды команд в машинные коды. Команды в программе могут быть одно-, двух- или трехбайтные и должны в памяти занимать соответственно один, два или три адреса.

Слайд 71 Предварительную запись программ удобно проводить в более компактной

форме. В программе указывается начальный адрес каждой команды и

при этом понимается, что в зависимости от длины (одно-, двух-, трехбайтная) команды в памяти будут занимать от одной до трех последовательных ячеек. При такой записи в левом столбце указываются лишь адреса команд в программе. Это позволяет сократить объем при описании программ и сделать более простым их анализ. В программе 1.1 используется прямой способ адресации.Программа 1.1 (общий вид записи)

Адрес Машинный Метка Мнемокод Комментарий

код

0800 3А 000В LDА,0В00 Получить число

0803 2F CMA Инвертировать число

0804 32 010В SТА,0В01 Записать по адресу 0В01

0807 СF RST 1 Прервать выполне- ние программы

Слайд 72

Программа 1.2

Адрес Машинный Метка Мнемокод

Комментарий

код0800 21 000В LXT H,0В00 Записать в регистры HL число

0В00 H

0803 7Е МОV А,М Получить число из адреса,

указанного в регистрах HL

0804 2F СМА Инвертировать число

в аккумуляторе

0805 23 INX H Увеличить на 1 число в

регистрах Н,L

0806 77 МОV М,А Записать число из аккумулято-

ра по указан ному адресу в Н,L

0807 СF RST 1 Прервать выполнение

программы