Pentium II: 7 млн.

ARM Cortex A9: 15 млн.

Core i7

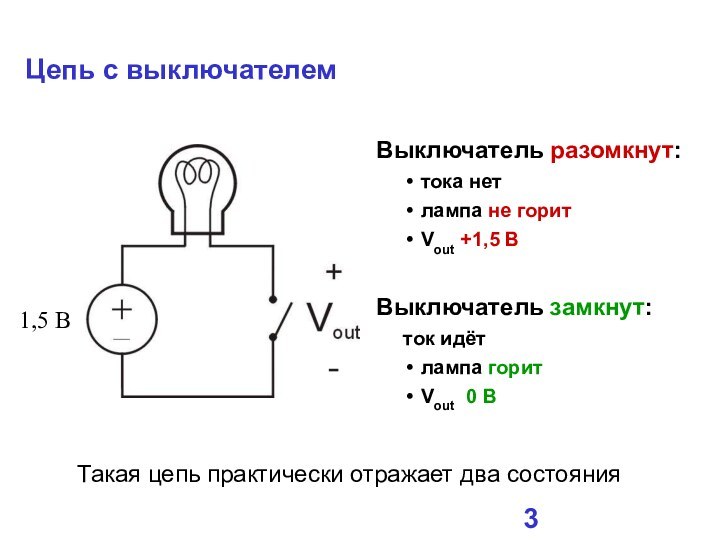

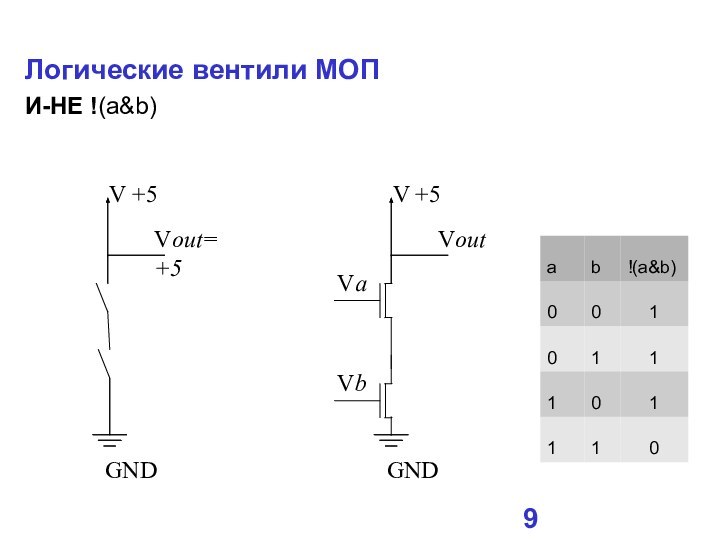

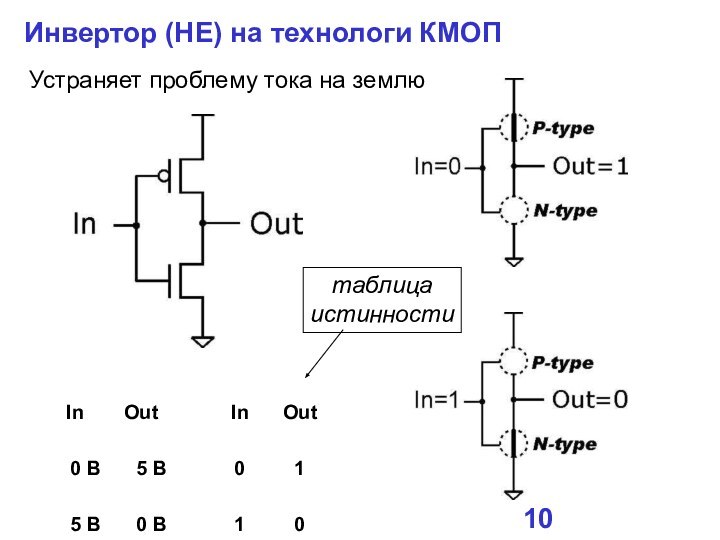

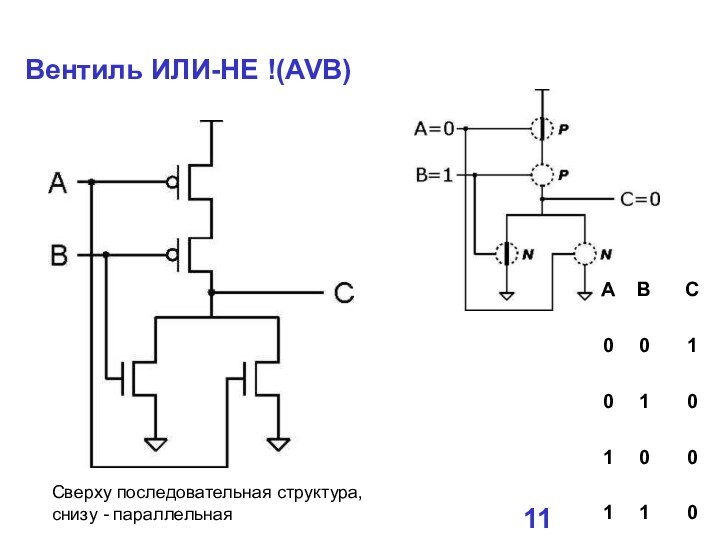

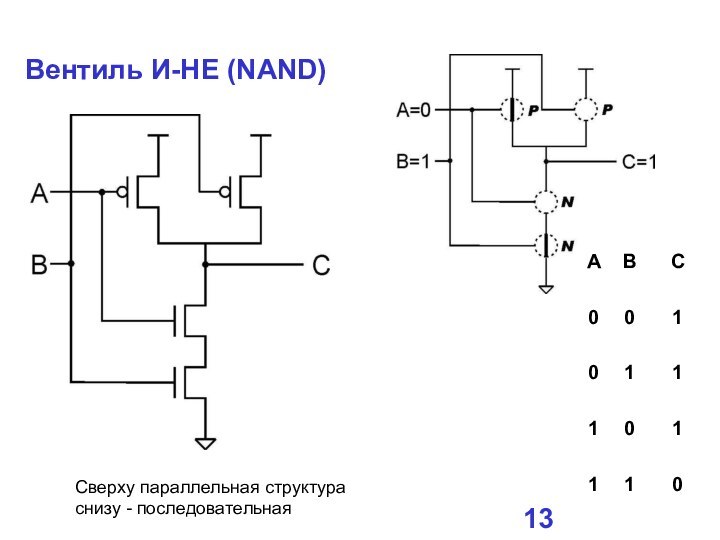

(4 ядра) 731 млн.Логически транзистор представляет собой выключатель

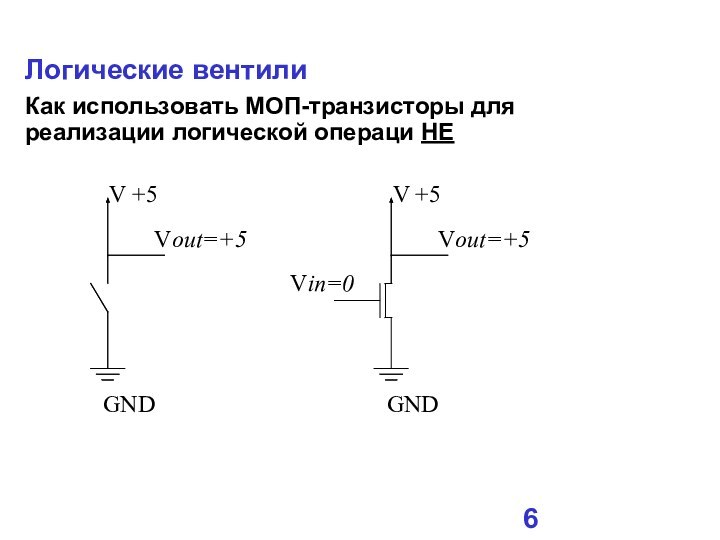

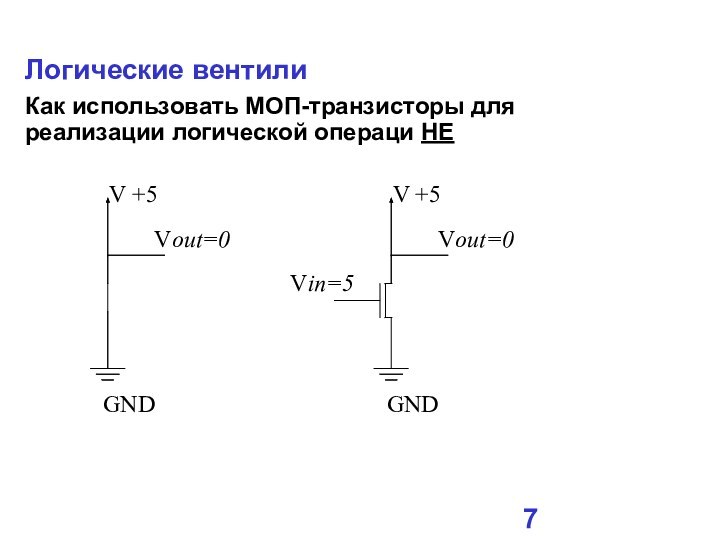

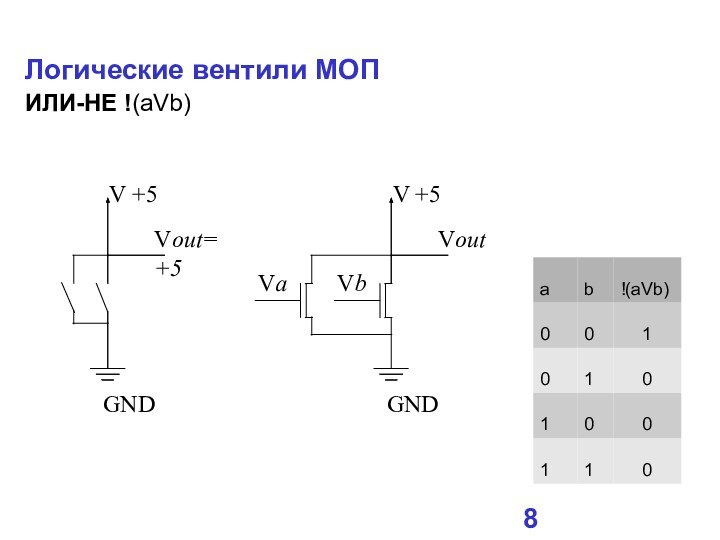

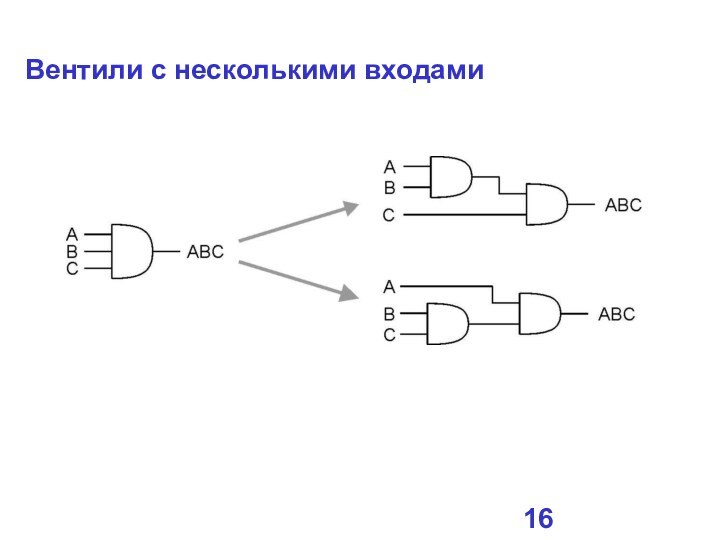

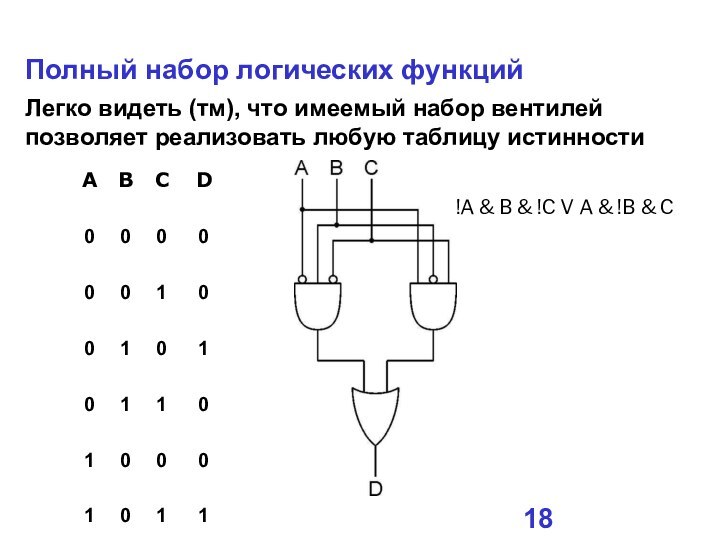

Их комбинации позволяют строить логические элементы – И, ИЛИ, НЕ, …

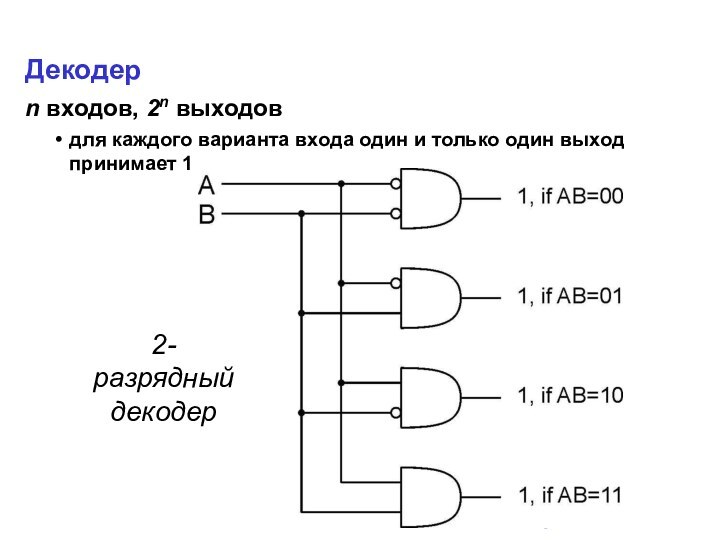

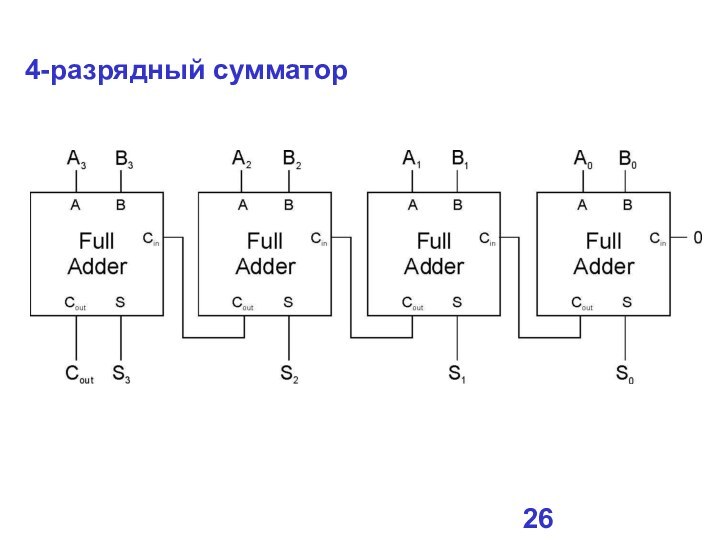

На логических элементах строятся устройства – сумматор, мультиплексор, декодер, регистр

На логических устройствах строится процессор