Слайд 2

Обзор

Оперативная память

Принцип работы

Основные характеристики микросхем памяти

3.1. Емкость и

разрядность

3.2. Быстродействие памяти

3.3. Банки и каналы памяти

3.4. Тайминг памяти

3.5.

Разгон памяти

DRAM

FPM DRAM

EDO DRAM

SDRAM

DDR SDRAM

DDR3 иDDR3 SDRAM

Rambus DRAM

Слайд 3

Оперативная память

Оперативная память (RAM, ОЗУ) — временная

память, т. е. данные хранятся в ней только до

выключения PC. Конструктивно оперативная память РС выполняется в виде модулей, так что при желании можно сравнительно просто заменить их или установить дополнительные и тем самым изменить (скорее всего, увеличить) объем оперативной памяти РС.

Чтобы CPU мог выполнять программы, они должны быть загружены в оперативную рабочую память, т. е. в память, доступную для программ пользователя. К данным, находящимся в оперативной памяти (Random Access Memory, RAM — память с произвольным доступом), CPU имеет непосредственный доступ, а к периферийной, или внешней памяти (гибким и жестким дискам) — через буфер, являющийся также разновидностью оперативной памяти, недоступной пользователю. Только после того как программа будет загружена в RAM с внешнего носителя данных, возможна дальнейшая ее работа.

Время доступа к данным, находящимся в RAM, чрезвычайно мало. Для сравнения можно привести простой пример. Пусть время доступа к памяти составляет порядка 200 нс, в то время как время доступа к данным на жестком диске составляет 12 000 000 нс. Если предположить, что 1 нс равна 1 с, то время обращения к памяти составит 3,3 мин, а время обращения к жесткому диску — 4,5 месяца.

Слайд 4

Оперативная память

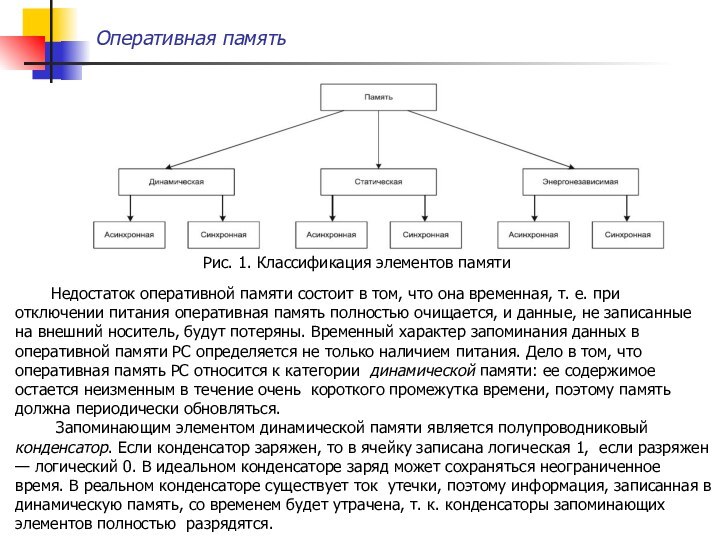

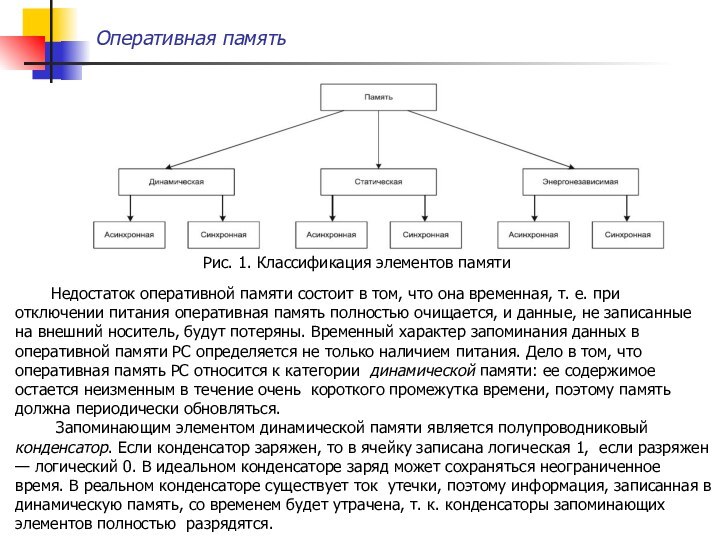

Рис. 1. Классификация элементов памяти

Недостаток

оперативной памяти состоит в том, что она временная, т.

е. при отключении питания оперативная память полностью очищается, и данные, не записанные на внешний носитель, будут потеряны. Временный характер запоминания данных в оперативной памяти РС определяется не только наличием питания. Дело в том, что оперативная память РС относится к категории динамической памяти: ее содержимое остается неизменным в течение очень короткого промежутка времени, поэтому память должна периодически обновляться.

Запоминающим элементом динамической памяти является полупроводниковый конденсатор. Если конденсатор заряжен, то в ячейку записана логическая 1, если разряжен — логический 0. В идеальном конденсаторе заряд может сохраняться неограниченное время. В реальном конденсаторе существует ток утечки, поэтому информация, записанная в динамическую память, со временем будет утрачена, т. к. конденсаторы запоминающих элементов полностью разрядятся.

Слайд 5

Оперативная память

Чтобы пояснить этот процесс, представим

элемент памяти как ведро с водой, которое может быть

либо пустым (состояние 0), либо полным (состояние 1). Однако в этом ведре имеются такие маленькие дырки, что вода (информация) вытекала бы по капле, если бы "водоносу" (специальной логической схеме) не было поручено компенсировать убыток воды (данных) так, чтобы уровень ее оставался неизменным. Этот процесс называется регенерацией памяти (Refresh). Деятельность "водоноса" имеет огромное значение, поэтому ему нельзя мешать. Это означает, что CPU имеет доступ к данным, находящимся в RAM, только в течение циклов, свободных от регенерации.

Единственным способом регенерации хранимой в памяти информации является выполнение операции чтения/записи данных. Если информация заносится в динамическую память, а затем в течение нескольких миллисекунд остается невостребованной, она будет утрачена, т. к. конденсаторы запоминающих элементов полностью разрядятся.

Регенерация памяти происходит при выполнении каждой операции чтения или записи. Однако нет гарантии, что при выполнении любой программы произойдет обращение ко всем ячейкам памяти, поэтому имеется специальная схема, которая через определенные промежутки времени (например, каждые 2 мс) будет осуществлять доступ (для считывания) ко всем строкам памяти. В эти моменты CPU находится в состоянии ожидания. За один цикл схема регенерирует все строки динамической памяти.

В 1966 г. ученый компании IBM Роберт Деннард (Robert Dennard)

разработал однотранзисторную динамическую оперативную память (DRAM).

Слайд 6

Оперативная память – принцип работы

Рис. 2. Структурная

схема динамической памяти.

Ячейки памяти организованы в матрицу, состоящую

из строк и столбцов. Полный адрес ячейки данных включает два компонента — адрес строки (row address) и адрес столбца (column address).

Слайд 7

Оперативная память – принцип работы

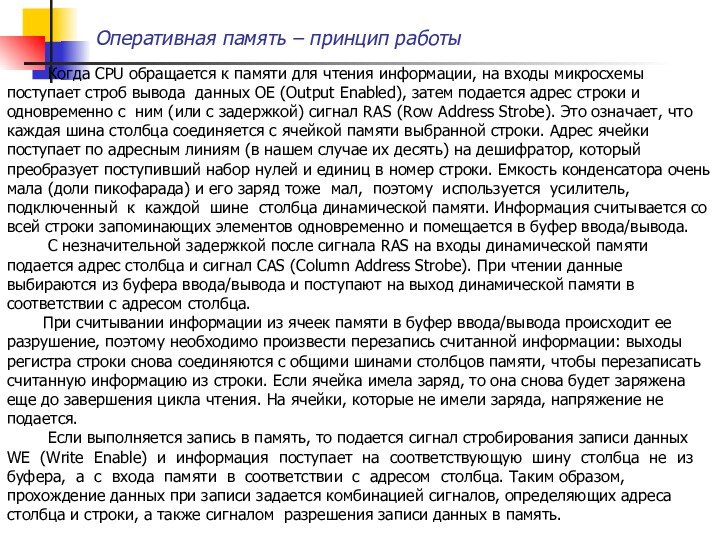

Когда CPU

обращается к памяти для чтения информации, на входы микросхемы

поступает строб вывода данных OE (Output Enabled), затем подается адрес строки и одновременно с ним (или с задержкой) сигнал RAS (Row Address Strobe). Это означает, что каждая шина столбца соединяется с ячейкой памяти выбранной строки. Адрес ячейки поступает по адресным линиям (в нашем случае их десять) на дешифратор, который преобразует поступивший набор нулей и единиц в номер строки. Емкость конденсатора очень мала (доли пикофарада) и его заряд тоже мал, поэтому используется усилитель, подключенный к каждой шине столбца динамической памяти. Информация считывается со всей строки запоминающих элементов одновременно и помещается в буфер ввода/вывода.

С незначительной задержкой после сигнала RAS на входы динамической памяти подается адрес столбца и сигнал CAS (Column Address Strobe). При чтении данные выбираются из буфера ввода/вывода и поступают на выход динамической памяти в соответствии с адресом столбца.

При считывании информации из ячеек памяти в буфер ввода/вывода происходит ее разрушение, поэтому необходимо произвести перезапись считанной информации: выходы регистра строки снова соединяются с общими шинами столбцов памяти, чтобы перезаписать считанную информацию из строки. Если ячейка имела заряд, то она снова будет заряжена еще до завершения цикла чтения. На ячейки, которые не имели заряда, напряжение не подается.

Если выполняется запись в память, то подается сигнал стробирования записи данных WE (Write Enable) и информация поступает на соответствующую шину столбца не из буфера, а с входа памяти в соответствии с адресом столбца. Таким образом, прохождение данных при записи задается комбинацией сигналов, определяющих адреса столбца и строки, а также сигналом разрешения записи данных в память.

Слайд 8

Основными характеристиками элементов (микросхем) памяти являются:

тип;

емкость;

разрядность;

быстродействие;

временная диаграмма.

Основные характеристики микросхем памяти.

Емкость и

разрядность

Рис.3. Структурная схема микросхемы памяти 1D4.

Слайд 9

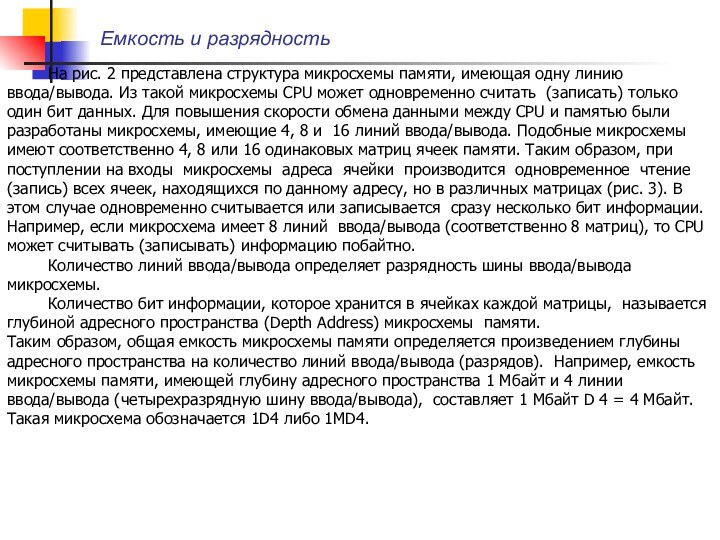

На рис. 2 представлена структура микросхемы памяти,

имеющая одну линию ввода/вывода. Из такой микросхемы CPU может

одновременно считать (записать) только один бит данных. Для повышения скорости обмена данными между CPU и памятью были разработаны микросхемы, имеющие 4, 8 и 16 линий ввода/вывода. Подобные микросхемы имеют соответственно 4, 8 или 16 одинаковых матриц ячеек памяти. Таким образом, при поступлении на входы микросхемы адреса ячейки производится одновременное чтение (запись) всех ячеек, находящихся по данному адресу, но в различных матрицах (рис. 3). В этом случае одновременно считывается или записывается сразу несколько бит информации. Например, если микросхема имеет 8 линий ввода/вывода (соответственно 8 матриц), то CPU может считывать (записывать) информацию побайтно.

Количество линий ввода/вывода определяет разрядность шины ввода/вывода

микросхемы.

Количество бит информации, которое хранится в ячейках каждой матрицы, называется глубиной адресного пространства (Depth Address) микросхемы памяти.

Таким образом, общая емкость микросхемы памяти определяется произведением глубины адресного пространства на количество линий ввода/вывода (разрядов). Например, емкость микросхемы памяти, имеющей глубину адресного пространства 1 Мбайт и 4 линии ввода/вывода (четырехразрядную шину ввода/вывода), составляет 1 Мбайт D 4 = 4 Мбайт. Такая микросхема обозначается 1D4 либо 1МD4.

Емкость и разрядность

Слайд 10

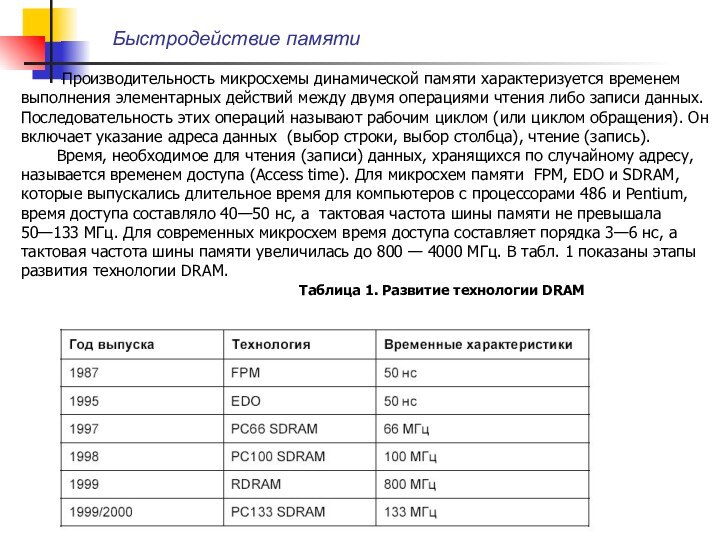

Производительность микросхемы динамической памяти характеризуется временем выполнения

элементарных действий между двумя операциями чтения либо записи данных.

Последовательность этих операций называют рабочим циклом (или циклом обращения). Он включает указание адреса данных (выбор строки, выбор столбца), чтение (запись).

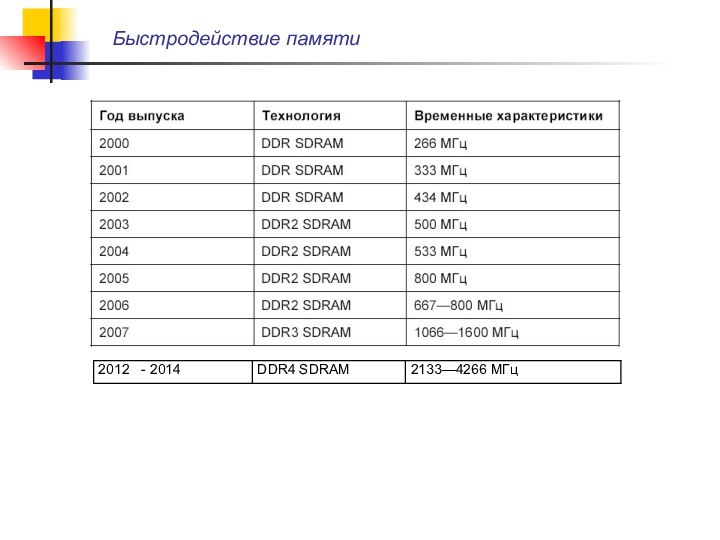

Время, необходимое для чтения (записи) данных, хранящихся по случайному адресу, называется временем доступа (Access time). Для микросхем памяти FPM, EDO и SDRAM, которые выпускались длительное время для компьютеров с процессорами 486 и Pentium, время доступа составляло 40—50 нс, а тактовая частота шины памяти не превышала 50—133 МГц. Для современных микросхем время доступа составляет порядка 3—6 нс, а тактовая частота шины памяти увеличилась до 800 — 4000 МГц. В табл. 1 показаны этапы развития технологии DRAM.

Таблица 1. Развитие технологии DRAM

Быстродействие памяти

Слайд 12

Банки и каналы памяти

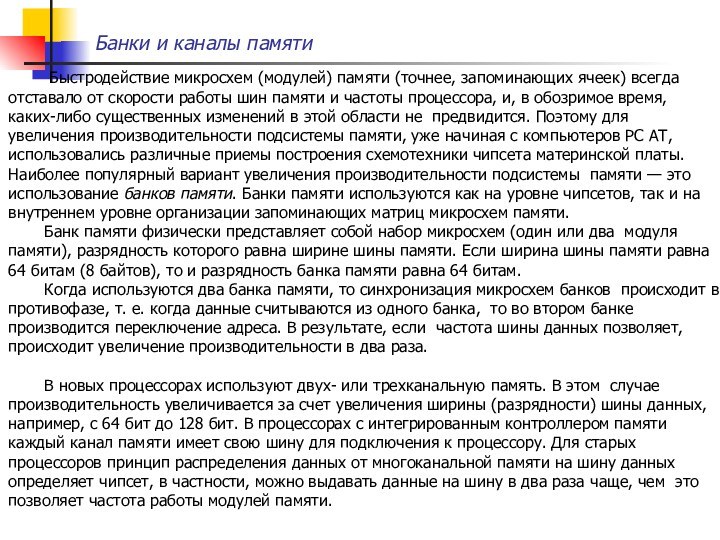

Быстродействие микросхем (модулей) памяти

(точнее, запоминающих ячеек) всегда отставало от скорости работы шин

памяти и частоты процессора, и, в обозримое время, каких-либо существенных изменений в этой области не предвидится. Поэтому для увеличения производительности подсистемы памяти, уже начиная с компьютеров РС АТ, использовались различные приемы построения схемотехники чипсета материнской платы.

Наиболее популярный вариант увеличения производительности подсистемы памяти — это использование банков памяти. Банки памяти используются как на уровне чипсетов, так и на внутреннем уровне организации запоминающих матриц микросхем памяти.

Банк памяти физически представляет собой набор микросхем (один или два модуля памяти), разрядность которого равна ширине шины памяти. Если ширина шины памяти равна 64 битам (8 байтов), то и разрядность банка памяти равна 64 битам.

Когда используются два банка памяти, то синхронизация микросхем банков происходит в противофазе, т. е. когда данные считываются из одного банка, то во втором банке производится переключение адреса. В результате, если частота шины данных позволяет, происходит увеличение производительности в два раза.

В новых процессорах используют двух- или трехканальную память. В этом случае производительность увеличивается за счет увеличения ширины (разрядности) шины данных, например, с 64 бит до 128 бит. В процессорах с интегрированным контроллером памяти каждый канал памяти имеет свою шину для подключения к процессору. Для старых процессоров принцип распределения данных от многоканальной памяти на шину данных определяет чипсет, в частности, можно выдавать данные на шину в два раза чаще, чем это позволяет частота работы модулей памяти.

Слайд 13

Тайминг памяти

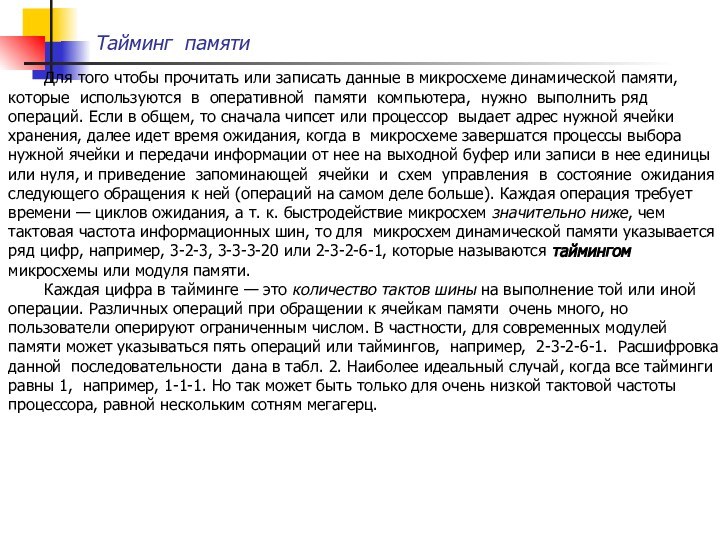

Для того чтобы прочитать или записать

данные в микросхеме динамической памяти, которые используются в оперативной

памяти компьютера, нужно выполнить ряд операций. Если в общем, то сначала чипсет или процессор выдает адрес нужной ячейки хранения, далее идет время ожидания, когда в микросхеме завершатся процессы выбора нужной ячейки и передачи информации от нее на выходной буфер или записи в нее единицы или нуля, и приведение запоминающей ячейки и схем управления в состояние ожидания следующего обращения к ней (операций на самом деле больше). Каждая операция требует времени — циклов ожидания, а т. к. быстродействие микросхем значительно ниже, чем тактовая частота информационных шин, то для микросхем динамической памяти указывается ряд цифр, например, 3-2-3, 3-3-3-20 или 2-3-2-6-1, которые называются таймингом микросхемы или модуля памяти.

Каждая цифра в тайминге — это количество тактов шины на выполнение той или иной операции. Различных операций при обращении к ячейкам памяти очень много, но пользователи оперируют ограниченным числом. В частности, для современных модулей памяти может указываться пять операций или таймингов, например, 2-3-2-6-1. Расшифровка данной последовательности дана в табл. 2. Наиболее идеальный случай, когда все тайминги равны 1, например, 1-1-1. Но так может быть только для очень низкой тактовой частоты процессора, равной нескольким сотням мегагерц.

Слайд 14

Тайминг памяти

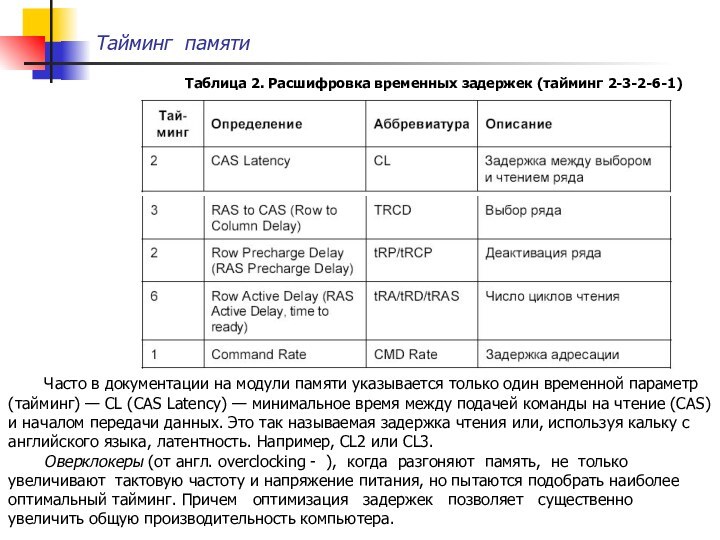

Таблица 2. Расшифровка временных задержек (тайминг

2-3-2-6-1)

Часто в документации на модули памяти указывается только один

временной параметр (тайминг) — CL (CAS Latency) — минимальное время между подачей команды на чтение (CAS) и началом передачи данных. Это так называемая задержка чтения или, используя кальку с английского языка, латентность. Например, CL2 или CL3.

Оверклокеры (от англ. overclocking - ), когда разгоняют память, не только увеличивают тактовую частоту и напряжение питания, но пытаются подобрать наиболее оптимальный тайминг. Причем оптимизация задержек позволяет существенно увеличить общую производительность компьютера.

Слайд 15

Разгон памяти - overclocking

Когда мы смотрим

на характеристики процессоров и видеокарт, то теперь везде фигурируют

огромные величины частот, например, 500, 800, 1000, 3000 МГц. Но, несмотря на такие огромные величины частот наиболее главных узлов современного компьютера, запоминающие ячейки оперативной памяти до сих пор реально работают на частотах около 200—300 МГц, и в ближайшее время такое положение дел коренным образом не изменится. А частота, например, в 1600 МГц для модулей памяти справедлива лишь для выходных буферных схем микросхем DRAM. Для ускорения работы оперативной памяти (увеличения производительности приложений) существует несколько технологий: увеличение тактовой частоты, уменьшение таймингов и увеличение напряжения питания. А т. к. сегодня производители процессоров отказались от жесткой фиксации частотных характеристик своей продукции, и даже поощряют разгон, то в распоряжении пользователей имеется ряд программных инструментов для изменения стандартных характеристик узлов процессора и памяти (обычно это выполняется через пункты меню программы CMOS Setup, предназначенной для настройки параметров BIOS).

Наиболее "древняя" методика разгона памяти, но эффективно использующаяся и сегодня — это увеличение опорной тактовой частоты, подающейся на модули памяти, которая, как правило, привязана к тактовой частоте системной шины. Повышая, скажем, на 25 МГц тактовую частоту, мы существенно увеличиваем производительность системы, что даже эффективнее замены процессора на более мощную модель. Заметим, результирующая частота для модулей DDR3 будет в 8 раз выше.

Слайд 16

Если обратить внимание на маркировку модулей памяти, то

можно увидеть, что в настоящее время предлагаются модули памяти

с частотами, не соответствующие обычным кратностям SDRAM, например, варианты 1375, 1625, 1800 МГц для модулей DDR3. В данном случае отражается принцип оптимизации тактовой частоты модулей памяти и частоты процессора. Хотя и считается, что цепи модулей памяти и процессора работают в синхронном режиме, но при стандартных частотах, например, 1333 и 1600 МГц периодически происходит сбой синхронизации, что вынуждает процессор останавливать прием/передачу данных на некоторое время. Если подобрать оптимальную тактовую частоту для модулей памяти, то можно увеличить общую производительность.

Другим эффективным методом разгона памяти является принцип уменьшения таймингов (задержек). Например, если вместо варианта 4-4-4 использовать 3-3-3, то мы существенно увеличим производительность памяти. Но производители записывают в микросхему для хранения информации SPD (Serial Presence Detect) (находится на каждом модуле памяти) характеристики, которые они гарантируют для всех случаев применения. Пользователь может самостоятельно подобрать тайминги для конкретных экземпляров модулей памяти и системной платы, правда, это кропотливая и нудная работа, требующая аккуратности и внимательности (обязательное тестирование системы на всех этапах разгона!).

Увеличение тактовой частоты и уменьшение таймингов почти всегда сопровождается увеличением уровня напряжения питания модулей памяти. К сожалению, просто так увеличить напряжение для современных модулей памяти нельзя, т. к. это сопровождается довольно вредными и неприятными эффектами. В частности, это увеличение тепловыделения, поэтому при разгоне модулей памяти приходится использовать конструкции модулей с теплоотводами и принудительным охлаждением.

Разгон памяти - overclocking

Слайд 17

Буква "D" в аббревиатуре "DRAM" означает "динамическая" (Dynamic),

т. е. для сохранения данных, записанных в микросхеме памяти,

необходима их периодическая регенерация. Все микросхемы DRAM имеют матричную организацию, причем каждый элемент матрицы (миниатюрный конденсатор) хранит один бит данных и адресуется с помощью следующих сигналов: RAS, адрес строки, CAS и адрес столбца.

ПРИМЕЧАНИЕ

Цикл регенерации происходит при фиксации адреса столбца и циклическом изменении адреса строки. Следовательно, чем меньше строк в матрице микросхемы, тем короче цикл регенерации.

Часто в описании микросхем можно встретить следующую характеристику: 2k refresh, 4k refresh и т. п. Число nk означает длину строки, т. е. количество столбцов. Дело в том, что "нормальное" количество столбцов и строк для чипа организации 4 D 4 численно равно 2 Кбит (4 Мбит = 1024 D 1024 D 4 = 1 048 576 D 4 = 4 194 304 бит, 4 194 304 = 2048 бит). Однако с целью повышения быстродействия были разработаны микросхемы с "неквадратной" матрицей, имеющие 1 Кбит строк и, соответственно, столбцов, что позволило сократить время регенерации.

В процессе совершенствования технологии изготовления DRAM были разработаны различные типы памяти: FPM, EDO, SDRAM, DDR SDRAM.

DRAM

Слайд 18

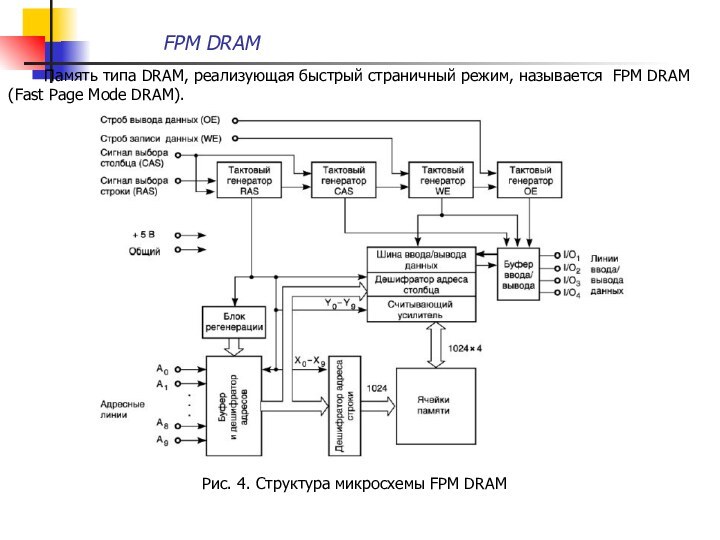

FPM DRAM

Память типа DRAM, реализующая быстрый

страничный режим, называется FPM DRAM (Fast Page Mode DRAM).

Рис.

4. Структура микросхемы FPM DRAM

Слайд 19

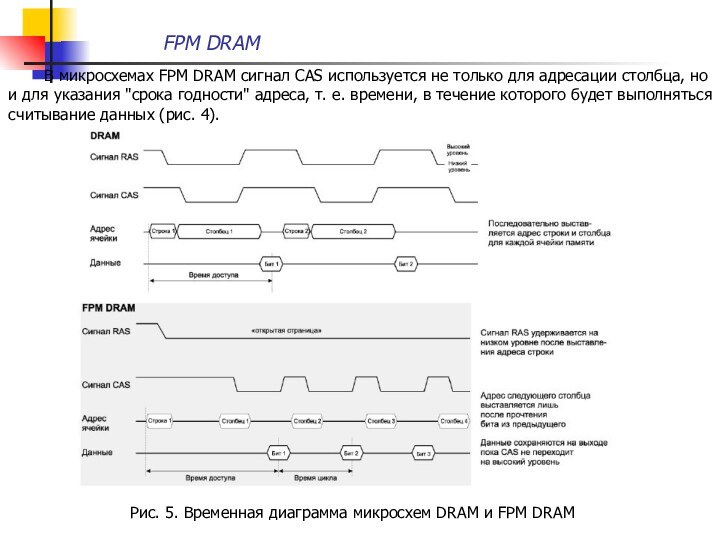

В микросхемах FPM DRAM сигнал CAS используется не

только для адресации столбца, но и для указания "срока

годности" адреса, т. е. времени, в течение которого будет выполняться считывание данных (рис. 4).

FPM DRAM

Рис. 5. Временная диаграмма микросхем DRAM и FPM DRAM

Слайд 20

Память этого типа появилась в последних моделях

РС с CPU 80486 и получила широкое распространение. Время

доступа процессора к памяти при использовании микросхем FPM DRAM (60 нс) сократилось на 40% по сравнению с временем доступа к обычным DRAM. Время рабочего цикла последних чипов составило 35 нс. Тем не менее, микросхемам FPM DRAM не удавалось "угнаться" за процессором, если частота системной шины превышала 28 МГц.

Временная диаграмма работы FPM DRAM представлена на рис. 5.

FPM DRAM

Слайд 21

EDO DRAM

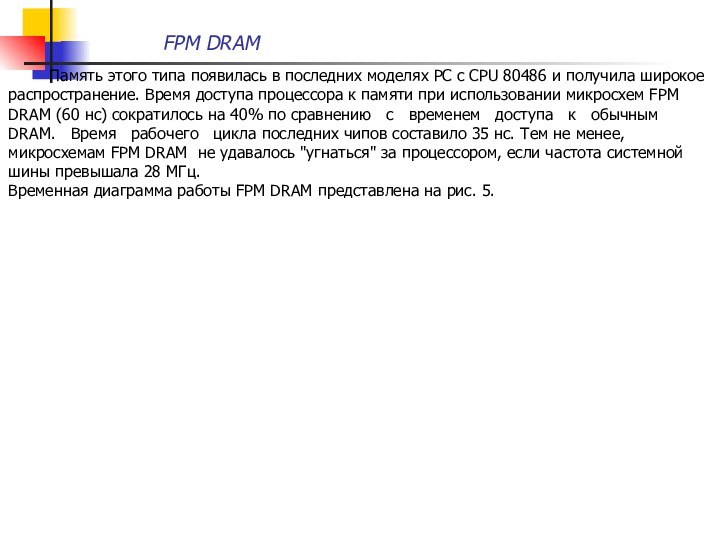

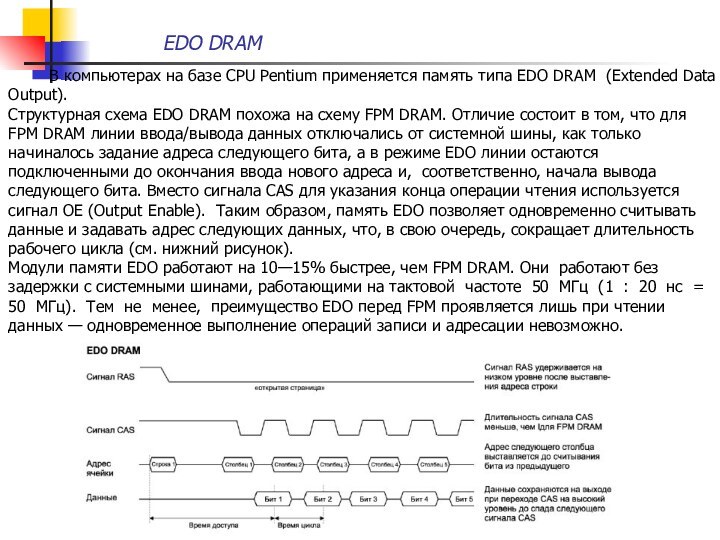

В компьютерах на базе

CPU Pentium применяется память типа EDO DRAM (Extended Data

Output).

Структурная схема EDO DRAM похожа на схему FPM DRAM. Отличие состоит в том, что для FPM DRAM линии ввода/вывода данных отключались от системной шины, как только начиналось задание адреса следующего бита, а в режиме EDO линии остаются подключенными до окончания ввода нового адреса и, соответственно, начала вывода следующего бита. Вместо сигнала CAS для указания конца операции чтения используется сигнал OE (Output Enable). Таким образом, память EDO позволяет одновременно считывать данные и задавать адрес следующих данных, что, в свою очередь, сокращает длительность рабочего цикла (см. нижний рисунок).

Модули памяти EDO работают на 10—15% быстрее, чем FPM DRAM. Они работают без задержки с системными шинами, работающими на тактовой частоте 50 МГц (1 : 20 нс = 50 МГц). Тем не менее, преимущество EDO перед FPM проявляется лишь при чтении данных — одновременное выполнение операций записи и адресации невозможно.

Слайд 22

SDRAM

До 1997 г. производились только

асинхронные микросхемы DRAM, т. е. такие, работа которых не

была синхронизирована с частотой работы системной шины.

П РИМЕЧАНИЕ

Асинхронные элементы имеют только информационные входы и срабатывают непосредственно после изменения сигнала на входах. Сигнал на выходе появляется через некоторое время. Оно не регламентируется и может изменяться в зависимости от температуры и от старения полупроводниковых элементов. Основным недостатком асинхронных элементов является их низкая помехоустойчивость, проявляющаяся в сбоях при работе PC.

Для срабатывания синхронных элементов смены сигналов на входах недостаточно. Необходим дополнительный тактирующий сигнал, который подается на соответствующий вход. В качестве такого сигнала выбран тактовый сигнал системной шины. Этот сигнал задает частоту смены информации в определенные моменты времени. В эти же моменты обновляется информация на выходах элементов. Таким образом, процессы записи и считывания информации в память строго привязаны к тактам CPU или шины.

Все рассмотренные выше элементы памяти (FPM и EDO) работают асинхронно с тактовой частотой системной шины. Поэтому для передачи данных из памяти в CPU необходимо подтверждение связи между CPU и контроллером памяти.

Процесс чтения данных организован следующим образом. CPU сообщает контроллеру памяти с помощью сигнала ADS, что ему необходимы данные, располагающиеся по определенному адресу. Затем осуществляется цикл чтения данных из DRAM. Когда данные прочитаны и находятся на выходных линиях DRAM, контроллер памяти посылает процессору сигнал BRDY и только тогда данные поступают на CPU. Если данные еще не готовы, то CPU вынужден осуществлять холостые циклы (Wаit state) в ожидании данных.

Слайд 23

SDRAM

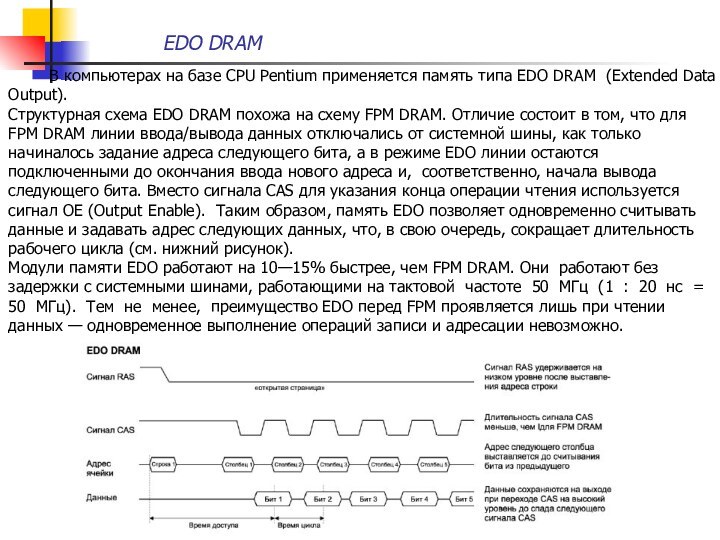

В 1997 г. для синхронизации работы

памяти и системной шины использовалась

микросхема синхронной динамической памяти

SDRAM (Sychronous DRAM). Метод доступа к строкам и столбцам данных в микросхемах SDRAM и стандартной DRAM реализован одинаково. Отличие заключается в следующем: все операции в микросхемах SDRAM синхронизированы с тактовой частотой CPU, т. е. память и CPU работают синхронно без циклов ожидания (рис. 6).

Рис. 6. Временная диаграмма SDRAM в пакетном режиме

Слайд 24

SDRAM

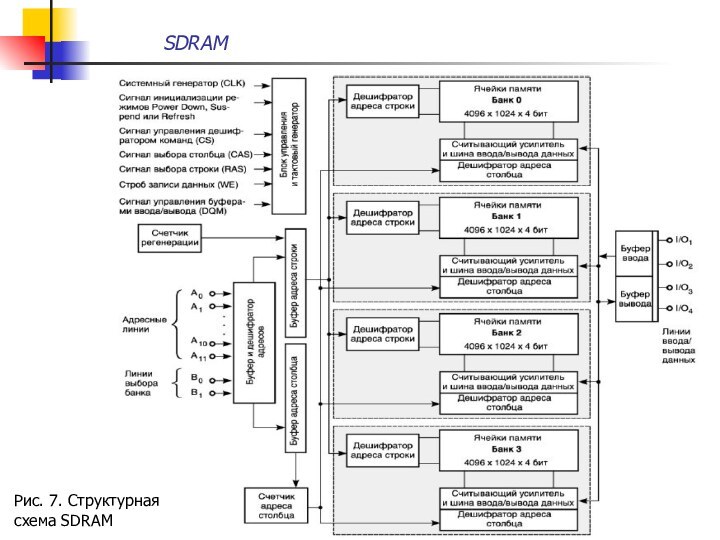

Рис. 7. Структурная схема SDRAM

Слайд 25

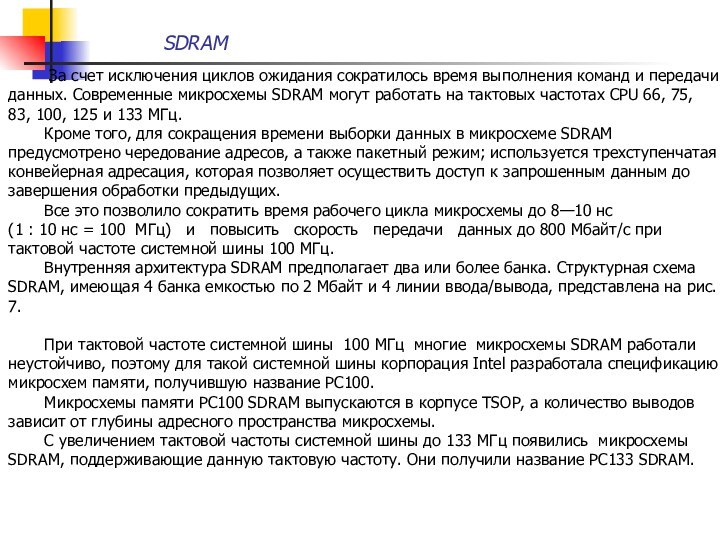

SDRAM

За счет исключения циклов ожидания

сократилось время выполнения команд и передачи данных. Современные микросхемы

SDRAM могут работать на тактовых частотах CPU 66, 75, 83, 100, 125 и 133 МГц.

Кроме того, для сокращения времени выборки данных в микросхеме SDRAM предусмотрено чередование адресов, а также пакетный режим; используется трехступенчатая конвейерная адресация, которая позволяет осуществить доступ к запрошенным данным до завершения обработки предыдущих.

Все это позволило сократить время рабочего цикла микросхемы до 8—10 нс

(1 : 10 нс = 100 МГц) и повысить скорость передачи данных до 800 Мбайт/c при тактовой частоте системной шины 100 МГц.

Внутренняя архитектура SDRAM предполагает два или более банка. Структурная схема SDRAM, имеющая 4 банка емкостью по 2 Мбайт и 4 линии ввода/вывода, представлена на рис. 7.

При тактовой частоте системной шины 100 МГц многие микросхемы SDRAM работали неустойчиво, поэтому для такой системной шины корпорация Intel разработала спецификацию микросхем памяти, получившую название PC100.

Микросхемы памяти PC100 SDRAM выпускаются в корпусе TSOP, а количество выводов зависит от глубины адресного пространства микросхемы.

С увеличением тактовой частоты системной шины до 133 МГц появились микросхемы SDRAM, поддерживающие данную тактовую частоту. Они получили название PC133 SDRAM.

Слайд 26

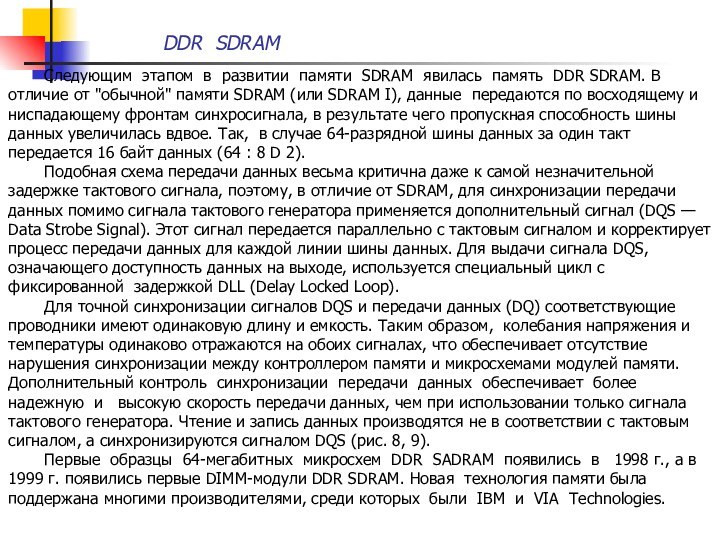

DDR SDRAM

Следующим этапом в развитии памяти SDRAM

явилась память DDR SDRAM. В отличие от "обычной" памяти

SDRAM (или SDRAM I), данные передаются по восходящему и ниспадающему фронтам синхросигнала, в результате чего пропускная способность шины данных увеличилась вдвое. Так, в случае 64-разрядной шины данных за один такт передается 16 байт данных (64 : 8 D 2).

Подобная схема передачи данных весьма критична даже к самой незначительной задержке тактового сигнала, поэтому, в отличие от SDRAM, для синхронизации передачи данных помимо сигнала тактового генератора применяется дополнительный сигнал (DQS — Data Strobe Signal). Этот сигнал передается параллельно с тактовым сигналом и корректирует процесс передачи данных для каждой линии шины данных. Для выдачи сигнала DQS, означающего доступность данных на выходе, используется специальный цикл с фиксированной задержкой DLL (Delay Locked Loop).

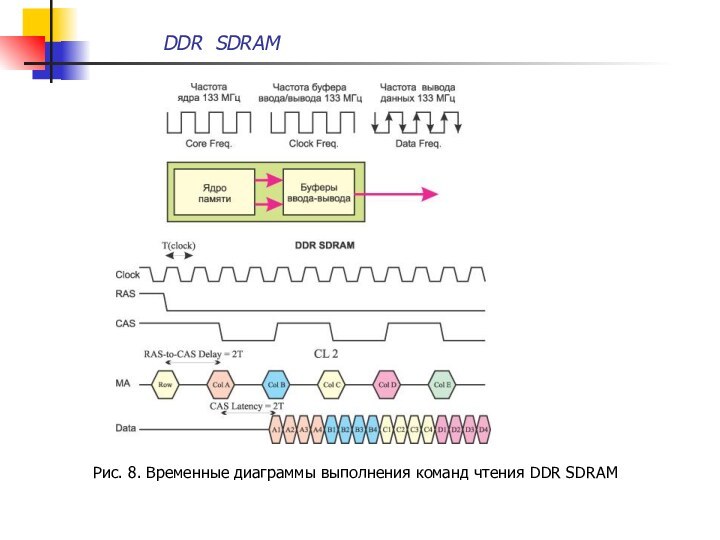

Для точной синхронизации сигналов DQS и передачи данных (DQ) соответствующие проводники имеют одинаковую длину и емкость. Таким образом, колебания напряжения и температуры одинаково отражаются на обоих сигналах, что обеспечивает отсутствие нарушения синхронизации между контроллером памяти и микросхемами модулей памяти. Дополнительный контроль синхронизации передачи данных обеспечивает более надежную и высокую скорость передачи данных, чем при использовании только сигнала тактового генератора. Чтение и запись данных производятся не в соответствии с тактовым сигналом, а синхронизируются сигналом DQS (рис. 8, 9).

Первые образцы 64-мегабитных микросхем DDR SADRAM появились в 1998 г., а в 1999 г. появились первые DIMM-модули DDR SDRAM. Новая технология памяти была поддержана многими производителями, среди которых были IBM и VIA Technologies.

Слайд 27

Рис. 8. Временные диаграммы выполнения команд чтения DDR

SDRAM

DDR SDRAM

Слайд 28

DDR SDRAM

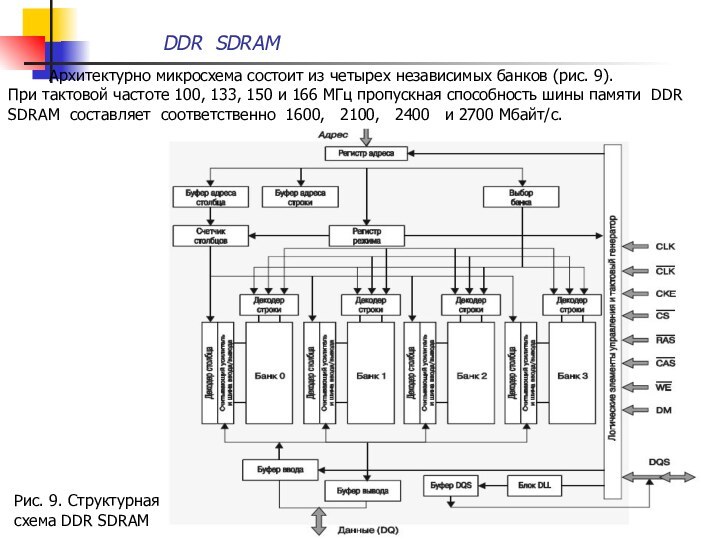

Архитектурно микросхема состоит из четырех

независимых банков (рис. 9).

При тактовой частоте 100, 133,

150 и 166 МГц пропускная способность шины памяти DDR SDRAM составляет соответственно 1600, 2100, 2400 и 2700 Мбайт/с.

Рис. 9. Структурная схема DDR SDRAM

Слайд 29

DDR 2 и 3 SDRAM

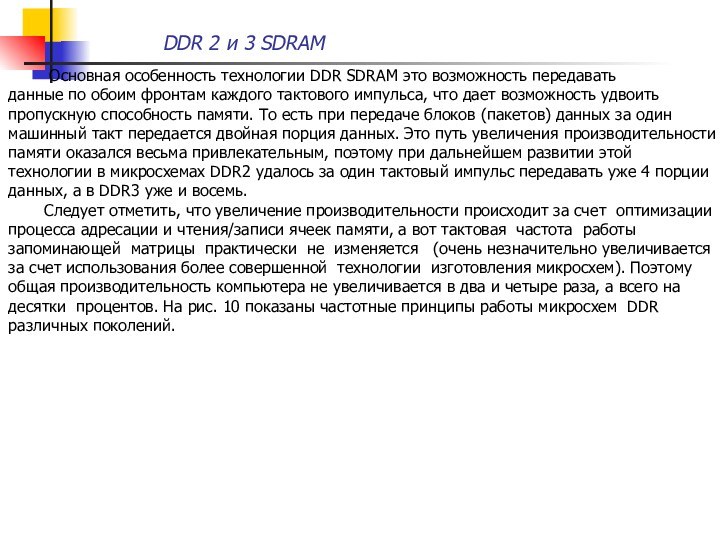

Основная особенность

технологии DDR SDRAM это возможность передавать

данные по обоим

фронтам каждого тактового импульса, что дает возможность удвоить пропускную способность памяти. То есть при передаче блоков (пакетов) данных за один машинный такт передается двойная порция данных. Это путь увеличения производительности памяти оказался весьма привлекательным, поэтому при дальнейшем развитии этой технологии в микросхемах DDR2 удалось за один тактовый импульс передавать уже 4 порции данных, а в DDR3 уже и восемь.

Следует отметить, что увеличение производительности происходит за счет оптимизации процесса адресации и чтения/записи ячеек памяти, а вот тактовая частота работы запоминающей матрицы практически не изменяется (очень незначительно увеличивается за счет использования более совершенной технологии изготовления микросхем). Поэтому общая производительность компьютера не увеличивается в два и четыре раза, а всего на десятки процентов. На рис. 10 показаны частотные принципы работы микросхем DDR различных поколений.

Слайд 30

DDR 2 и 3 SDRAM

Рис. 10. Частотные

принципы работы микросхем памяти SDRAM

Слайд 31

DDR 2 и 3 SDRAM

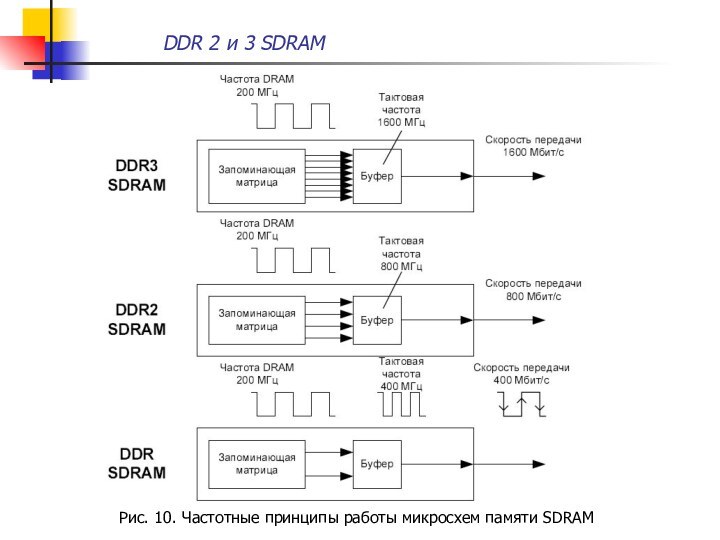

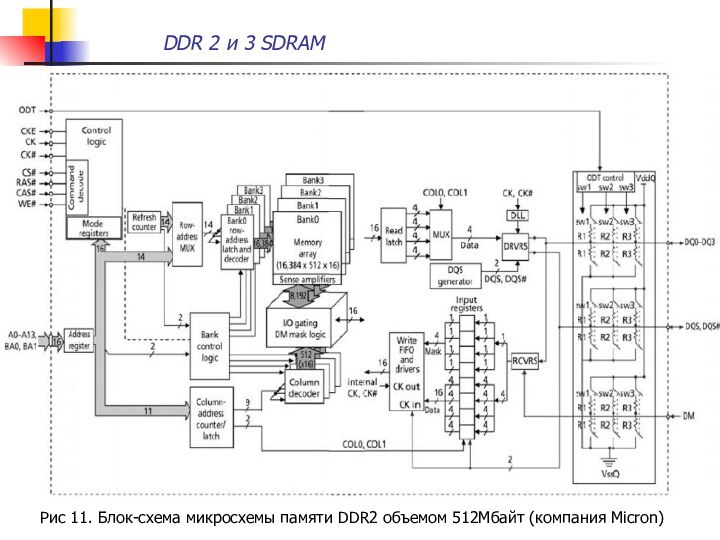

Рис 11. Блок-схема

микросхемы памяти DDR2 объемом 512Мбайт (компания Micron)

Слайд 32

DDR 2 и 3 SDRAM

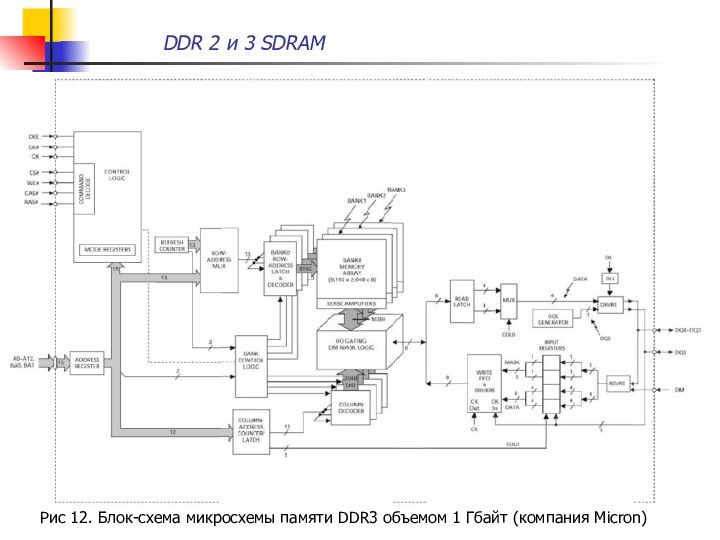

Рис 12. Блок-схема

микросхемы памяти DDR3 объемом 1 Гбайт (компания Micron)

Слайд 33

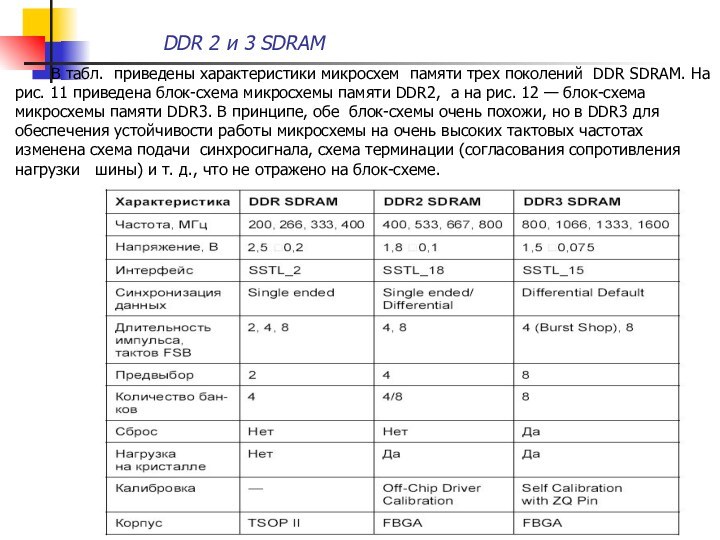

В табл. приведены характеристики микросхем памяти трех поколений

DDR SDRAM. На рис. 11 приведена блок-схема микросхемы памяти

DDR2, а на рис. 12 — блок-схема микросхемы памяти DDR3. В принципе, обе блок-схемы очень похожи, но в DDR3 для обеспечения устойчивости работы микросхемы на очень высоких тактовых частотах изменена схема подачи синхросигнала, схема терминации (согласования сопротивления нагрузки шины) и т. д., что не отражено на блок-схеме.

DDR 2 и 3 SDRAM

Слайд 34

DDR 2 и 3 SDRAM

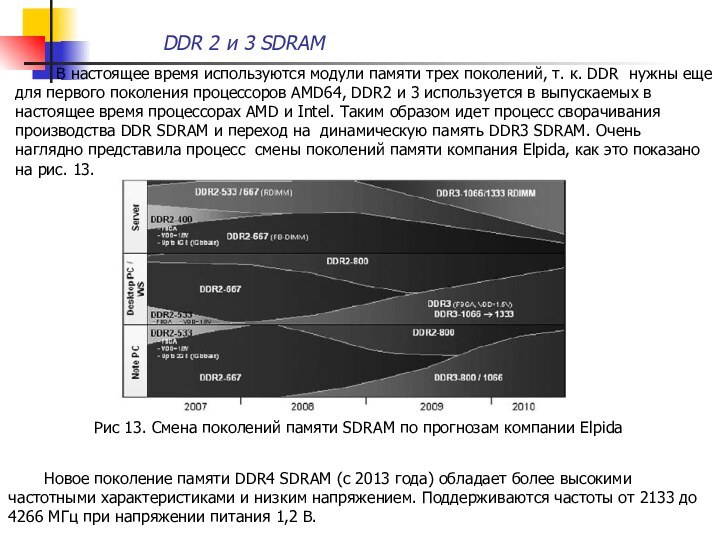

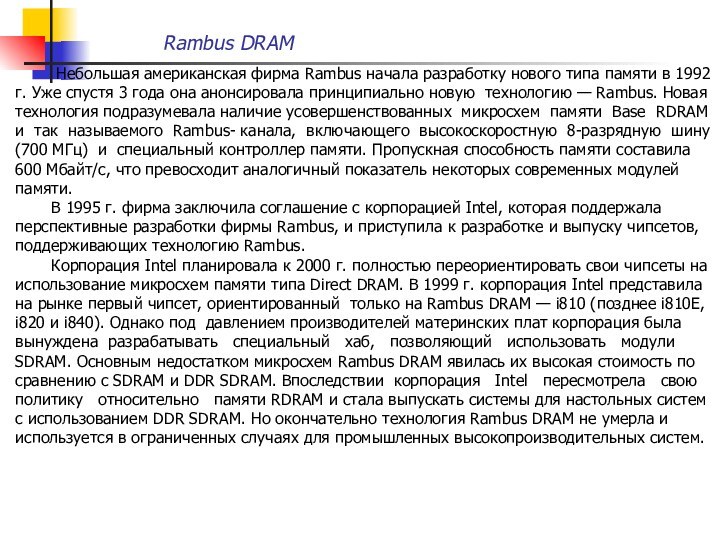

В настоящее

время используются модули памяти трех поколений, т. к. DDR

нужны еще для первого поколения процессоров AMD64, DDR2 и 3 используется в выпускаемых в настоящее время процессорах AMD и Intel. Таким образом идет процесс сворачивания производства DDR SDRAM и переход на динамическую память DDR3 SDRAM. Очень наглядно представила процесс смены поколений памяти компания Elpida, как это показано на рис. 13.

Рис 13. Смена поколений памяти SDRAM по прогнозам компании Elpida

Новое поколение памяти DDR4 SDRAM (с 2013 года) обладает более высокими частотными характеристиками и низким напряжением. Поддерживаются частоты от 2133 до 4266 МГц при напряжении питания 1,2 В.