- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Проектирование цифровых устройств на языке vhdl

Содержание

- 2. Применение ПЛИС

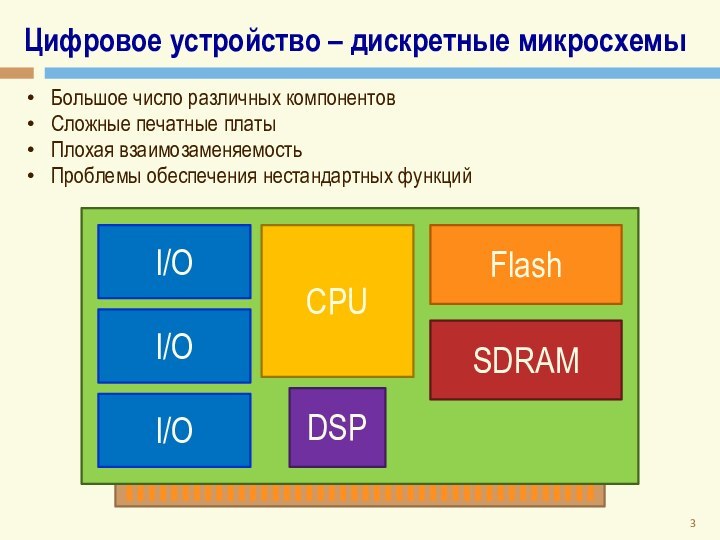

- 3. Цифровое устройство – дискретные микросхемыБольшое число различных компонентовСложные печатные платыПлохая взаимозаменяемостьПроблемы обеспечения нестандартных функций

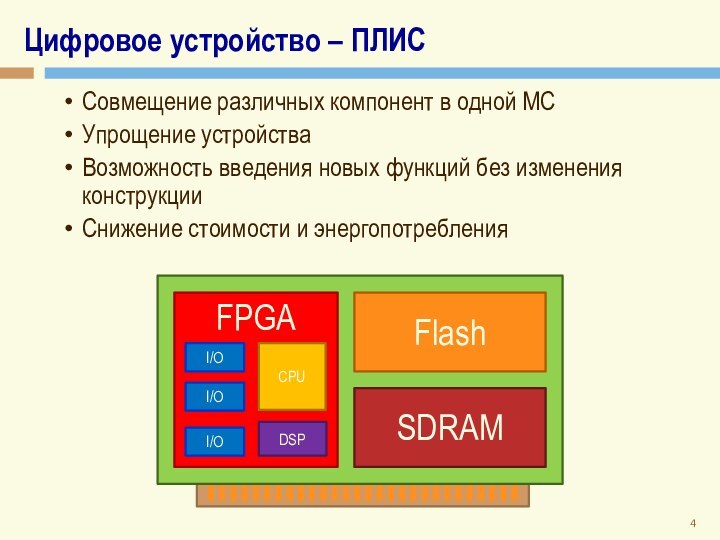

- 4. Цифровое устройство – ПЛИССовмещение различных компонент в

- 5. Некоторые сферы примененияБытовая техникаОбработка сигналовЦифровое телевидениеПромышленностьСАР / САУИзмерительное оборудованиеТелекоммуникацииКоммутационное оборудованиеБезопасностьЗащищенные системы связиСпециальные электронные устройства

- 6. История развития программируемой логики

- 7. Дискретная TTL-логикаПримитивы реализованы в отдельных микросхемах:NAND, OR,

- 8. Дискретная TTL-логика (разработка)Произвольная логическая функцияЛогическая функция в

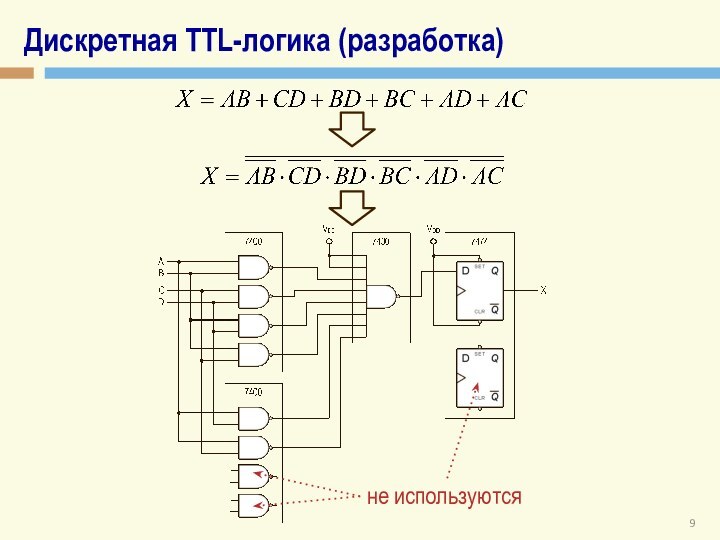

- 9. Дискретная TTL-логика (разработка)не используются

- 10. Реализация логических функцийЛогические функции…Могут быть выражены в

- 11. Ячейка ПЛМПрограммируемые логические матрицы (ПЛМ)Programmable Array Logic

- 12. Технология программированияFAMOS(Floating-gate Avalanche injection MOS transistor)FLOTOX(Floating-gate Tunnel

- 13. Технология программирования – FAMOSЗапись напряжениемСтирание ультрафиолетом (EPROM)до программирования – обычный транзисторпосле программирования01100 или 11

- 14. Технология программирования – FLOTOXЗапись напряжениемСтирание обратным напряжением

- 15. Преимущества программируемой логикиСнижение числа микросхемНиже стоимость и

- 16. Основы программируемой логики

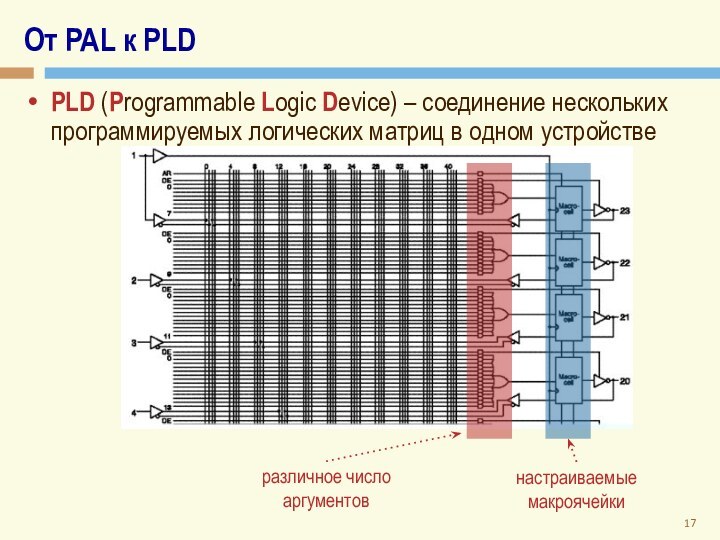

- 17. От PAL к PLDPLD (Programmable Logic Device)

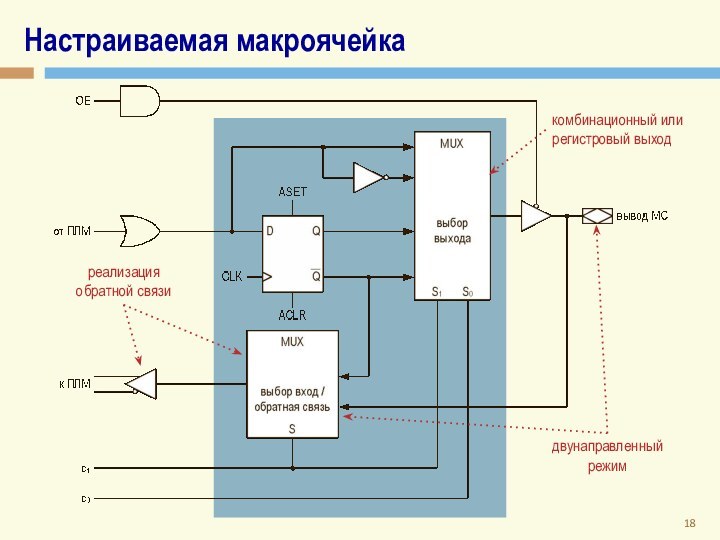

- 18. Настраиваемая макроячейкадвунаправленный режимкомбинационный или регистровый выходреализация обратной связи

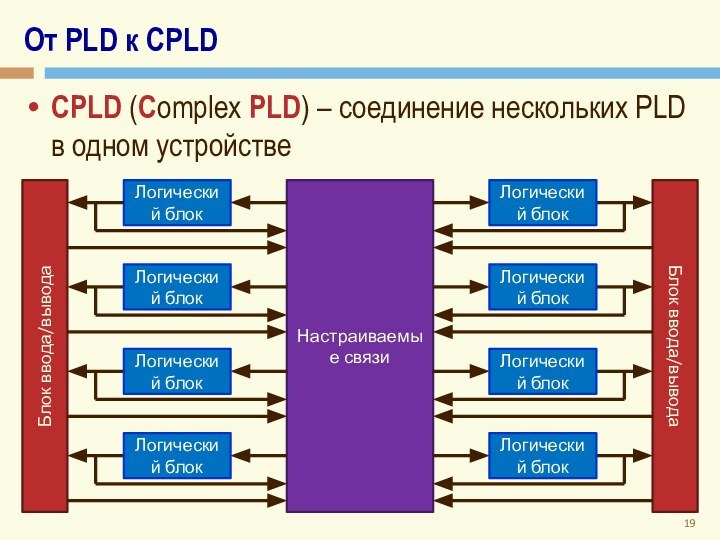

- 19. От PLD к CPLDCPLD (Complex PLD) – соединение нескольких PLD в одном устройстве

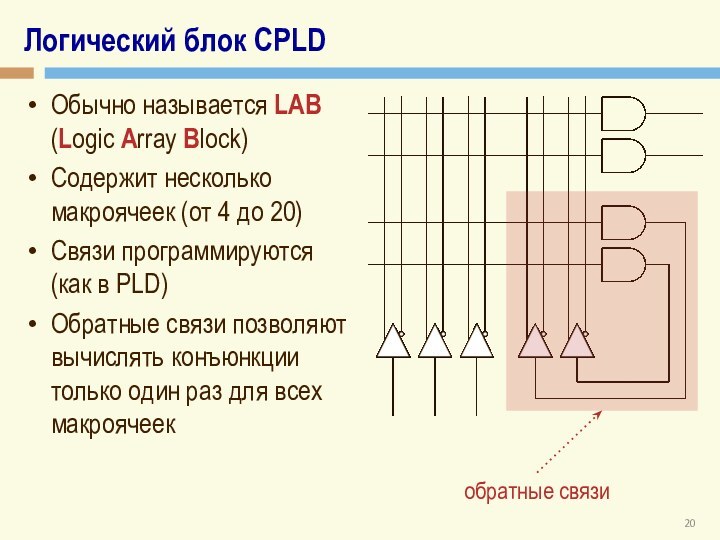

- 20. Логический блок CPLDОбычно называется LAB (Logic Array

- 21. Настраиваемые связиProgrammable Interconnect Array (PI или PIA)Принцип

- 22. Блоки ввода-выводаОбеспечивают интерфейс с внешним миромСоединены с

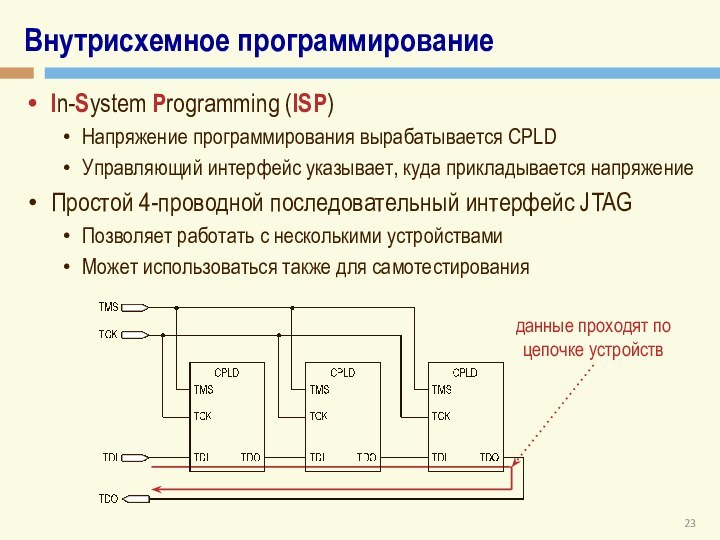

- 23. Внутрисхемное программированиеIn-System Programming (ISP)Напряжение программирования вырабатывается CPLDУправляющий

- 24. Преимущества CPLDНизкая стоимостьБольшая логическая емкостьПрограммируемые внутренние связиГотовы к работе сразу после подачи питанияЭнергонезависимая конфигурацияВозможность многократного программирования

- 25. Что такое FPGA?

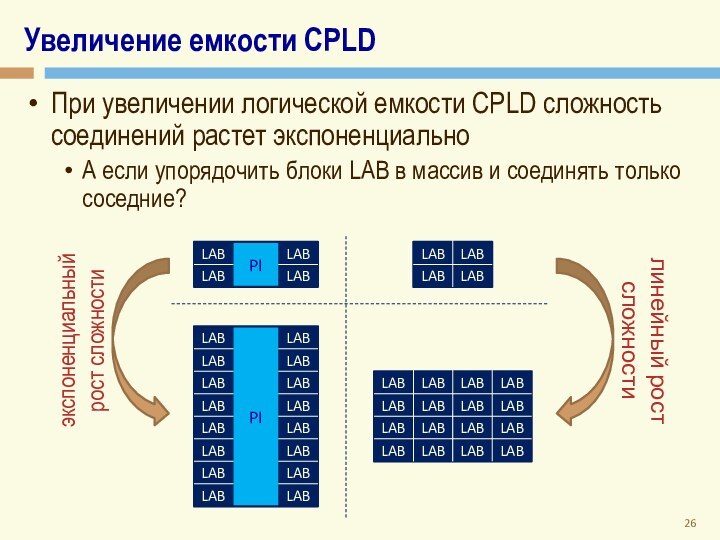

- 26. Увеличение емкости CPLDПри увеличении логической емкости CPLD

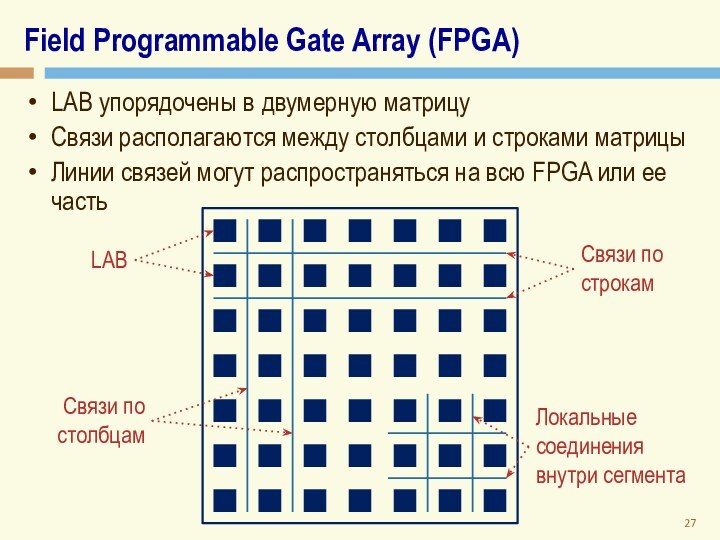

- 27. Field Programmable Gate Array (FPGA)LAB упорядочены в

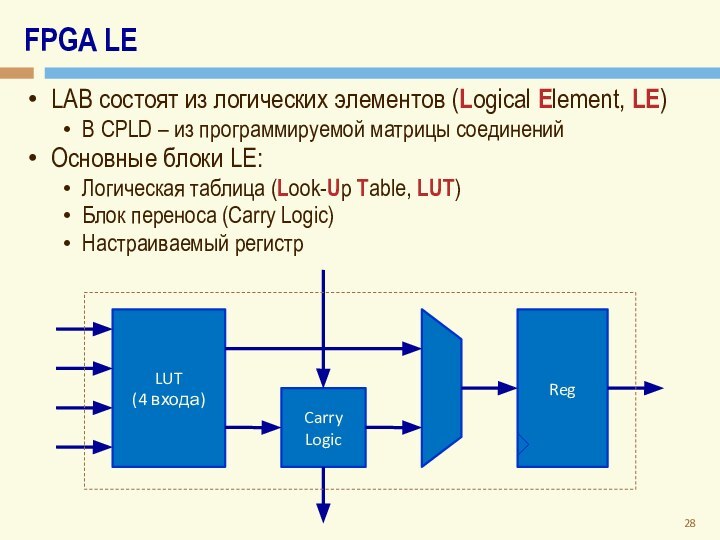

- 28. FPGA LELAB состоят из логических элементов (Logical

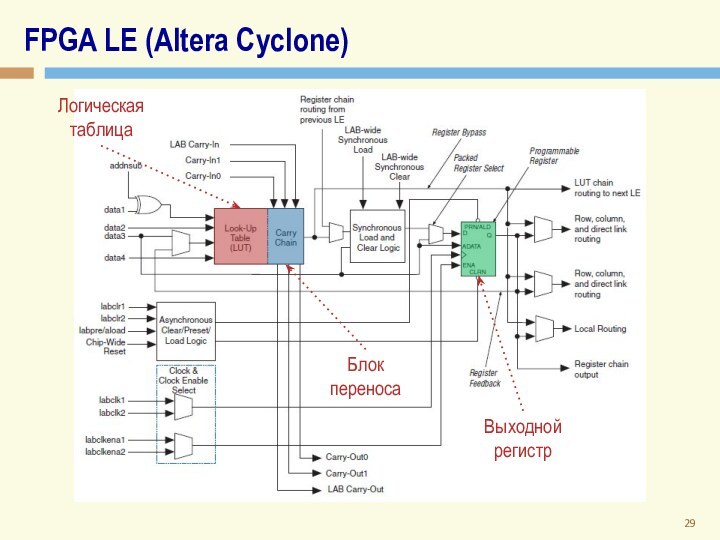

- 29. FPGA LE (Altera Cyclone)Логическая таблицаБлок переносаВыходной регистр

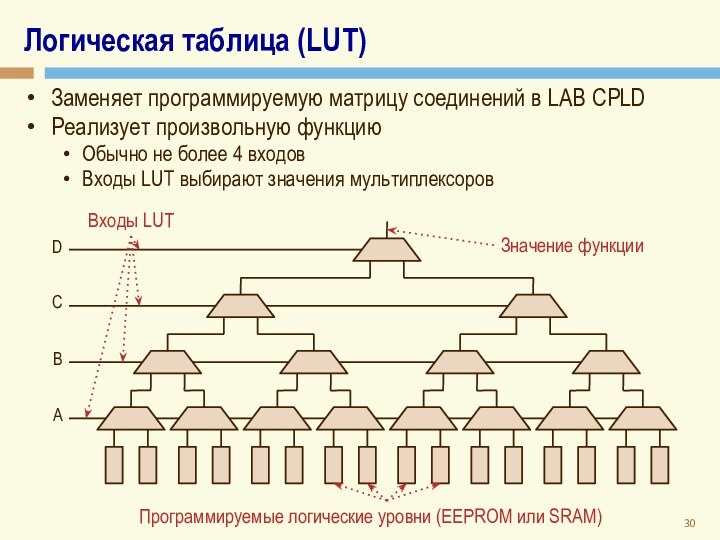

- 30. Логическая таблица (LUT)Заменяет программируемую матрицу соединений в

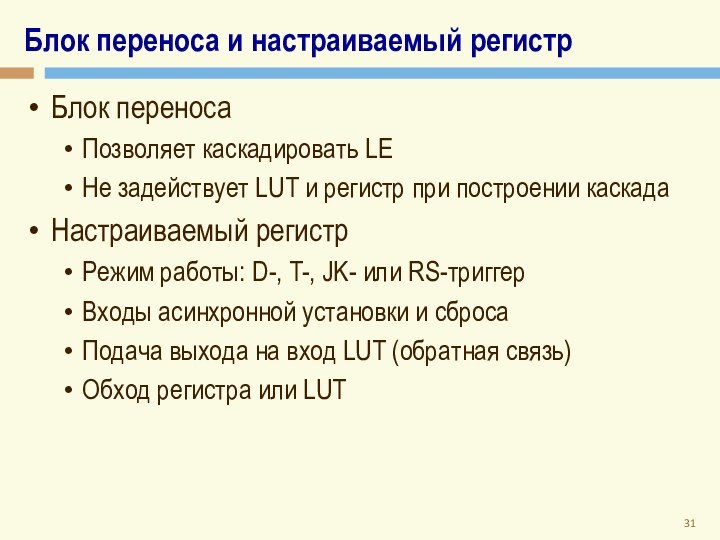

- 31. Блок переноса и настраиваемый регистрБлок переносаПозволяет каскадировать

- 32. Маршрутизация сигналовЛюбой LE может обмениваться информацией с

- 33. Блоки ввода/выводаТакже называются элементами ввода/вывода (I/O elements)Подключены

- 34. Другие особенности FPGAВстроенные блоки памятиУпрощают создание структур

- 35. СинхронизацияОсобенности синхросигналаОчень чувствителен к временным параметрамВысокий коэффициент

- 36. Структуры для работы с синхросигналомБлок фазовой автоподстройки

- 37. Программирование FPGAБольшинство FPGA используют SRAM для задания связей и программирования LUTстолбцыстрокисвязи по строкам и столбцам

- 38. Программирование FPGASRAM является энергозависимойНеобходима инициализация после подачи

- 39. Сравнение CPLD и FPGA

- 40. Аппаратные особенности

- 41. Скачать презентацию

- 42. Похожие презентации

Применение ПЛИС

Слайд 3

Цифровое устройство – дискретные микросхемы

Большое число различных компонентов

Сложные

печатные платы

Слайд 4

Цифровое устройство – ПЛИС

Совмещение различных компонент в одной

МС

Упрощение устройства

Возможность введения новых функций без изменения конструкции

Снижение стоимости

и энергопотребления

Слайд 5

Некоторые сферы применения

Бытовая техника

Обработка сигналов

Цифровое телевидение

Промышленность

САР / САУ

Измерительное

оборудование

Телекоммуникации

Коммутационное оборудование

Безопасность

Защищенные системы связи

Специальные электронные устройства

Слайд 7

Дискретная TTL-логика

Примитивы реализованы в отдельных микросхемах:

NAND, OR, …

мультиплексоры,

дешифраторы, сумматоры…

триггеры, регистры, …

Конструкция устройства определяется ценой и доступной

номенклатурой элементов

Слайд 8

Дискретная TTL-логика (разработка)

Произвольная логическая функция

Логическая функция в заданном

базисе

Схемотехническая реализация

Перевод в базис имеющихся элементов

Минимальная логическая функция

Минимизация логической

функцииРазработка схемы устройства

Слайд 10

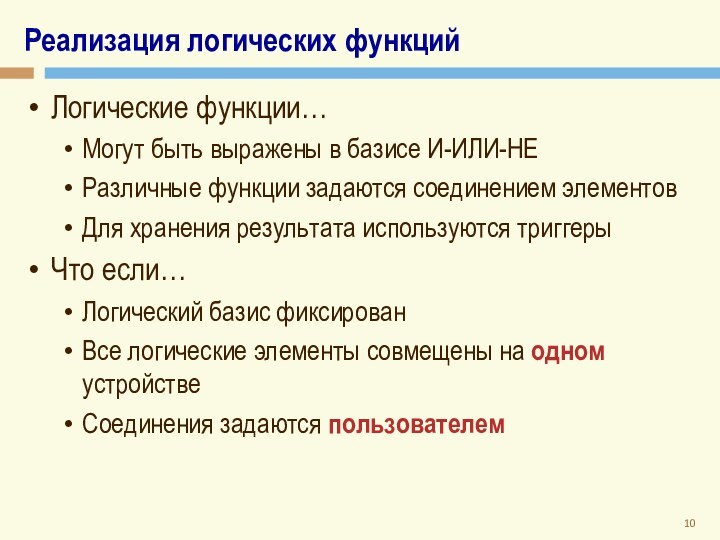

Реализация логических функций

Логические функции…

Могут быть выражены в базисе

И-ИЛИ-НЕ

Различные функции задаются соединением элементов

Для хранения результата используются триггеры

Что

если…Логический базис фиксирован

Все логические элементы совмещены на одном устройстве

Соединения задаются пользователем

Слайд 11

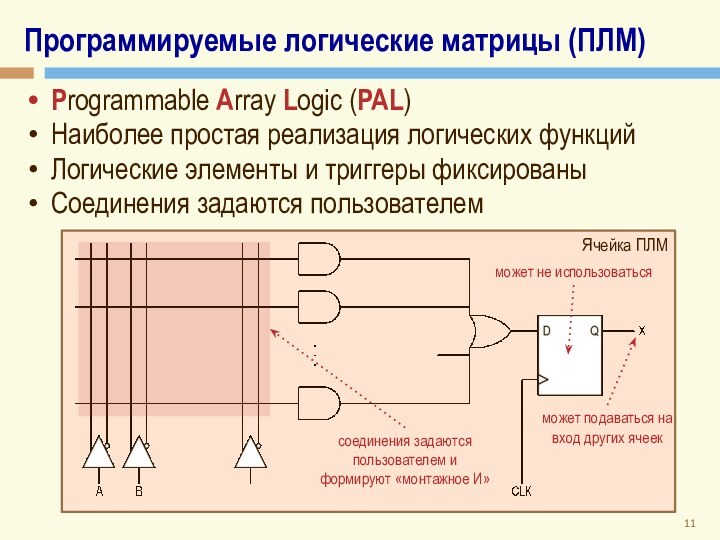

Ячейка ПЛМ

Программируемые логические матрицы (ПЛМ)

Programmable Array Logic (PAL)

Наиболее

простая реализация логических функций

Логические элементы и триггеры фиксированы

Соединения задаются

пользователемможет подаваться на вход других ячеек

соединения задаются пользователем и формируют «монтажное И»

может не использоваться

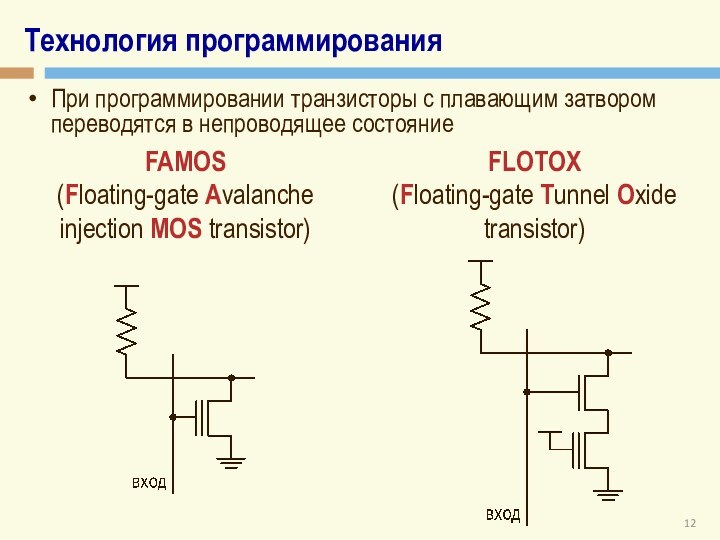

Слайд 12

Технология программирования

FAMOS

(Floating-gate Avalanche injection MOS transistor)

FLOTOX

(Floating-gate Tunnel Oxide

transistor)

При программировании транзисторы с плавающим затвором переводятся в непроводящее

состояние

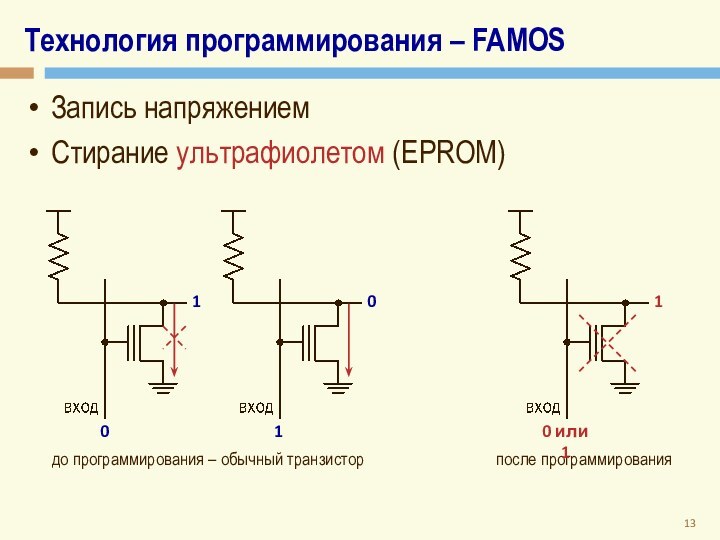

Слайд 13

Технология программирования – FAMOS

Запись напряжением

Стирание ультрафиолетом (EPROM)

до программирования

– обычный транзистор

после программирования

0

1

1

0

0 или 1

1

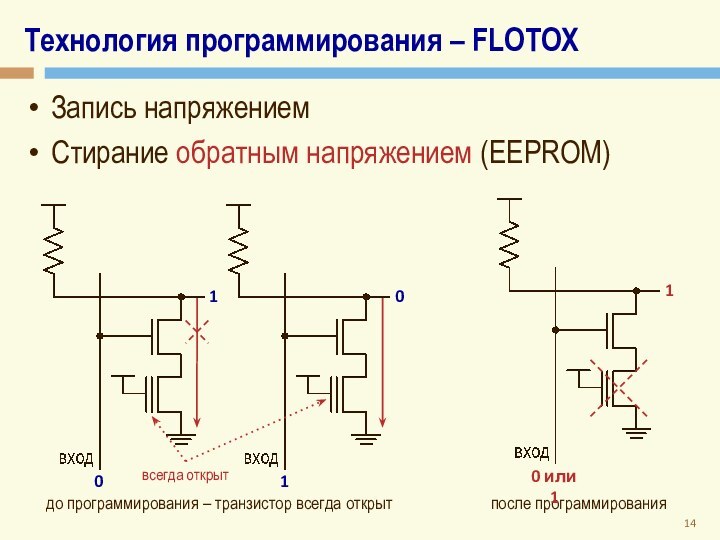

Слайд 14

Технология программирования – FLOTOX

Запись напряжением

Стирание обратным напряжением (EEPROM)

до

программирования – транзистор всегда открыт

после программирования

0

1

0

1

всегда открыт

0 или 1

1

Слайд 15

Преимущества программируемой логики

Снижение числа микросхем

Ниже стоимость и энергопотребление

Меньше

занимаемая площадь

Повышение безопасности

Труднее восстановить схему

Простота внесения изменений

Совместимость по выводам

микросхемМногократное программирование (в том числе внутрисхемное)

Наличие средств автоматизированного проектирования

Слайд 17

От PAL к PLD

PLD (Programmable Logic Device) –

соединение нескольких программируемых логических матриц в одном устройстве

различное число

аргументовнастраиваемые

макроячейки

Слайд 18

Настраиваемая макроячейка

двунаправленный режим

комбинационный или регистровый выход

реализация обратной связи

Слайд 20

Логический блок CPLD

Обычно называется LAB (Logic Array Block)

Содержит

несколько макроячеек (от 4 до 20)

Связи программируются (как в

PLD)Обратные связи позволяют вычислять конъюнкции только один раз для всех макроячеек

обратные связи

Слайд 21

Настраиваемые связи

Programmable Interconnect Array (PI или PIA)

Принцип аналогичен

ПЛМ

Глобальные связи позволяют соединить любой сигнал с любым другим:

Между

логическими блоками (LAB)Между логическими блоками и выводами микросхемы

Программирование по технологии EPROM / EEPROM / Flash

Слайд 22

Блоки ввода-вывода

Обеспечивают интерфейс с внешним миром

Соединены с логическими

блоками через PIA (в PLD – напрямую)

Различные режимы ввода-вывода

Pull-up

или pull-downНесколько стандартов

Направление: входной, выходной или двунаправленный (через тристабильные буферы)

Слайд 23

Внутрисхемное программирование

In-System Programming (ISP)

Напряжение программирования вырабатывается CPLD

Управляющий интерфейс

указывает, куда прикладывается напряжение

Простой 4-проводной последовательный интерфейс JTAG

Позволяет работать

с несколькими устройствамиМожет использоваться также для самотестирования

данные проходят по цепочке устройств

Слайд 24

Преимущества CPLD

Низкая стоимость

Большая логическая емкость

Программируемые внутренние связи

Готовы к

работе сразу после подачи питания

Энергонезависимая конфигурация

Возможность многократного программирования

Слайд 26

Увеличение емкости CPLD

При увеличении логической емкости CPLD сложность

соединений растет экспоненциально

А если упорядочить блоки LAB в массив

и соединять только соседние?экспоненциальный рост сложности

линейный рост сложности

Слайд 27

Field Programmable Gate Array (FPGA)

LAB упорядочены в двумерную

матрицу

Связи располагаются между столбцами и строками матрицы

Линии связей могут

распространяться на всю FPGA или ее частьLAB

Связи по столбцам

Связи по строкам

Локальные соединения внутри сегмента

Слайд 28

FPGA LE

LAB состоят из логических элементов (Logical Element,

LE)

В CPLD – из программируемой матрицы соединений

Основные блоки LE:

Логическая

таблица (Look-Up Table, LUT)Блок переноса (Carry Logic)

Настраиваемый регистр

Слайд 30

Логическая таблица (LUT)

Заменяет программируемую матрицу соединений в LAB

CPLD

Реализует произвольную функцию

Обычно не более 4 входов

Входы LUT выбирают

значения мультиплексоровВходы LUT

Значение функции

Программируемые логические уровни (EEPROM или SRAM)

Слайд 31

Блок переноса и настраиваемый регистр

Блок переноса

Позволяет каскадировать LE

Не

задействует LUT и регистр при построении каскада

Настраиваемый регистр

Режим работы:

D-, T-, JK- или RS-триггерВходы асинхронной установки и сброса

Подача выхода на вход LUT (обратная связь)

Обход регистра или LUT

Слайд 32

Маршрутизация сигналов

Любой LE может обмениваться информацией с любым

другим LE

Локальные соединения

Соединяют LE внутри LAB

Могут также соединять соседние

LAB в FPGAСвязи по столбцам и строкам

Состоят из сегментов фиксированной длины

Охватывают несколько LAB или всю FPGA

Слайд 33

Блоки ввода/вывода

Также называются элементами ввода/вывода (I/O elements)

Подключены напрямую

к связям по срокам и столбцам

Обеспечивают настраиваемый ввод/вывод

Направление (вход

/ выход / двунаправленный)Стандарт (LVTTL, LVCMOS, PCI, …)

Формирование дифференциального сигнала

Выходной ток

Pull-up / pull-down

…

Слайд 34

Другие особенности FPGA

Встроенные блоки памяти

Упрощают создание структур памяти

(RAM, ROM, …)

Могут быть инициализированы при подаче питания

Аппаратные умножители

Используются

в DSPВысокоскоростные операции умножения / сложения

Высокоскоростные трансиверы

Замена некоторых LAB специализированными блоками

Слайд 35

Синхронизация

Особенности синхросигнала

Очень чувствителен к временным параметрам

Высокий коэффициент разветвления

Маршрутизация

синхросигнала

Отдельные выводы микросхемы FPGA

Отдельная сеть маршрутизации (clock routing network)

Глобальная

сеть снабжает всю FPGAРегиональные сети обслуживают отдельные области FPGA

Специальные структуры для работы с синхросигналом

Блоки фазовой автоподстройки частоты (PLL)

Блоки управления синхросигналом

Слайд 36

Структуры для работы с синхросигналом

Блок фазовой автоподстройки частоты

(Phase-Locked Loop, PLL)

Умножение и деление частоты

Сдвиг фазы

Настраиваемая скважность

Переключение между

несколькими входными синхросигналамиРазличные режимы компенсации задержек

Блок управления синхросигналом (Clock Control Block, CCB)

Является промежуточным звеном между источником синхросигнала (выводом МС, PLL или внутренней логикой) и глобальной сетью маршрутизации

Позволяет динамически выбирать источник синхросигнала

Обеспечивает отключение сети при необходимости

Слайд 37

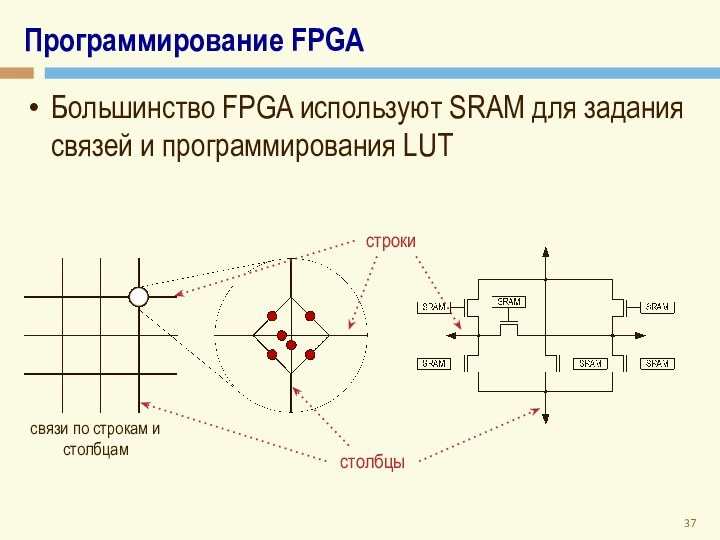

Программирование FPGA

Большинство FPGA используют SRAM для задания связей

и программирования LUT

столбцы

строки

связи по строкам и столбцам

Слайд 38

Программирование FPGA

SRAM является энергозависимой

Необходима инициализация после подачи питания

Долговременное

хранение конфигурации вне FPGA

Режимы программирования:

Активный: управляется FPGA после подачи

питанияПассивный: управляется внешним устройством (CPLD, CPU, …)

Возможно программирование по интерфейсу JTAG