- Главная

- Разное

- Бизнес и предпринимательство

- Образование

- Развлечения

- Государство

- Спорт

- Графика

- Культурология

- Еда и кулинария

- Лингвистика

- Религиоведение

- Черчение

- Физкультура

- ИЗО

- Психология

- Социология

- Английский язык

- Астрономия

- Алгебра

- Биология

- География

- Геометрия

- Детские презентации

- Информатика

- История

- Литература

- Маркетинг

- Математика

- Медицина

- Менеджмент

- Музыка

- МХК

- Немецкий язык

- ОБЖ

- Обществознание

- Окружающий мир

- Педагогика

- Русский язык

- Технология

- Физика

- Философия

- Химия

- Шаблоны, картинки для презентаций

- Экология

- Экономика

- Юриспруденция

Что такое findslide.org?

FindSlide.org - это сайт презентаций, докладов, шаблонов в формате PowerPoint.

Обратная связь

Email: Нажмите что бы посмотреть

Презентация на тему Проектирование цифровых устройств на языке vhdl

Содержание

- 2. Комбинационные схемыСдвиговыеСдвиг влево / вправоВращение влево / вправоЛогическиеРеализация булевых функцийАрифметическиеСложение, вычитаниеУмножение, делениеСхемотехническиеМультиплексоры, демультиплексорыШифраторы, дешифраторыКлассификация условная

- 3. Структура цифрового устройстваКомбинационная логикаРегистры

- 4. Стили описания на VHDLСтильПотоков данных (dataflow)Структурный(structural)«параллельные» операторыкомпоненты и связи«последовательные» операторы

- 5. Арифметические и логические операторы, операторы отношений

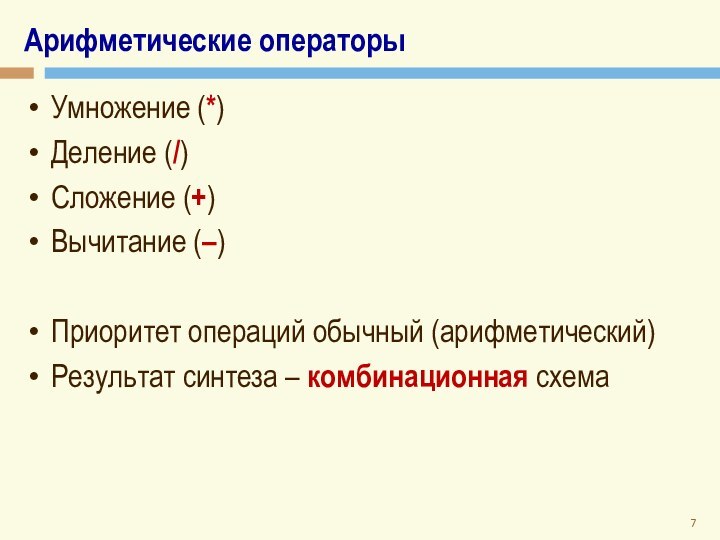

- 6. Основные операторыnot* /+ -

- 7. Арифметические операторыУмножение (*)Деление (/)Сложение (+)Вычитание (–)Приоритет операций обычный (арифметический)Результат синтеза – комбинационная схема

- 8. Пакеты IEEEstd_logic_1164Стандарт IEEEОпределяет типы std_logic и std_logic_vectorПример:

- 9. Пакеты IEEEstd_logic_unsignedНе является стандартом (разработан Synopsys)Заставляет компилятор

- 10. Пакеты IEEEnumeric_stdСтандарт IEEEОпределяет типы signed и unsignedОписывает арифметические операцииНесовместим с пакетом std_logic_arith

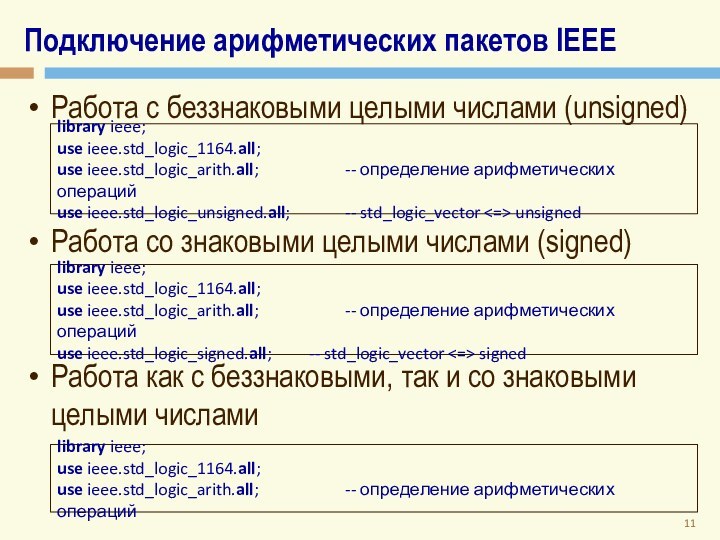

- 11. Подключение арифметических пакетов IEEEРабота с беззнаковыми целыми

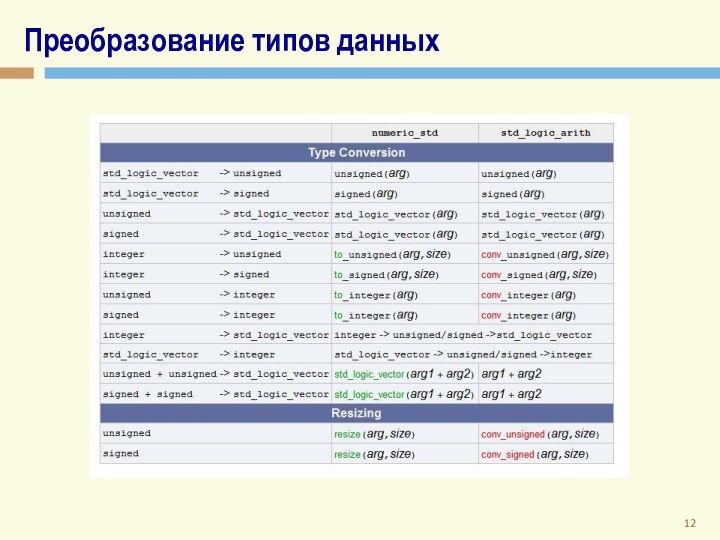

- 12. Преобразование типов данных

- 13. Присваивание

- 14. ПрисваиваниеПростое присваиваниеУсловное присваивание (when-else)Выборочное присваивание (with-select-when)

- 15. Простое присваиваниеОператор

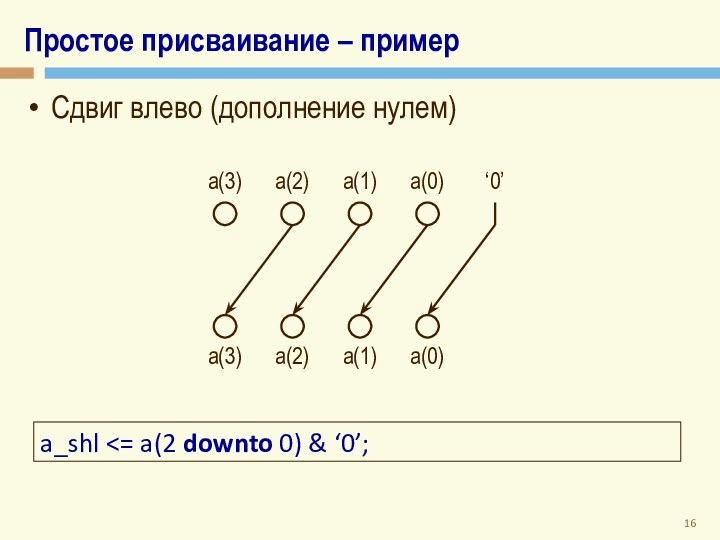

- 16. Простое присваивание – примерСдвиг влево (дополнение нулем)a_shl

- 17. Простое присваивание – примерВращение вправоa_ror

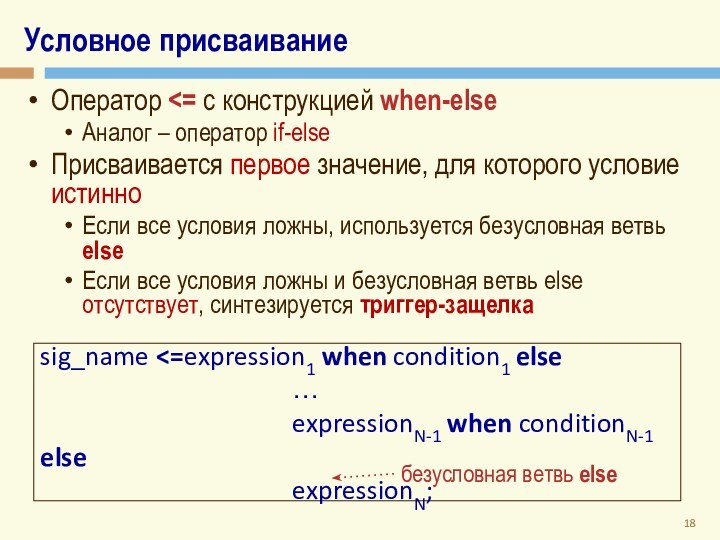

- 18. Условное присваиваниеОператор

- 19. Условное присваиваниеsig_name

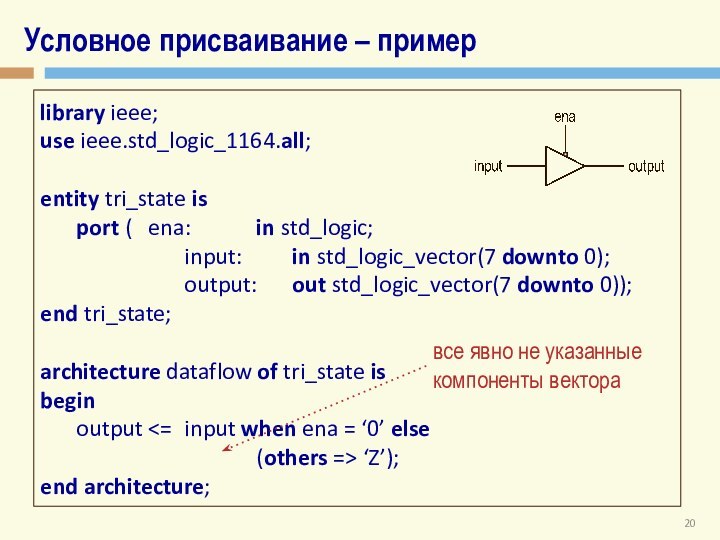

- 20. Условное присваивание – примерlibrary ieee;use ieee.std_logic_1164.all;entity tri_state

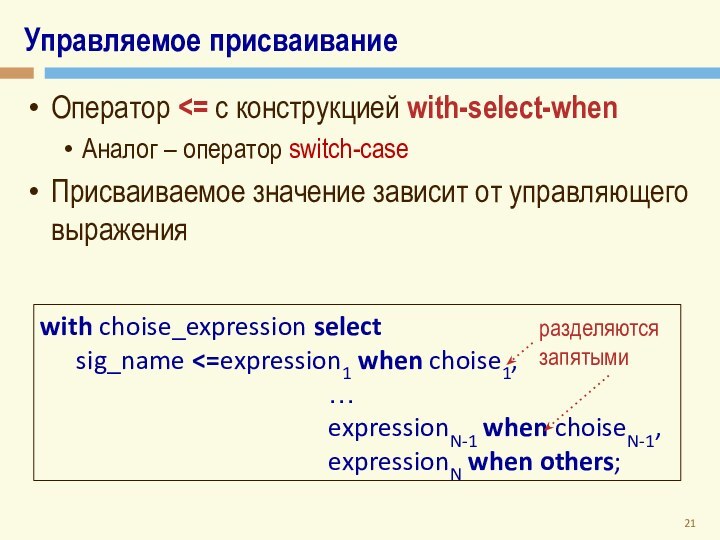

- 21. Управляемое присваиваниеОператор

- 22. Управляемое присваиваниеwith choise_expression select sig_name

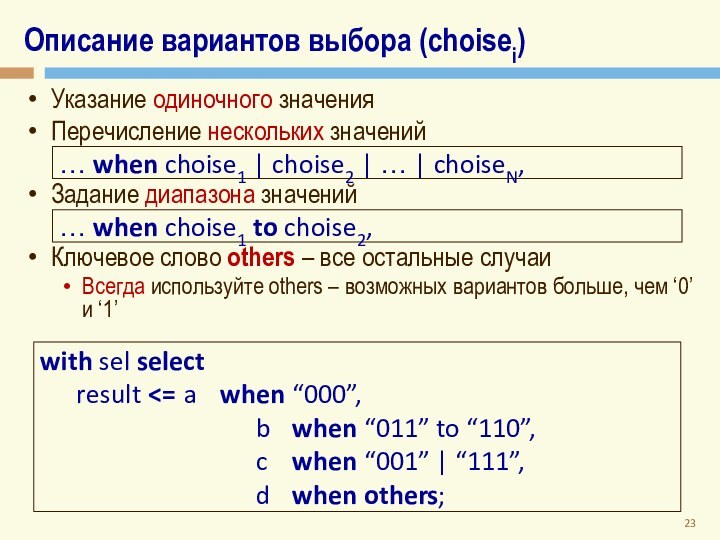

- 23. Описание вариантов выбора (choisei)Указание одиночного значенияПеречисление нескольких

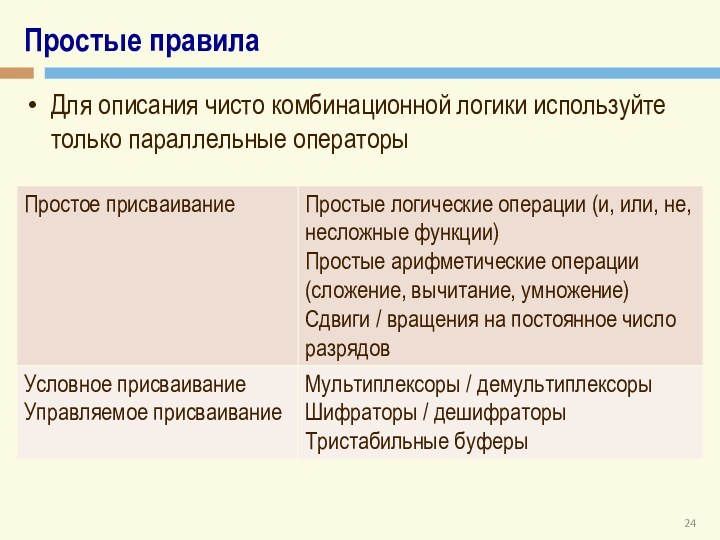

- 24. Простые правилаДля описания чисто комбинационной логики используйте только параллельные операторы

- 25. Генерация выражений

- 26. Генерация выраженийКонструкция for-generateКонструкция if-generatelabel: for var in range generate concurrent statements end generate;label: if condition generate concurrent statements end generate;

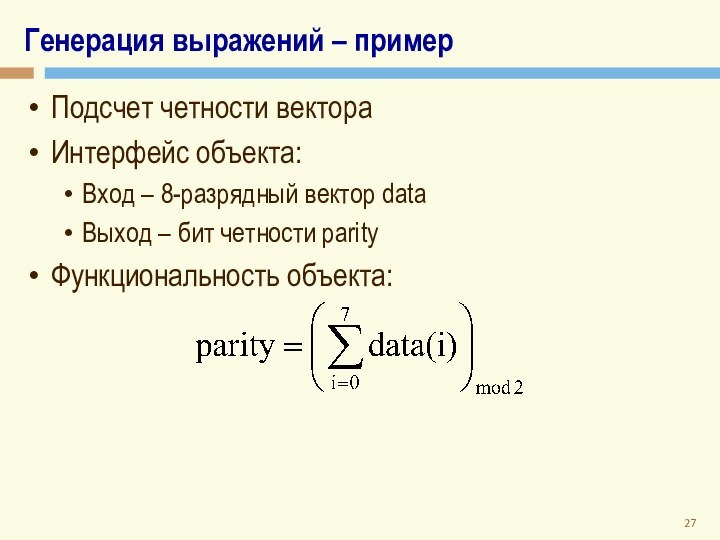

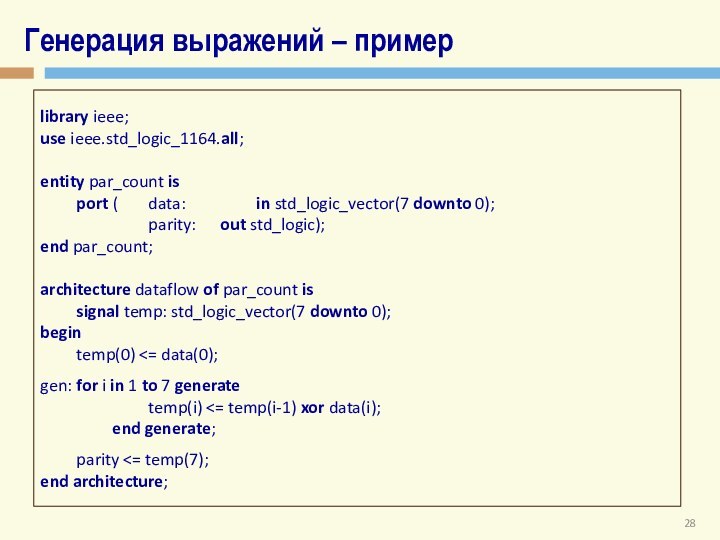

- 27. Генерация выражений – примерПодсчет четности вектораИнтерфейс объекта:Вход – 8-разрядный вектор dataВыход – бит четности parityФункциональность объекта:

- 28. Скачать презентацию

- 29. Похожие презентации

Слайд 2

Комбинационные схемы

Сдвиговые

Сдвиг влево / вправо

Вращение влево / вправо

Логические

Реализация

булевых функций

Слайд 4

Стили описания на VHDL

Стиль

Потоков данных (dataflow)

Структурный

(structural)

«параллельные» операторы

компоненты и

связи

«последовательные» операторы

Слайд 6

Основные операторы

not

* /

+ - &

sll

srl sla sra ror rol

= /=

<= > >=and or nand nor xor xnor

не равно

VHDL-93

конкатенация

Слайд 7

Арифметические операторы

Умножение (*)

Деление (/)

Сложение (+)

Вычитание (–)

Приоритет операций обычный

(арифметический)

Результат синтеза – комбинационная схема

Слайд 8

Пакеты IEEE

std_logic_1164

Стандарт IEEE

Определяет типы std_logic и std_logic_vector

Пример: std_logic_vector(7

downto 0)

Описывает логические операции

std_logic_arith

Не является стандартом (разработан Synopsys)

Определяет типы

signed (знаковое целое) и unsigned (беззнаковое целое)Пример: unsigned(7 downto 0)

Описывает арифметические операции

Слайд 9

Пакеты IEEE

std_logic_unsigned

Не является стандартом (разработан Synopsys)

Заставляет компилятор интерпретировать

std_logic_vector как unsigned

std_logic_signed

Не является стандартом (разработан Synopsys)

Заставляет компилятор интерпретировать

std_logic_vector как signedНе используйте одновременно std_logic_unsigned и std_logic_signed

Преобразования типов можно выполнять явно

Слайд 10

Пакеты IEEE

numeric_std

Стандарт IEEE

Определяет типы signed и unsigned

Описывает арифметические

операции

Несовместим с пакетом std_logic_arith

Слайд 11

Подключение арифметических пакетов IEEE

Работа с беззнаковыми целыми числами

(unsigned)

Работа со знаковыми целыми числами (signed)

Работа как с беззнаковыми,

так и со знаковыми целыми числамиlibrary ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all; -- определение арифметических операций

use ieee.std_logic_unsigned.all; -- std_logic_vector <=> unsigned

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all; -- определение арифметических операций

use ieee.std_logic_signed.all; -- std_logic_vector <=> signed

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_arith.all; -- определение арифметических операций

Слайд 14

Присваивание

Простое присваивание

Условное присваивание (when-else)

Выборочное присваивание (with-select-when)

Слайд 18

Условное присваивание

Оператор

if-else

Присваивается первое значение, для которого условие истинно

Если все условия

ложны, используется безусловная ветвь elseЕсли все условия ложны и безусловная ветвь else отсутствует, синтезируется триггер-защелка

sig_name <= expression1 when condition1 else

…

expressionN-1 when conditionN-1 else

expressionN;

безусловная ветвь else

Слайд 20

Условное присваивание – пример

library ieee;

use ieee.std_logic_1164.all;

entity tri_state is

port

( ena: in std_logic;

input: in std_logic_vector(7 downto 0);

output: out std_logic_vector(7 downto 0));

end tri_state;

architecture

dataflow of tri_state isbegin

output <= input when ena = ‘0’ else

(others => ‘Z’);

end architecture;

все явно не указанные компоненты вектора

Слайд 21

Управляемое присваивание

Оператор

switch-case

Присваиваемое значение зависит от управляющего выражения

with choise_expression select

sig_name

when choise1,…

expressionN-1 when choiseN-1,

expressionN when others;

разделяются запятыми

Слайд 22

Управляемое присваивание

with choise_expression select

sig_name

choiseN-1,

expressionN when others;

Слайд 23

Описание вариантов выбора (choisei)

Указание одиночного значения

Перечисление нескольких значений

Задание

диапазона значений

Ключевое слово others – все остальные случаи

Всегда используйте

others – возможных вариантов больше, чем ‘0’ и ‘1’with sel select

result <= a when “000”,

b when “011” to “110”,

c when “001” | “111”,

d when others;

… when choise1 | choise2 | … | choiseN,

… when choise1 to choise2,