Слайд 2

Архитектура ПК

Архитектурой принято называть

совокупность всех программно доступных

аппаратных средств процессора.

Понятие архитектуры является комплексным и включает в

себя

структурную схему компьютера;

средства и способы доступа к элементам структурной схемы;

организацию и разрядность интерфейсов;

набор регистров;

организацию и способы адресации памяти;

способы представления и форматы данных;

набор машинных команд;

форматы машинных команд;

обработку прерываний.

Слайд 3

В основе любого устройства лежат

базовые принципы, на

основе которых в дальнейшем строится система

Набор этих принципов

часто называется архитектурными принципами

Рассмотрим архитектурные принципы, положенные в основу компьютерной техники

Слайд 4

Широкое распространение получили персональные компьютеры производства

компании Apple

Computer и

компании IBM (International Business Machines).

Слайд 5

Компания Apple производит широко известные компьютеры Macintosh

Особенности

все основные

узлы компьютера размещены на одной плате (поэтому замена узлов

невозможна),

пользователю предоставляются минимальные возможности по вмешательству в работу системы.

Согласно принципу Apple

изготовлением узлов и сборку компьютера должна осуществлять одна фирма,

а настройкой компьютера и заменой его узлов должны заниматься только профессионалы.

⇒ высокое качество и надежность ПК Macintosh.

Слайд 6

IBM-совместимые компьютеры

строятся на базе принципа открытой архитектуры:

компьютер

составлен из отдельных узлов (блоков),

пользователю предоставляются широкие возможности

изменять состав компьютера, заменяя одни узлы другими

Производством узлов для IBM-совместимых компьютеров и сборкой самих компьютеров занимаются фирмы из разных стран.

Такой подход к построению компьютера предоставляет

1) возможности для массового производства

2) широкие возможности дальнейшего совершенствования

Слайд 7

Компьютеры, не совместимые с IBM PC

Например,

компьютер Power PC

с процессором производства корпорации Motorola

Слайд 8

Общие архитектурные

свойства и принципы

Эти свойства и принципы

присущи всем современным машинам фон-неймановской архитектуры.

Принцип хранимой программы

Код программы

и ее данные находятся в едином адресном пространстве в ОП.

С точки зрения процессора нет принципиальной разницы между данными и командами.

Принцип микропрограммирования

В состав процессора входит блок микропрограммного управления. Этот блок для каждой машинной команды имеет набор действий-сигналов, которые нужно сгенерировать для физического выполнения требуемой машинной команды.

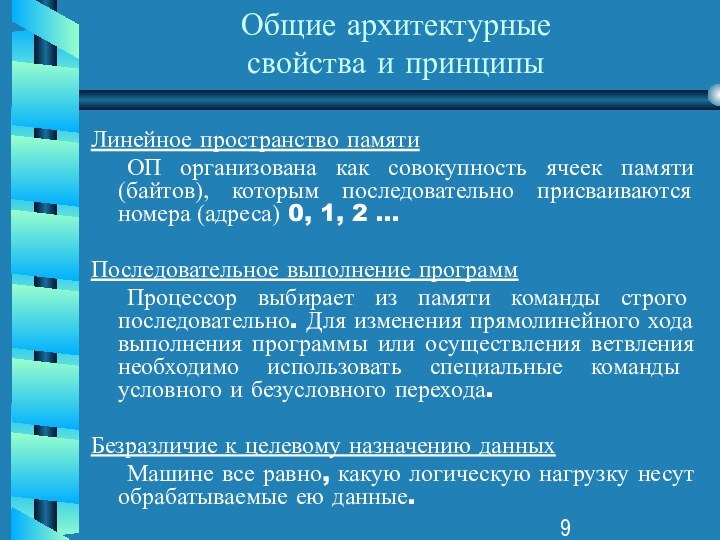

Слайд 9

Общие архитектурные

свойства и принципы

Линейное пространство памяти

ОП организована

как совокупность ячеек памяти (байтов), которым последовательно присваиваются номера

(адреса) 0, 1, 2 …

Последовательное выполнение программ

Процессор выбирает из памяти команды строго последовательно. Для изменения прямолинейного хода выполнения программы или осуществления ветвления необходимо использовать специальные команды условного и безусловного перехода.

Безразличие к целевому назначению данных

Машине все равно, какую логическую нагрузку несут обрабатываемые ею данные.

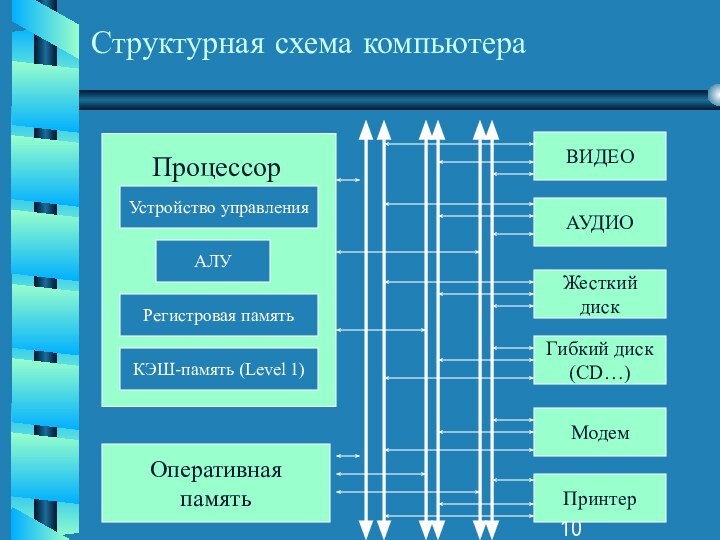

Слайд 10

Структурная схема компьютера

Оперативная

память

Устройство управления

АЛУ

Регистровая память

КЭШ-память (Level 1)

Процессор

ВИДЕО

АУДИО

Жесткий диск

Гибкий

диск

(CD…)

Принтер

Модем

Слайд 11

Материнская плата

Основной элемент компьютера –

материнская (системная) плата

вместе с микропроцессором

Предназначена для

обеспечения бесперебойной работы процессора;

обеспечения эффективной

работы компьютера.

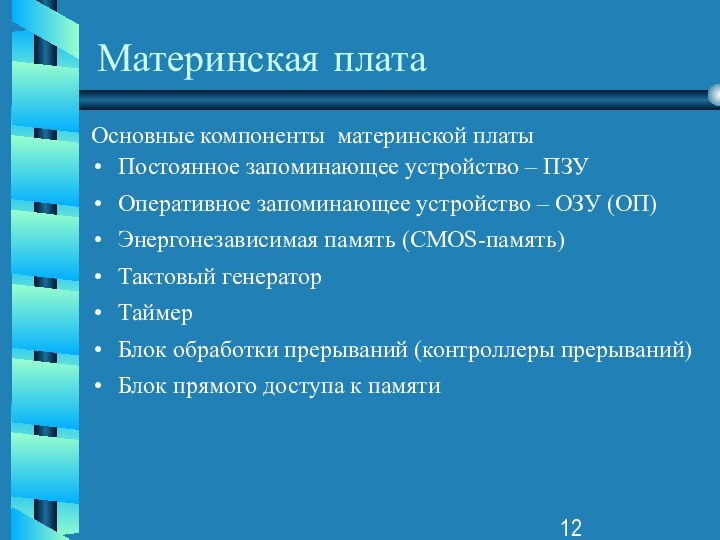

Слайд 12

Материнская плата

Основные компоненты материнской платы

Постоянное запоминающее устройство –

ПЗУ

Оперативное запоминающее устройство – ОЗУ (ОП)

Энергонезависимая память (CMOS-память)

Тактовый генератор

Таймер

Блок

обработки прерываний (контроллеры прерываний)

Блок прямого доступа к памяти

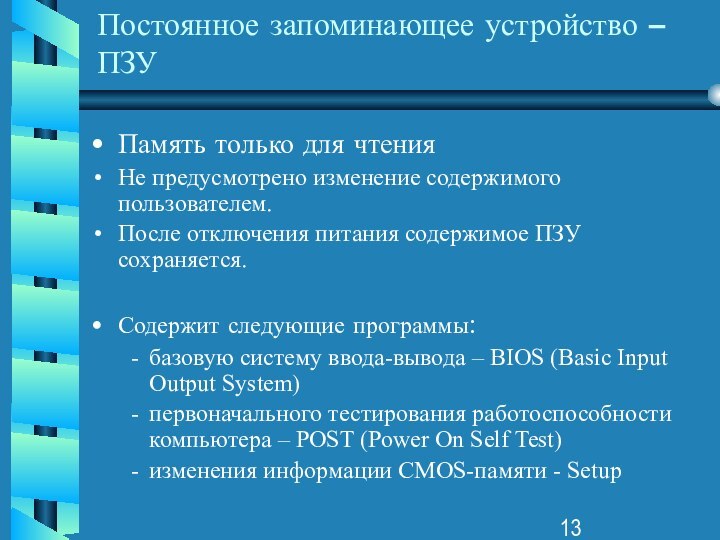

Слайд 13

Постоянное запоминающее устройство – ПЗУ

Память только для чтения

Не

предусмотрено изменение содержимого пользователем.

После отключения питания содержимое ПЗУ

сохраняется.

Содержит следующие программы:

базовую систему ввода-вывода – BIOS (Basic Input Output System)

первоначального тестирования работоспособности компьютера – POST (Power On Self Test)

изменения информации CMOS-памяти - Setup

Слайд 14

Энергонезависимая память

(CMOS-память)

Хранится информация

об устройствах системы и

их параметрах (дисковая подсистема);

необходимая при каждом запуске (например, порядок

загрузки компьютера)

Слайд 15

Системные шины

Шина (bus) – общий канал связи, соединяющий

отдельные части компьютера (пучок проводов)

Перенос информации происходит по параллельным

линиям (проводам).

Один бит – одна линия.

Их количество называют шириной шины.

Шина адреса

Шина данных

Шина управления

Слайд 16

Системные шины

Передаваемую информацию можно условно разделить на 3

вида:

Данные – обрабатываемые числовые значения.

Адреса – сведения о местонахождении

данных.

Управляющие сигналы – указывают направление потокам данных и регламентируют обмен данными.

Набор линий, предназначенных для передачи одного вида информации, называют шиной.

Шина адреса

Шина данных

Шина управления

Слайд 17

Шина управления

Микропроцессор выставляет на шине управления

команды управления

узлами системы и получает ответные сигналы состояния узлов и

подтверждение выполнения команды

Слайд 18

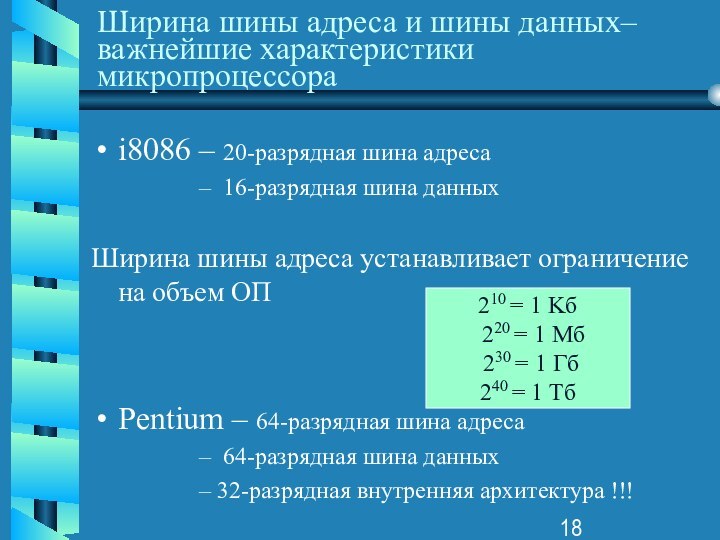

Ширина шины адреса и шины данных– важнейшие характеристики

микропроцессора

i8086 – 20-разрядная шина адреса

16-разрядная шина данных

Ширина шины

адреса устанавливает ограничение на объем ОП

Pentium – 64-разрядная шина адреса

64-разрядная шина данных

32-разрядная внутренняя архитектура !!!

210 = 1 Kб

220 = 1 Мб

230 = 1 Гб

240 = 1 Тб

Слайд 19

Внутренняя шина

Три шины вместе (шина адреса, шина данных,

шина управления) составляют процессорную (внутреннюю) шину

Шина адреса и шина

управления – однонаправленные (передача в одном направлении - из микропроцессора)

Шина данных – двунаправленная (данные считываются и выдается результат)

Слайд 20

Системная шина

Микропроцессор напрямую работает только с несколькими устройствами,

а от остальных отделен специальными микросхемами-буферами (для усиления проходящих

сигналов).

После буферов шины адреса, данных и управления совместно с некоторыми дополнительными сигналами образуют другой канал обмена информацией – СИСТЕМНУЮ ШИНУ.

Системная шина характеризуется частотой системной шины (образуется из тактовой частоты)

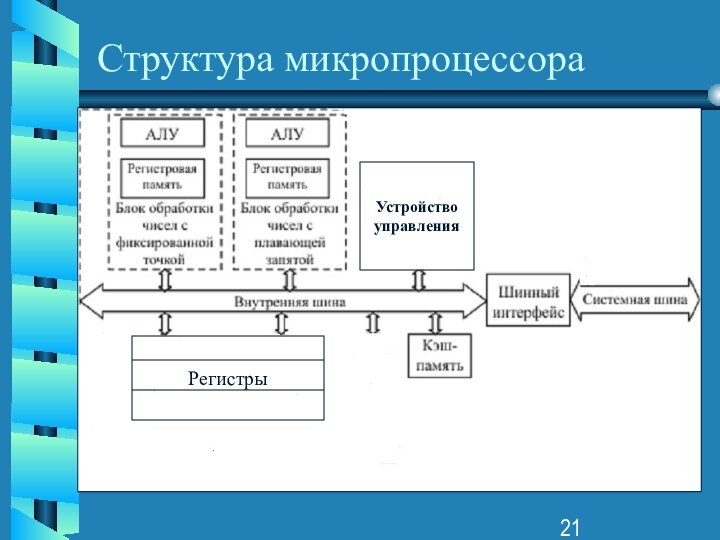

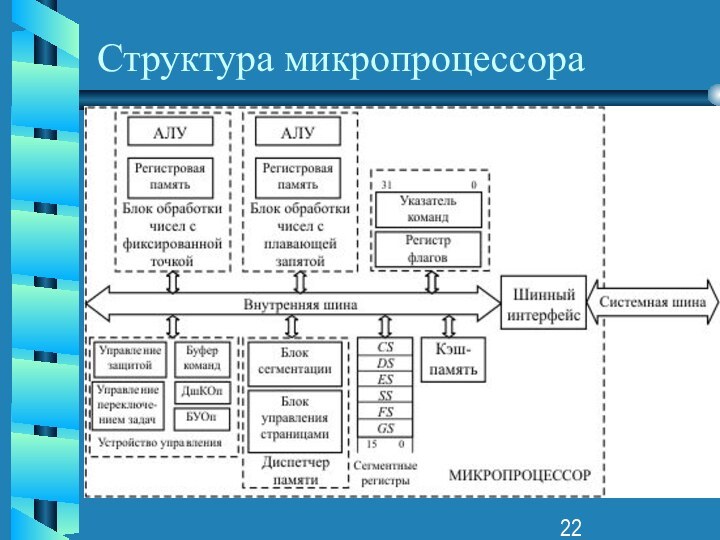

Слайд 21

Структура микропроцессора

Устройство

управления

Регистры

Слайд 23

Тактовая частота

Управление процессором осуществляется с помощью сигналов –

тактовых импульсов, которые выдаются через фиксированные интервалы времени специальным

устройством – тактовым генератором.

Промежуток между тактовыми импульсами – такт.

Такт - минимальная временная единица в системе.

Для выполнения машинной команды процессор подразделяет ее на последовательность шагов, каждый из которых может быть выполнен за один такт.

Длительность одного такта – важнейший параметр,

определяющий производительность процессора (Т)

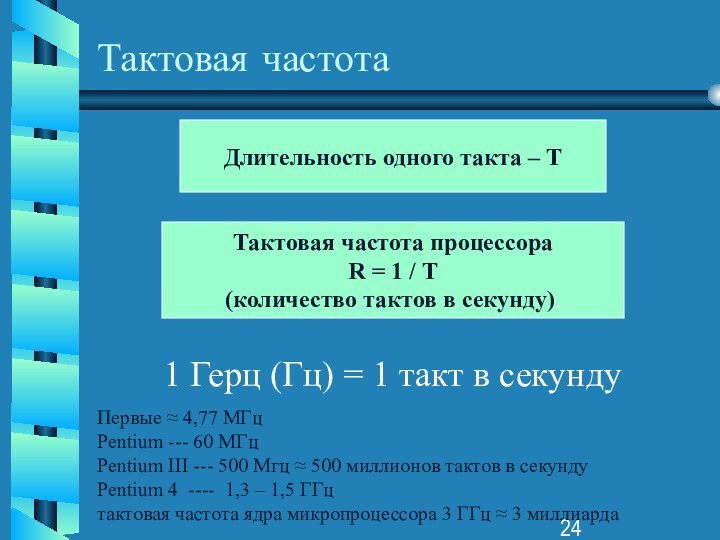

Слайд 24

Тактовая частота

Тактовая частота процессора

R = 1 / T

(количество тактов в секунду).

Длительность одного такта – Т

1 Герц

(Гц) = 1 такт в секунду

Первые ≈ 4,77 МГц

Pentium --- 60 МГц

Pentium III --- 500 Мгц ≈ 500 миллионов тактов в секунду

Pentium 4 ---- 1,3 – 1,5 ГГц

тактовая частота ядра микропроцессора 3 ГГц ≈ 3 миллиарда

Слайд 25

Тактовая частота

Решает задачу синхронизации функционирования всех компонентов системы

(их

действия должны быть «увязаны» между собой, время работы должно

измеряться в одинаковых интервалах)

Тактовая частота используется для формирования

РАБОЧЕЙ (СИСТЕМНОЙ) частоты

(на рабочей частоте процессор взаимодействует с памятью).

Из рабочей частоты образуется частота системных шин.

«Внутри себя» (ядро) микропроцессор работает на более высокой частоте (начиная с i486).

Внутренняя частота процессора образуется путем умножения системной частоты на некоторый коэффициент.

Слайд 26

Мультипроцессорные системы

Система, содержащая несколько (много) процессоров, называется многопроцессорной

(мультипроцессорной)

Процессоры выполняют параллельно несколько задач

(несколько подзадач одной большой задачи)

Все

процессоры имеют доступ ко всей памяти системы – мультипроцессорная система с общей памятью

Высокая производительность

Высокая стоимость (большое количество процессоров, большой объем памяти, сложные схемы управления)

Слайд 27

Мультикомпьютерные системы

Мультикомпьютерные = многомашинные

системы - соединенные группы

компьютеров

Каждому

компьютеру доступна только своя память

Обмен данными через пересылку сообщений

Кластер

– группа компьютеров, объединенных для решения одной задачи

Слайд 28

Элементная база процессора

Процессор состоит из очень большого набора

элементов,

собранных определенным образом.

Каждый элемент – это электронно-техническое

изделие.

В основе конструкции

процессоров лежат элементарные логические микросхемы

Используется несколько базовых логических функций (элементов) и бесчисленное число их комбинаций.

Слайд 29

Элементная база процессора

2 основных класса элементов:

логические

(для вычислений)

запоминающие (для хранения)

Слайд 30

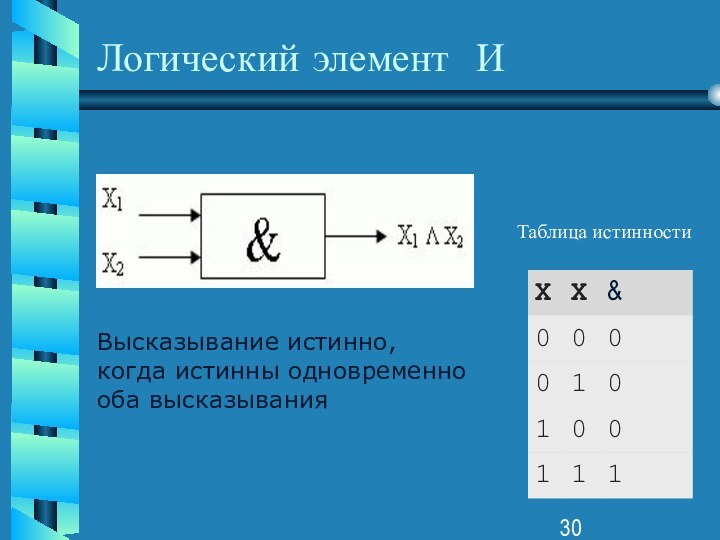

Логический элемент И

Высказывание истинно, когда истинны одновременно оба

высказывания

Таблица истинности

Слайд 31

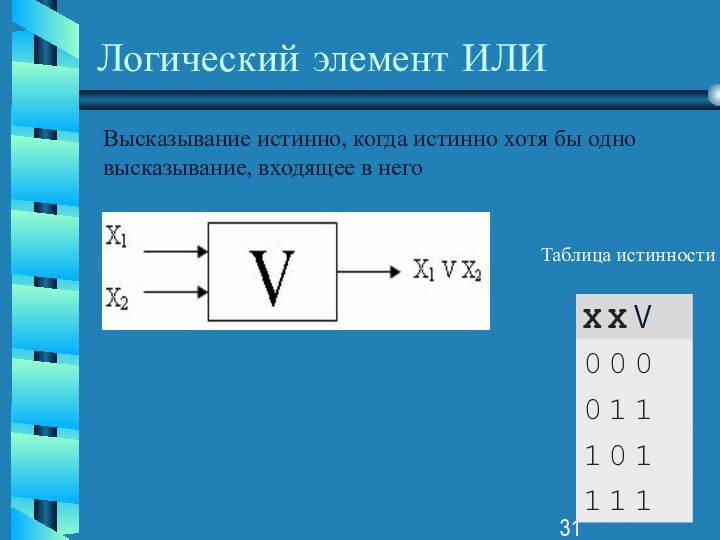

Логический элемент ИЛИ

Высказывание истинно, когда истинно хотя бы

одно высказывание, входящее в него

Таблица истинности

Слайд 32

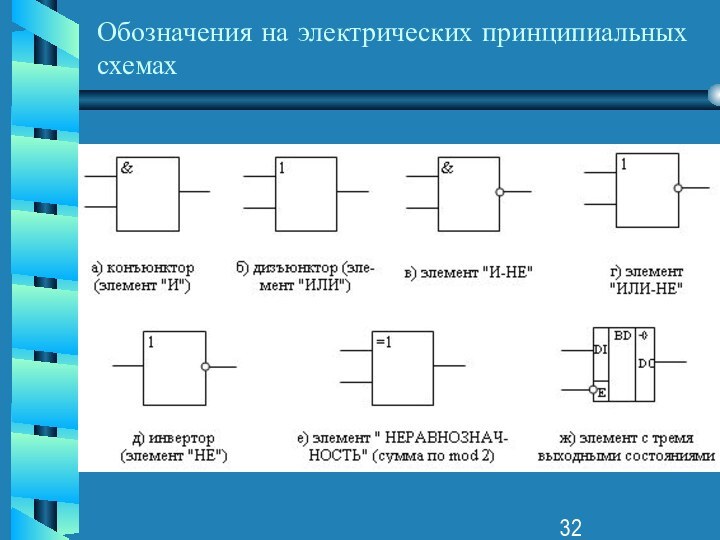

Обозначения на электрических принципиальных схемах

Слайд 33

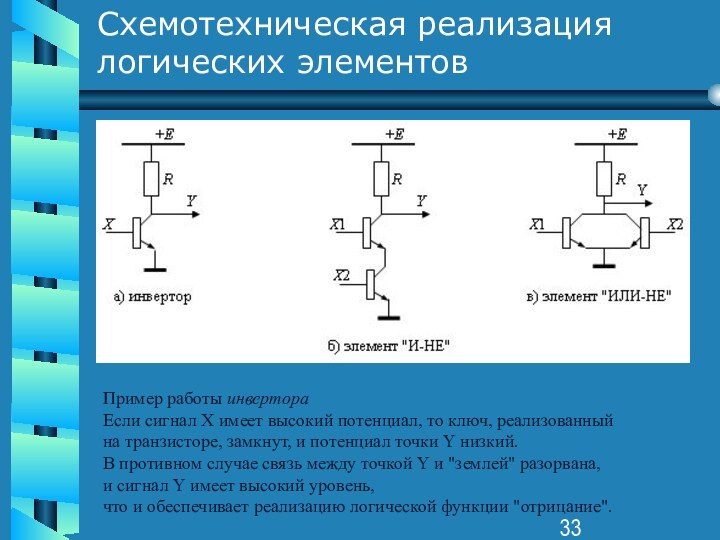

Схемотехническая реализация логических элементов

Пример работы инвертора

Если сигнал X

имеет высокий потенциал, то ключ, реализованный

на транзисторе, замкнут,

и потенциал точки Y низкий.

В противном случае связь между точкой Y и "землей" разорвана,

и сигнал Y имеет высокий уровень,

что и обеспечивает реализацию логической функции "отрицание".

Слайд 34

Запоминающие элементы

Базовый запоминающий элемент в электротехнике – ТРИГГЕР

Триггер

используется для хранения одного бита информации

Его задача – запомнить,

что было на его входе – 1 или 0, и сообщить об этом, когда спросят.

Слайд 35

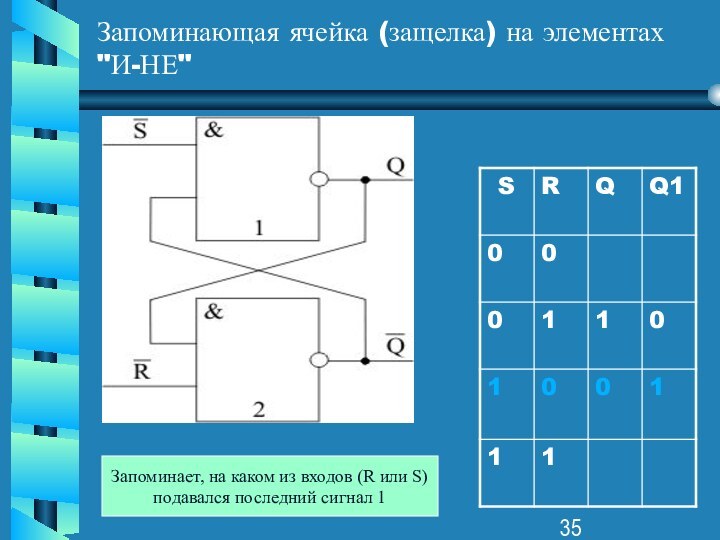

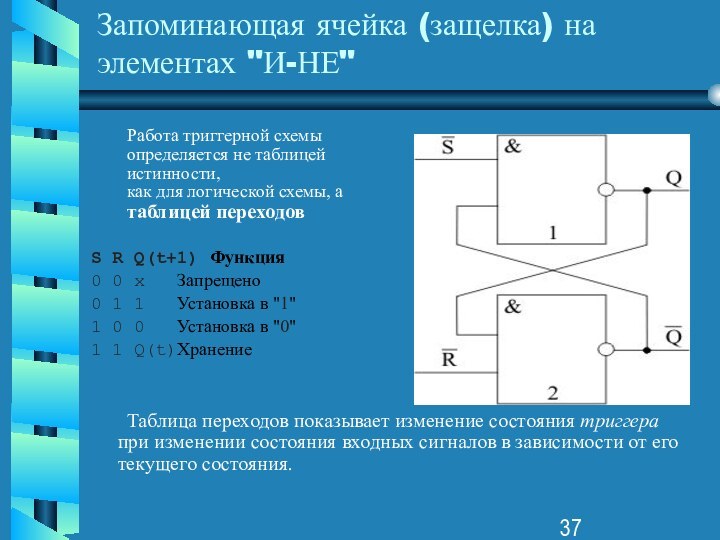

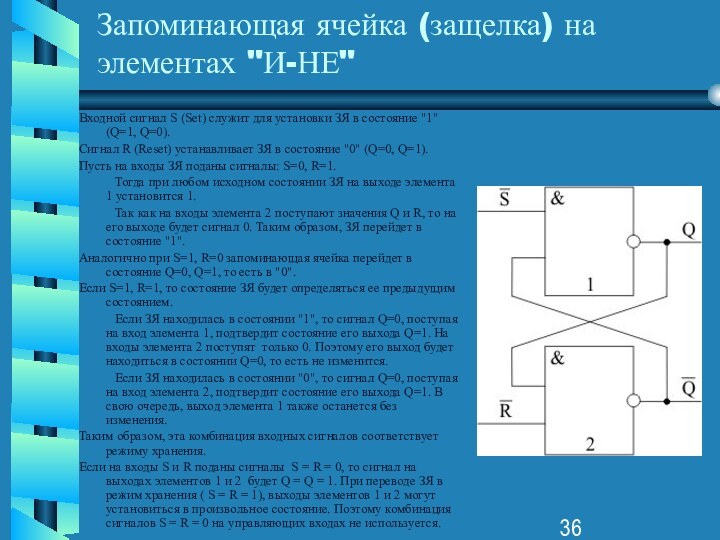

Запоминающая ячейка (защелка) на элементах "И-НЕ"

Запоминает, на каком

из входов (R или S)

подавался последний сигнал 1

Слайд 36

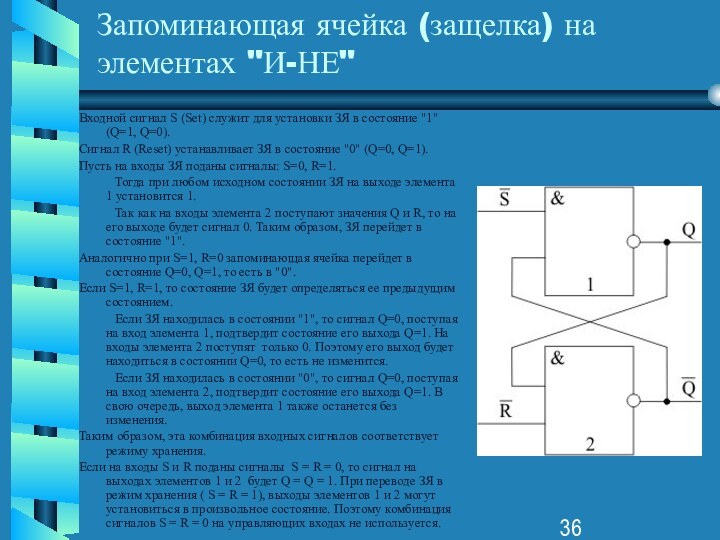

Запоминающая ячейка (защелка) на элементах "И-НЕ"

Входной сигнал S

(Set) служит для установки ЗЯ в состояние "1" (Q=1,

Q=0).

Сигнал R (Reset) устанавливает ЗЯ в состояние "0" (Q=0, Q=1).

Пусть на входы ЗЯ поданы сигналы: S=0, R=1.

Тогда при любом исходном состоянии ЗЯ на выходе элемента 1 установится 1.

Так как на входы элемента 2 поступают значения Q и R, то на его выходе будет сигнал 0. Таким образом, ЗЯ перейдет в состояние "1".

Аналогично при S=1, R=0 запоминающая ячейка перейдет в состояние Q=0, Q=1, то есть в "0".

Если S=1, R=1, то состояние ЗЯ будет определяться ее предыдущим состоянием.

Если ЗЯ находилась в состоянии "1", то сигнал Q=0, поступая на вход элемента 1, подтвердит состояние его выхода Q=1. На входы элемента 2 поступят только 0. Поэтому его выход будет находиться в состоянии Q=0, то есть не изменится.

Если ЗЯ находилась в состоянии "0", то сигнал Q=0, поступая на вход элемента 2, подтвердит состояние его выхода Q=1. В свою очередь, выход элемента 1 также останется без изменения.

Таким образом, эта комбинация входных сигналов соответствует режиму хранения.

Если на входы S и R поданы сигналы S = R = 0, то сигнал на выходах элементов 1 и 2 будет Q = Q = 1. При переводе ЗЯ в режим хранения ( S = R = 1), выходы элементов 1 и 2 могут установиться в произвольное состояние. Поэтому комбинация сигналов S = R = 0 на управляющих входах не используется.

Слайд 37

Запоминающая ячейка (защелка) на элементах "И-НЕ"

Работа триггерной схемы

определяется не таблицей

истинности,

как для логической схемы, а

таблицей переходов

S R Q(t+1) Функция

0 0 х Запрещено

0 1 1 Установка в "1"

1 0 0 Установка в "0"

1 1 Q(t)Хранение

Таблица переходов показывает изменение состояния триггера при изменении состояния входных сигналов в зависимости от его текущего состояния.