Слайд 2

Модуль центрального процессора С28x

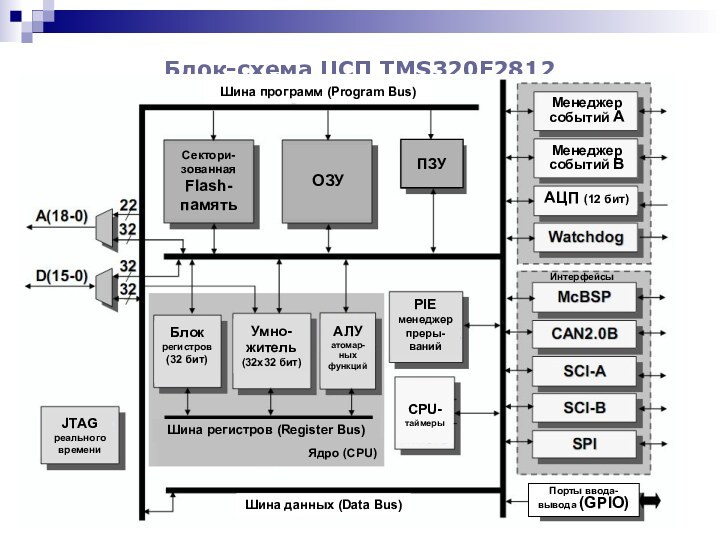

В целом укрупненная структура

ЦСП TMS320F2812 может быть представлена в виде 4-х блоков:

1.

Система внутренних и внешних шин

2. Модуль центрального процессора

3. Модуль памяти

4. Модуль периферийных устройств

Для обеспечения возможности работы в одном машинном цикле с двумя операндами, находящимися в памяти, ЦСП имеет гарвардскую архитектуру, т.е. оснащен двумя независимыми шинами: шиной программ (Program Bus) и шиной данных (Data Bus)

Слайд 3

Основные характеристики ЦСП семейства С28x

ЦСП TMS320F2812 имеет

высокопроизводительную статическую КМОП-технологию. Максимальная тактовая частота ядра составляет 150

MГц (время цикла 6,67 нс). Напряжение питания: на ядре –

1,8 В @ 135 МГц; 1,9 В @ 150 МГц; на периферийных модулях – 3,3 В.

ЦСП поддерживает периферийное сканирование по стандарту JTAG при высокой скорости передачи отладочной информации (до 20 Mбит/с).

TMS320F2812 содержит в своем составе периферийный модуль управления электроприводами – два модуля управления событиями (Event Manager - EVA, EVB), а также периферийные последовательные порты:

- синхронный последовательный интерфейс SPI;

- два асинхронных последовательных порта SCI, использующих стандарт UART;

- контроллер сети CAN (Controller Area Network) с расширенными возможностями;

- многоканальный буферизованный последовательный порт (Multichannel Buffered Serial Port - McBSP).

Количество встроенных портов для различных ЦСП семейства C28x, может быть различным. Некоторые ЦСП семейства C28x имеют в своем составе, помимо перечисленных, также и интерфейсы I2C, LIN (например, серии F2802x, F2803x).

Слайд 4

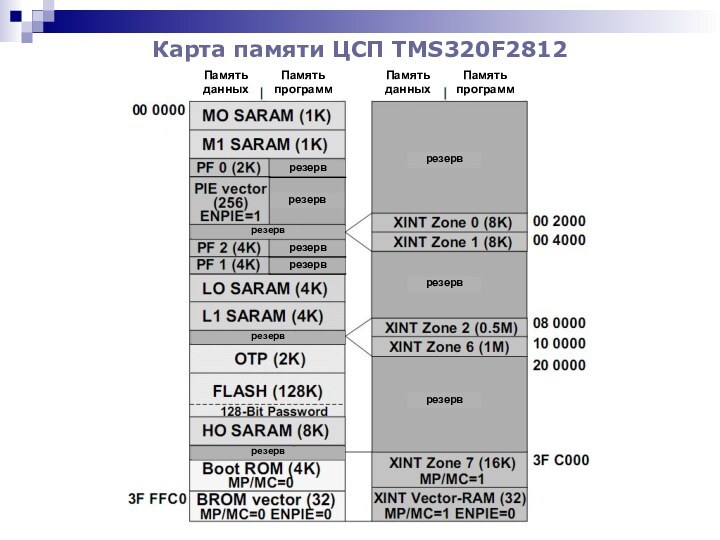

Карта памяти ЦСП TMS320F2812

Память данных

Память программ

Память данных

Память

программ

резерв

резерв

резерв

резерв

резерв

резерв

резерв

резерв

резерв

резерв

Слайд 5

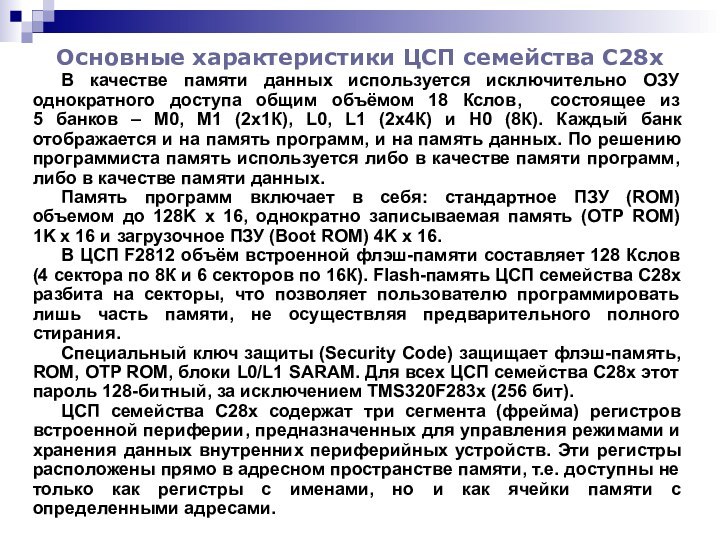

Основные характеристики ЦСП семейства С28x

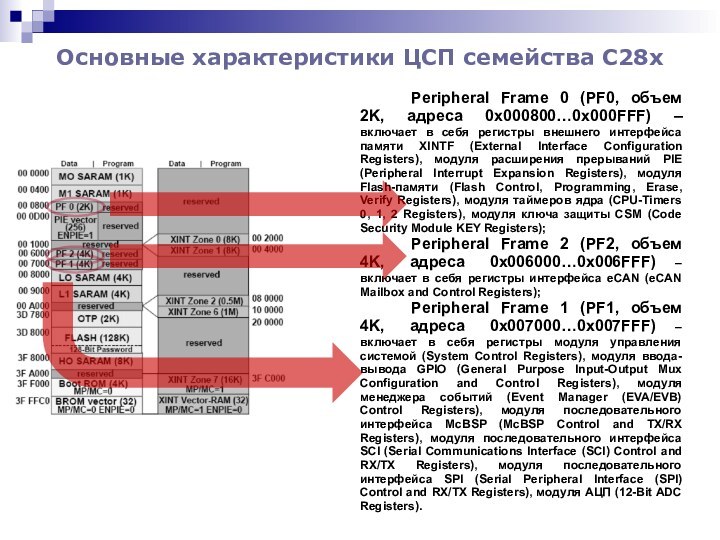

В качестве памяти

данных используется исключительно ОЗУ однократного доступа общим объёмом 18

Кслов, состоящее из

5 банков – М0, M1 (2x1К), L0, L1 (2x4К) и Н0 (8К). Каждый банк отображается и на память программ, и на память данных. По решению программиста память используется либо в качестве памяти программ, либо в качестве памяти данных.

Память программ включает в себя: стандартное ПЗУ (ROM) объемом до 128K x 16, однократно записываемая память (OTP ROM)

1K x 16 и загрузочное ПЗУ (Boot ROM) 4K x 16.

В ЦСП F2812 объём встроенной флэш-памяти составляет 128 Кслов (4 сектора по 8К и 6 секторов по 16К). Flash-память ЦСП семейства С28х разбита на секторы, что позволяет пользователю программировать лишь часть памяти, не осуществляя предварительного полного стирания.

Специальный ключ защиты (Security Code) защищает флэш-память, ROM, OTP ROM, блоки L0/L1 SARAM. Для всех ЦСП семейства С28x этот пароль 128-битный, за исключением TMS320F283x (256 бит).

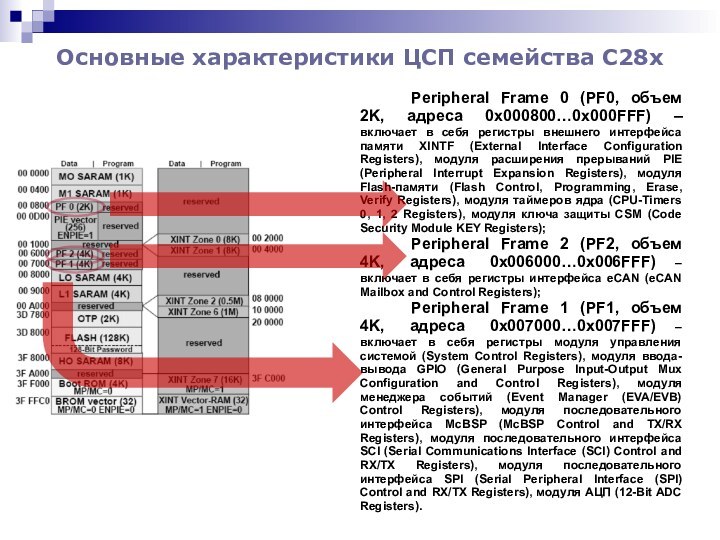

ЦСП семейства С28x содержат три сегмента (фрейма) регистров встроенной периферии, предназначенных для управления режимами и хранения данных внутренних периферийных устройств. Эти регистры расположены прямо в адресном пространстве памяти, т.е. доступны не только как регистры с именами, но и как ячейки памяти с определенными адресами.

Слайд 6

Основные характеристики ЦСП семейства С28x

Peripheral Frame 0

(PF0, объем 2K, адреса 0x000800…0x000FFF) – включает в себя

регистры внешнего интерфейса памяти XINTF (External Interface Configuration Registers), модуля расширения прерываний PIE (Peripheral Interrupt Expansion Registers), модуля Flash-памяти (Flash Control, Programming, Erase, Verify Registers), модуля таймеров ядра (CPU-Timers 0, 1, 2 Registers), модуля ключа защиты CSM (Code Security Module KEY Registers);

Peripheral Frame 2 (PF2, объем 4K, адреса 0x006000…0x006FFF) – включает в себя регистры интерфейса eCAN (eCAN Mailbox and Control Registers);

Peripheral Frame 1 (PF1, объем 4K, адреса 0x007000…0x007FFF) – включает в себя регистры модуля управления системой (System Control Registers), модуля ввода-вывода GPIO (General Purpose Input-Output Mux Configuration and Control Registers), модуля менеджера событий (Event Manager (EVA/EVB) Control Registers), модуля последовательного интерфейса McBSP (McBSP Control and TX/RX Registers), модуля последовательного интерфейса SCI (Serial Communications Interface (SCI) Control and RX/TX Registers), модуля последовательного интерфейса SPI (Serial Peripheral Interface (SPI) Control and RX/TX Registers), модуля АЦП (12-Bit ADC Registers).

Слайд 7

Основные характеристики ЦСП семейства С28x

Загрузочное ПЗУ (Boot

ROM) объёмом 4 Кслова программируется на заводе-изготовителе и содержит

несколько программ загрузки флэш-памяти, а также таблицы стандартных математических функций sin/cos(х), l/х, √х, arctg(х), используемые для организации эффективных вычислений.

В различных сериях ЦСП семейства C28x (F280x, F281x, F2823x, F2833x, C2834x, F2802x, F2803x) на кристалле имеется различный объем ПЗУ, ОЗУ, Flash-памяти.

Отличительной особенностью архитектуры C28 является отказ от аппаратного стека ограниченной ёмкости и переход к программному стеку любой длины. По умолчанию, в качестве стека предлагается использовать банк M1, и указатель стека сразу после сброса процессора устанавливается в начало этого блока.

Блок расширения периферийных прерываний PIE поддерживает 96 входов запросов прерываний, из которых используются только 45. Задержка при переходе к процедуре обслуживания прерывания составляет всего 9 циклов (60 нс). Дополнительной возможностью является аппаратный или программный контроль уровней приоритетов запросов прерываний, а также программное разрешение/запрет любого из запросов.

Слайд 8

Основные характеристики ЦСП семейства С28x

Интерфейс внешней памяти

XINTF (имеется только в ИМС TMS320F2812) состоит из 19-разрядной

адресной шины,

16-разрядной шины данных и трех линий выборки кристалла, с помощью которых обеспечивается доступ к пяти зонам внешней памяти 0, 1, 2, 6 и 7. Зоны 0 и 1 используют одну общую линию выборки, как и зоны 6 и 7.

19-битная шина адреса внешнего интерфейса позволяет адресовать 219=80000H=524288 ячеек памяти. Для сравнения,

22-битная внутренняя шина адреса программ адресует 222=400000H=4194304 ячеек памяти.

Доступ к памяти внутри каждой из пяти зон XINTF индивидуально программируется – устанавливается нужное число тактов ожидания и требуемые временные интервалы для сигналов чтения/записи. Эти возможности упрощают подключение внешней памяти и внешней периферии.

Внутренняя система шин включает в себя 2 составные шины:

1) шина чтения программ (22-разрядная адресная шина и

32-разрядная шина данных);

2) шина чтения и записи данных (32-разрядная адресная шина и 32-разрядная шина данных).

Слайд 9

Основные характеристики ЦСП семейства С28x

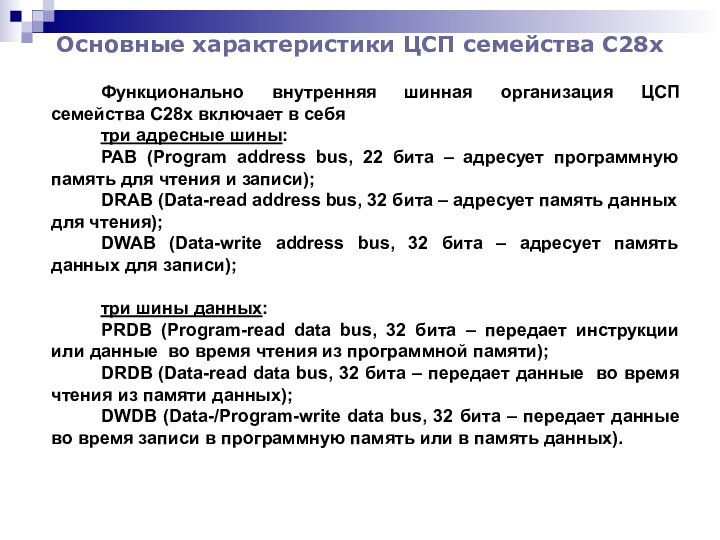

Функционально внутренняя шинная

организация ЦСП семейства С28x включает в себя

три адресные

шины:

PAB (Program address bus, 22 бита – адресует программную память для чтения и записи);

DRAB (Data-read address bus, 32 бита – адресует память данных для чтения);

DWAB (Data-write address bus, 32 бита – адресует память данных для записи);

три шины данных:

PRDB (Program-read data bus, 32 бита – передает инструкции или данные во время чтения из программной памяти);

DRDB (Data-read data bus, 32 бита – передает данные во время чтения из памяти данных);

DWDB (Data-/Program-write data bus, 32 бита – передает данные во время записи в программную память или в память данных).

Слайд 10

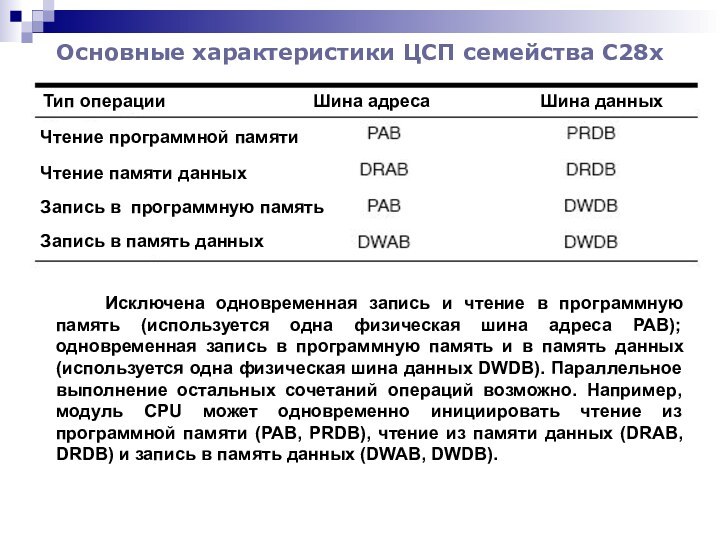

Основные характеристики ЦСП семейства С28x

Исключена одновременная запись

и чтение в программную память (используется одна физическая шина

адреса PAB); одновременная запись в программную память и в память данных (используется одна физическая шина данных DWDB). Параллельное выполнение остальных сочетаний операций возможно. Например, модуль CPU может одновременно инициировать чтение из программной памяти (PAB, PRDB), чтение из памяти данных (DRAB, DRDB) и запись в память данных (DWAB, DWDB).

Чтение программной памяти

Запись в программную память

Чтение памяти данных

Запись в память данных

Тип операции

Шина адреса

Шина данных

Слайд 11

Основные характеристики ЦСП семейства С28x

Указанная система внутренних

шин названа разработчиками Texas Instruments «модифицированная гарвардская архитектура». Главное

ее достоинство – параллельное выполнение сразу нескольких действий. В течение одного цикла возможна выборка команды, считывание и запись данных. Кроме того, в течение одного цикла в АЛУ можно вводить два 32-битных операнда (по одному из памяти данных и из памяти программ) для последующего умножения.

Для сравнения, при вводе через внешний интерфейс минимально необходимо 4 цикла, т.к. внешняя ША имеет 19 бит, а внешняя ШД – 16 бит.

Слайд 12

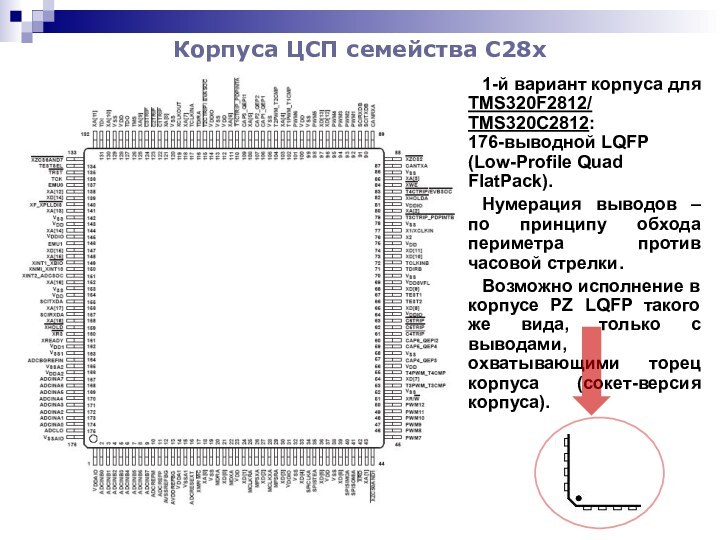

Корпуса ЦСП семейства С28x

1-й вариант корпуса для

TMS320F2812/ TMS320С2812:

176-выводной LQFP (Low-Profile Quad FlatPack).

Нумерация выводов –

по принципу обхода периметра против часовой стрелки.

Возможно исполнение в корпусе PZ LQFP такого же вида, только с выводами, охватывающими торец корпуса (сокет-версия корпуса).

Слайд 13

Корпуса ЦСП семейства С28x

2-й вариант корпуса для

TMS320F2812/ TMS320С2812 :

179-выводной MicroStar BGA (Ball Grid Array)

– вид снизу.

Нумерация выводов – по координатному принципу «строка-столбец»:

по вертикали снизу вверх латинскими буквами от «A» до «P»;

по горизонтали слева направо цифрами от «1» до «14».

Примеры:

«L12» - вывод PWM3;

«D4» - вывод ADCINA4.

Слайд 14

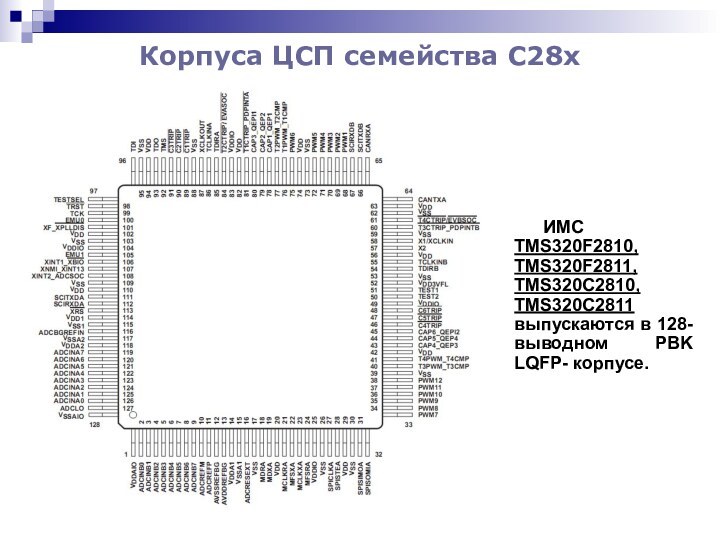

Корпуса ЦСП семейства С28x

ИМС TMS320F2810, TMS320F2811, TMS320С2810,

TMS320С2811 выпускаются в 128-выводном PBK LQFP- корпусе.

Слайд 15

Корпуса ЦСП семейства С28x

ИМС

TMS320F2801, TMS320С2801, TMS320F2802,

TMS320С2802, TMS320F2806, TMS320F2808

выпускаются в 100-выводном

корпусе PZ LQFP

или в 100-выводном

корпусе GGM BGA.

Слайд 16

Корпуса ЦСП семейства С28x (серия Delfino)

Корпуса для

серий

Delfino C2833x и C2834x:

176-выводной LQFP,

179-выводной MicroStar

BGA, 176-выводной BGA (аналогичен вышерассмотренному 179-выводному MicroStar BGA).

Кроме того, Delfino C2834x выпускается в 256-выводном корпусе BGA.

Этот корпус аналогичен вышерассмотренному 179-выводному MicroStar BGA, только координатное поле имеет формат 16 x 16.

. . .

.

.

.

Слайд 17

Корпуса ЦСП семейства С28x (серия Piccolo)

Серия Piccolo

C2802x:

38- выводной корпус TSSOP, шаг выводов 0.65mm

Серия Piccolo

C2803x:

48- выводной корпус LQFP или 64-выводной TQFP, шаг выводов 0.5mm