Слайд 2

Цифровые ИМС и логические элементы

Цифровые интегральные микросхемы (ИМС)

–

это микроэлектронные изделия, предназначенные

для преобразования и обработки

цифровых сигналов.

Логическим элементом называется устройство, выполняющее элементарные логические операции И, ИЛИ, НЕ, И-НЕ, ИЛИ-НЕ, относящиеся к функциональным элементам одноступенчатой логики и элементы двухступенчатой логики: И-ИЛИ-НЕ, И-ИЛИ, ИЛИ-И и др.

Системой логических элементов называется функционально полный набор логических элементов, объединенных общими электрическими, конструктивными и технологическими пара-метрами и использующих одинаковый тип межэлементных связей.

Системы элементов содержат элементы для выполнения логических операций, запоминающие элементы, элементы, реализующие функции узлов ЭВМ, а также элементы

для усиления, восстановления и формирования сигналов стандартной формы.

Слайд 3

Схемотехнические базисы

Схемотехнические базисы (схемотехнологии) цифровых микросхем развивались в

следующей последовательности:

резистивно-транзисторная логика (РТЛ),

резистивно-конденсаторная логика (РКТЛ),

диодно-транзисторная логика (ДТЛ),

транзисторно-транзисторная логика

(ТТЛ),

эмиттерно-связанная логика (ЭСЛ),

транзисторно-транзисторная логика с диодами Шоттки (ТТЛШ),

интегрально-инжекционная логика (И2Л).

В этих определениях слово «логика» подразумевает понятие «электронный ключ».

Все перечисленные цифровые микросхемы выполнены на базе биполярных транзисторов. Наряду с ними широкое распространение получили цифровые микросхемы на МОП-структурах (на транзисторах p- и n-типов с обогащённым каналом, КМОП – схемы на дополняющих транзисторах).

Слайд 4

Положительная и отрицательная логика работы ИМС

Цифровые микросхемы могут

использовать позитивную или негативную логику.

Логика называется позитивной (положительной), если

высокому уровню потенциала U1 приписывается значение логической единицы, а низкому уровню потенциала U0 – логический нуль.

Логика называется негативной (отрицательной), если высокому уровню потенциала U1 приписывается значение логического нуля, а низкому уровню потенциала U0 – значение логической единицы.

Слайд 5

Статические параметры логических элементов

Основные параметры логических элементов:

напряжение источника

питания;

входной ток;

уровни выходных напряжений;

потребляемая мощность (Рпот);

помехоустойчивость;

коэффициент разветвления по выходу

Краз (нагрузочная способность);

коэффициент объединения по входу Коб.

Слайд 6

Входной ток

Входной ток Iвх определяет нагрузку, которую представляет

рассматриваемая схема для предшествующей ей схемы или другого источника

сигнала. Наиболее полно этот параметр определяет зависимость Iвх(Uвх) от напряжения входного сигнала, т.е. ВАХ.

В зависимости от вида полупроводниковых приборов,

на которых построена входная логика (диоды или транзисторы, их тип и т. д.), а также от значения входного сигнала (1 или 0 при положительной или отрицательной логике) схемы могут как потреблять ток от источника входного сигнала, так и отдавать его. Поэтому различают входные токи I0вх и I1вх при подаче логического «0» или логической «1».

Наименьшие входные токи имеют ИМС на МОП-транзисторах (до долей микроампер), наибольшие – быстродействующие ИМС

на биполярных транзисторах (до единиц миллиампер).

Слайд 7

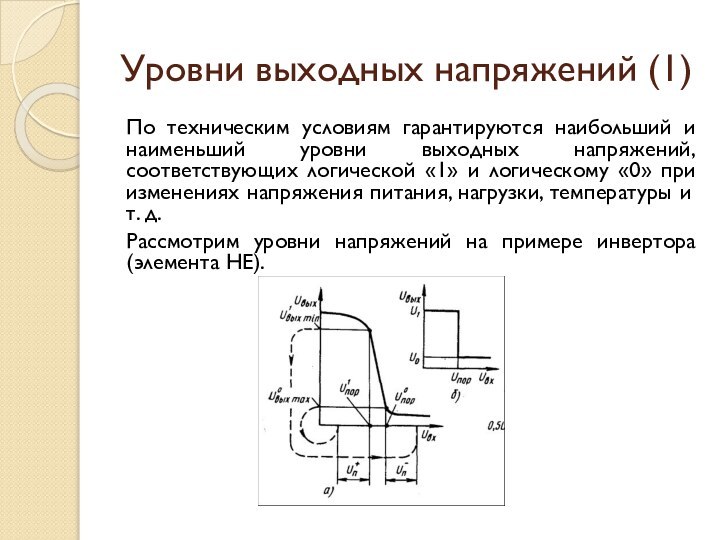

Уровни выходных напряжений (1)

По техническим условиям гарантируются наибольший

и наименьший уровни выходных напряжений, соответствующих логической «1» и

логическому «0» при изменениях напряжения питания, нагрузки, температуры и т. д.

Рассмотрим уровни напряжений на примере инвертора (элемента НЕ).

Слайд 8

Уровни выходных напряжений (2)

Напряжение U1вых min соответствует минимальному

уровню логической «1» на выходе, а напряжение U0вых max

– максимальному уровню логического «0». Для современных ИМС эти параметры имеют значения от долей до единиц вольт.

Абсцисса точки пересечения передаточной характеристики с уровнем U1вых min называется входным пороговым напряжением логической «1» и обозначается U1пор, а абсцисса точки пересечения с уровнем U0вых max – входным пороговым напряжением логического «0» U0пор.

При напряжении входного сигнала Uвх < U1пор на выходе элемента поддерживается уровень логической «1» , при Uвх > U0пор – уровень логического «0».

Диапазон напряжений на входе U1пор < Uвх < U0пор и диапазон напряжений на выходе U0вых max < Uвх < U1вых min соответствует области переключения, в которой схема находится только во время действия фронтов входных сигналов.

Слайд 9

Потребляемая мощность (1)

В зависимости от технологии микросхем, мощности,

потребляемые в состоянии логического «0» и в состоянии логической

«1», могут отличаться.

Некоторые логические элементы большую мощность потребляют в статических состояниях («0», «1») и сравнительно незначитель-ную – во время переходного процесса из состояния «0» в состояние «1» и наоборот.

Другие многочисленные и широко применяемые логические элементы характеризуются большой потребляемой мощностью во времени переходных процессов и относительно невысокой

в статических состояниях.

По потребляемой мощности ИМС можно разделить

на относительно мощные (потребляемая мощность от сотен

до единиц милливатт), маломощные (от единиц милливатт

до микроватта) и ещё меньшей мощности, называемые «нановаттными» (потребляемая мощность <1 мкВт).

Слайд 10

Потребляемая мощность (2)

Средняя потребляемая мощность

в динамическом режиме

для ИМС

на биполярных транзисторах (в предположении, что схема

примерно одинаковое время находится в состояниях «0» и «1»), определяется как

Рпотр = 0,5(Р0потр + Р1потр),

где Р0потр – мощность, потребляемая микросхемой при состоянии выхода «0»;

Р1потр – мощность при выходном состоянии «1».

Так как эта мощность отводится (рассеивается) в виде теплоты, её называют также рассеиваемой мощностью.

Слайд 11

Помехоустойчивость

ИМС, принадлежащие одной серии, спроектированы взаимно согласованными, т.

е. уровни выходных сигналов одного логического элемента (даже при

их изменении

в допустимых пределах) могут использоваться в качестве уровней входного сигнала следующего элемента

без каких-либо согласующих устройств.

Допустимый уровень напряжения помехи логического элемента определяется уровнем входного напряжения, при котором ещё не происходит ложное срабатывание микросхемы.

В статическом режиме помехоустойчивость определяется по низкому U0пом и высокому U1пом уровням.

Помехоустойчивость в динамическом режиме зависит

от длительности, амплитуды и формы импульса помехи,

а также от запаса статической помехоустойчивости

и скорости переключения логического элемента.

Слайд 12

Статическая помехоустойчивость (1)

Параметры статической помехоустойчивости проиллюстрированы на рисунке

построением, выполненным штриховыми линиями.

Слайд 13

Статическая помехоустойчивость (2)

Из построения видно, что между U0вых

max, поданным на вход следующего элемента, и U1пор имеется

запас Uп+. Этот запас означает, что переключения этого элемента из 1 в 0

не произойдет даже в том случае, если входной сигнал, соответствующий логическому «0», превысит по какой-либо причине значение U0вых max, но на величину, не большую, чем Uп+. Значение Uп+ и характеризует помехоустойчивость ИМС

к положительным изменениям напряжения.

Аналогично, если на вход следующего элемента подано с выхода предыдущего напряжение логической 1, даже меньшее, чем

U1вых min, но на величину, не превышающую Uп–, то переключения из 0 в 1 этого элемента не произойдет, так как Uвх окажется всё-таки большим порогового Uп–. Параметр Uп– характеризует помехоустойчивость ИМС к отрицательным изменениям напряжения. Этот параметр для различных типов микросхем колеблется от десятых долей до единиц вольт.

Слайд 14

Коэффициент разветвления по выходу,

коэффициент объединения по входу

Коэффициент

разветвления по выходу Краз определяет число входов аналогичных элементов,

которое может быть подключено к выходу предыдущего элемента без нарушения его работоспособности. С увеличением нагрузочной способности расширяются возможности применения цифровых микросхем и уменьшается число корпусов

в разрабатываемом устройстве. Однако при этом ухудшаются помехоустойчивость и быстродействие микросхемы и возрастает потребляемая мощность.

Коэффициент объединения по входу Коб определяет максимальное число входов цифровых микросхем.

Слайд 15

Динамические параметры логических элементов (1)

К основным динамическим параметрам

логического элемента относятся:

t01 – время перехода при включении (фронт

формирования уровня логической «1»);

t10 – время перехода при выключении (фронт формирования уровня логического «0»);

t10зд – время задержки распространения при включении (переключении из состояния логической «1» в состояние логического «0»);

t01зд – время задержки распространения при выключении (переключении из состояния логического «0» в состояние логической «1»);

tзд ср – среднее время задержки распространения (интервал времени, равный полусумме времён задержки распространения сигнала при включении и при выключении; в дальнейшем это время будем называть временем задержки элемента tзд).

tи—длительность импульса;

fp—рабочая частота.

Слайд 16

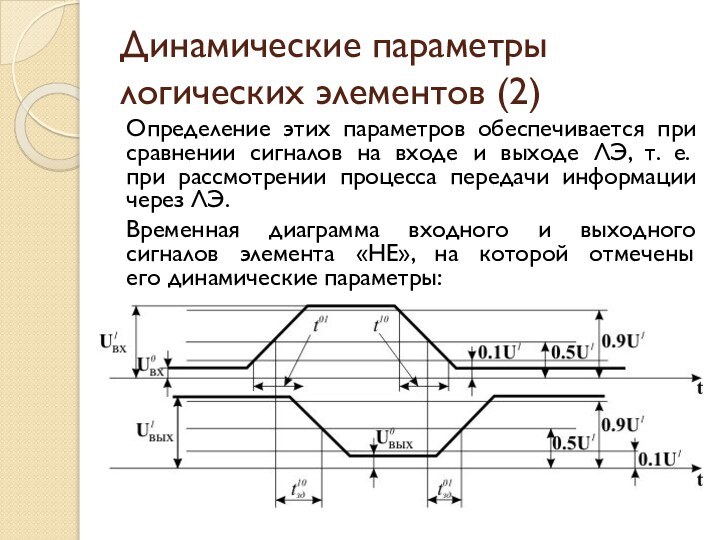

Динамические параметры логических элементов (2)

Определение этих параметров обеспечивается

при сравнении сигналов на входе и выходе ЛЭ, т.

е.

при рассмотрении процесса передачи информации через ЛЭ.

Временная диаграмма входного и выходного сигналов элемента «НЕ», на которой отмечены

его динамические параметры:

Слайд 17

Эксплуатационные параметры

Кроме рассмотренных параметров, характеризующих электрический режим работы

ИМС, используют

и эксплуатационные параметры, характеризующие работоспособность ИМС в

условиях воздействия окружающей среды.

К числу таких параметров относятся следующие:

диапазон рабочих температур;

допустимые механические воздействия (частота

и амплитуда вибраций, ударные нагрузки, ускорения);

границы допустимого диапазона изменения атмосферного давления, влажности и т. д.

Слайд 18

Серии логических ИМС

В зависимости от технологии изготовления логические

ИМС делятся на серии, отличающиеся набором элементов, напряжением питания,

потребляемой мощностью, динамическим параметрам и др.

Наибольшее применение получили серии логических ИМС, выполненные по технологиям ТТЛ (транзисторно-транзисторная логика), ЭСЛ (эмиттерно-связанная логика) и КМОП (комплиментарная МОП логика).

Каждая из перечисленных технологий совершенствовалась, поэтому в каждой серии ИМС имеются подсерии, отличающиеся по параметрам.

Слайд 19

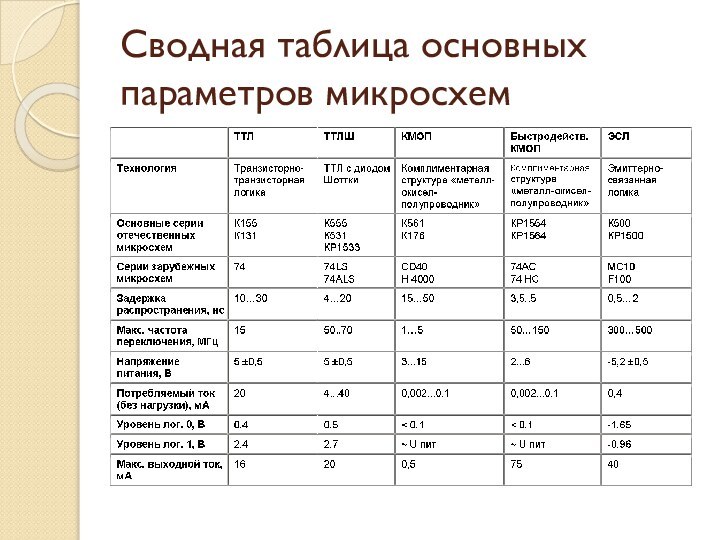

Сводная таблица основных параметров микросхем

Слайд 20

Микросхемы ТТЛ (1)

В ИМС, выполненных по технологии ТТЛ,

в качестве базового элемента используется многоэмиттерный транзистор. Многоэмиттерный транзистор

(МЭТ) имеет несколько эмиттеров, расположенных так, что прямое взаимодействие между ними исключается. Благодаря этому переходы база-эмиттеры МЭТ можно рассматривать как параллельно включённые диоды.

В ИМС, выполненных по технологии ТТЛШ, используется сложный инвертор с двуполярным ключом,

а для исключения насыщения МЭТ – диоды Шотки с малым падением напряжения в прямом направлении (ТТЛШ).

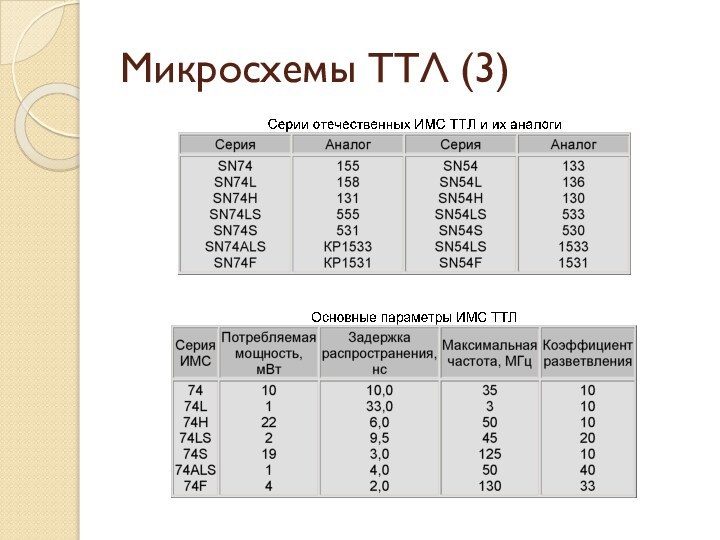

Первым разработчиком ИМС по технологии ТТЛ является фирма Техаs Instruments, которая выпустила ИМС серии SN74. Дальнейшие усовершенствования этой серии были направлены на повышение быстродействия и снижение потребляемой мощности.

Слайд 21

Микросхемы ТТЛ (2)

Подвиды микросхем ТТЛ:

L (low power) –

маломощная серия

H (high speed) – быстродействующая серия

LS

(low power Shottky) – маломощная серия c диодами Шотки

S (Shottky) – серия c диодами Шотки

ALS (advanced low power Shottky) – усовершенствованная маломощная серия c диодами Шотки

F (fast) – сверхбыстродействующая серия.

Слайд 23

Типы выходных каскадов цифровых элементов

Цифровые элементы (логические, запоминающие,

буферные) могут иметь выходы следующих типов:

логические;

с третьим состоянием;

с открытым

коллектором (стоком);

с открытым эмиттером (истоком).

Слайд 24

Логический выход (1)

Логический выход формирует два уровня выходного

напряжения (U0 и U1).

Выходное сопротивление логического выхода стремятся сделать

малым, способным развивать большие токи для перезаряда ёмкостных нагрузок и, следовательно, получения высокого быстродействия элемента.

Такой тип выхода имеют большинство логических элементов, используемых в комбинационных цепях.

Схемы логических выходов элементов ТТЛ(Ш) и КМОП подобны двухтактным каскадам – в них оба фронта выходного напряжения формируются с участием активных транзисторов, работающих противофазно, что обеспечивает малые выходные сопротивления при любом направлении переключения выхода.

Слайд 25

Логический выход (2)

Особенность таких выходов состоит в том,

что их нельзя соединять параллельно.

Во-первых, это создает логическую неопределённость,

т. к. в точке соединения выхода, формирующего логическую единицу, и выхода, формирующего логический нуль, не будет нормального результата.

Во-вторых, при соединении выходов, находящихся

в различных логических состояниях, возникло бы их «противоборство». Вследствие малых величин выходных сопротивлений уравнительный ток при этом может достигать достаточно большой величины,

что может вывести из строя электрические элементы выходной цепи.

Слайд 26

Логический выход (3)

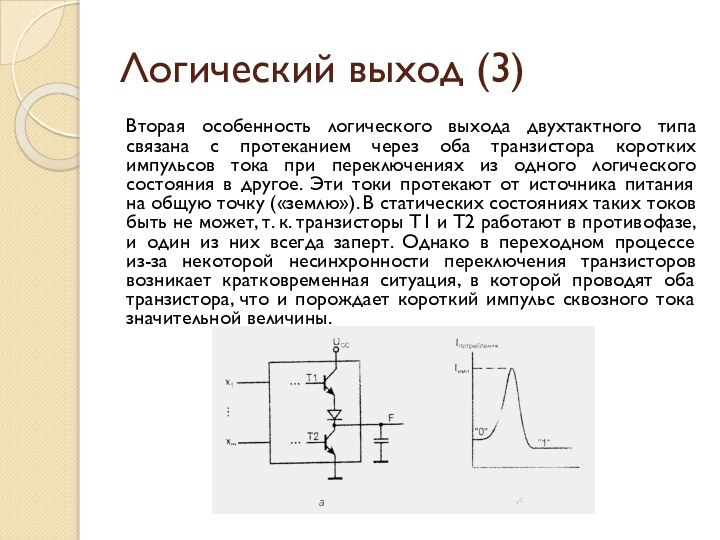

Вторая особенность логического выхода двухтактного типа

связана с протеканием через оба транзистора коротких импульсов тока

при переключениях из одного логического состояния в другое. Эти токи протекают от источника питания

на общую точку («землю»). В статических состояниях таких токов быть не может, т. к. транзисторы Т1 и Т2 работают в противофазе, и один из них всегда заперт. Однако в переходном процессе

из-за некоторой несинхронности переключения транзисторов возникает кратковременная ситуация, в которой проводят оба транзистора, что и порождает короткий импульс сквозного тока значительной величины.

Слайд 27

Элементы с тремя состояниями выхода (1)

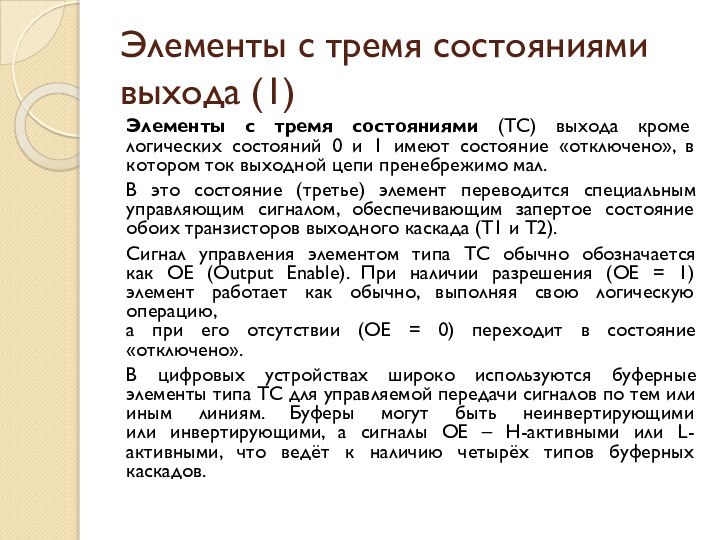

Элементы с тремя

состояниями (ТС) выхода кроме логических состояний 0 и 1

имеют состояние «отключено», в котором ток выходной цепи пренебрежимо мал.

В это состояние (третье) элемент переводится специальным управляющим сигналом, обеспечивающим запертое состояние обоих транзисторов выходного каскада (Т1 и Т2).

Сигнал управления элементом типа ТС обычно обозначается

как ОЕ (Output Enable). При наличии разрешения (ОЕ = 1) элемент работает как обычно, выполняя свою логическую операцию,

а при его отсутствии (ОЕ = 0) переходит в состояние «отключено».

В цифровых устройствах широко используются буферные элементы типа ТС для управляемой передачи сигналов по тем или иным линиям. Буферы могут быть неинвертирующими

или инвертирующими, а сигналы ОЕ – Н-активными или L-активными, что ведёт к наличию четырёх типов буферных каскадов.

Слайд 28

Элементы с тремя состояниями выхода (2)

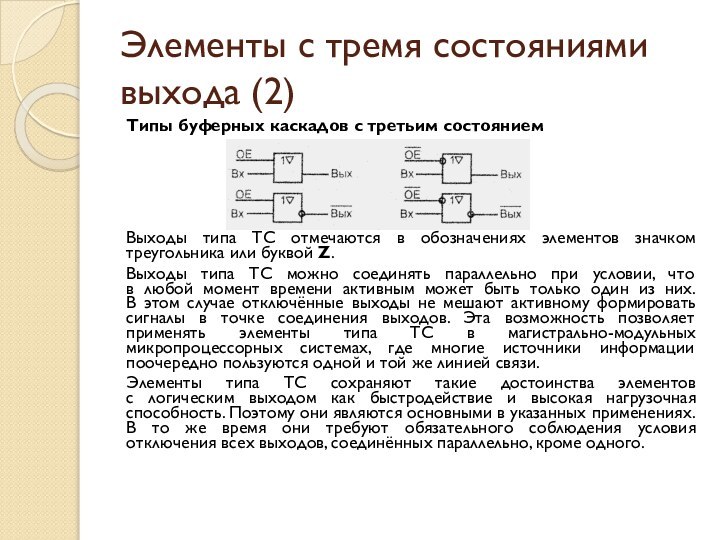

Типы буферных каскадов

с третьим состоянием

Выходы типа ТС отмечаются в обозначениях элементов

значком треугольника или буквой Z.

Выходы типа ТС можно соединять параллельно при условии, что

в любой момент времени активным может быть только один из них.

В этом случае отключённые выходы не мешают активному формировать сигналы в точке соединения выходов. Эта возможность позволяет применять элементы типа ТС в магистрально-модульных микропроцессорных системах, где многие источники информации поочередно пользуются одной и той же линией связи.

Элементы типа ТС сохраняют такие достоинства элементов

с логическим выходом как быстродействие и высокая нагрузочная способность. Поэтому они являются основными в указанных применениях. В то же время они требуют обязательного соблюдения условия отключения всех выходов, соединённых параллельно, кроме одного.

Слайд 29

Выход с открытым коллектором (1)

Элементы с открытым коллектором

(ОК) имеют выходную цепь, заканчивающуюся одиночным транзистором, коллектор которого

не соединен с какими-либо цепями внутри микросхемы.

Транзистор управляется от предыдущей части схемы элемента так, что может находиться в насыщенном или запертом состоянии. Насыщенное состояние трактуется как отображение логического нуля, запертое – единицы. Насыщение транзистора обеспечивает на выходе напряжение U0 – малое напряжение насыщения «коллектор-эмиттер». Запирание же транзистора какого-либо уровня напряжения на выходе элемента не задает, выход при этом имеет фактически неизвестный «плавающий» потенциал, т. к. не подключен к каким-либо цепям схемы элемента. Поэтому для формирования высокого уровня напряжения при запирании транзистора на выходе элементов

с открытым коллектором (типа ОК) требуется подключать внешние резисторы (или другие нагрузки), соединенные

с источником питания.

Слайд 30

Выход с открытым коллектором (2)

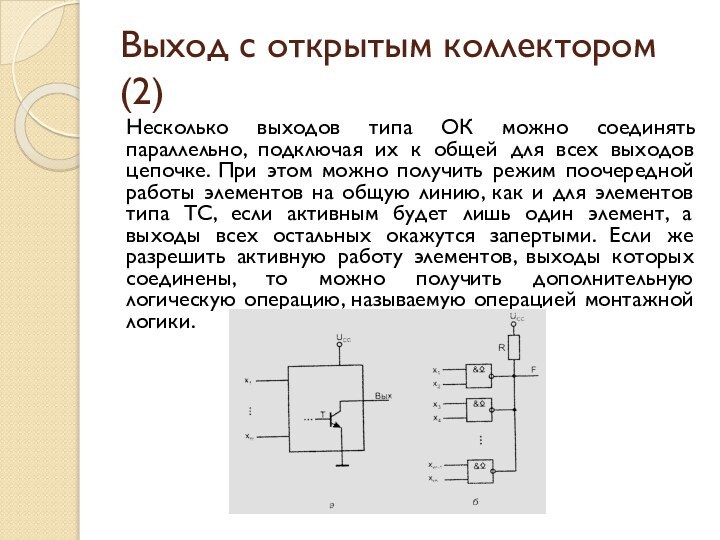

Несколько выходов типа ОК

можно соединять параллельно, подключая их к общей для всех

выходов цепочке. При этом можно получить режим поочередной работы элементов на общую линию, как и для элементов типа ТС, если активным будет лишь один элемент, а выходы всех остальных окажутся запертыми. Если же разрешить активную работу элементов, выходы которых соединены, то можно получить дополнительную логическую операцию, называемую операцией монтажной логики.

Слайд 31

Выход с открытым коллектором (3)

При реализации монтажной логики

высокое напряжение

на общем выходе возникает только при запирании

всех транзисторов, т. к. насыщение хотя бы одного из них снижает выходное напряжение до уровня U0 = Uкэн. То есть для получения логической единицы на выходе требуется единичное состояние всех выходов: выполняется монтажная операция И.

В обозначениях элементов с ОК после символа функции ставится ромб с черточкой снизу.

При использовании элементов с ОК в магистрально-модульных структурах требуется разрешать или запрещать работу того

или иного элемента. Для элементов типа ТС это делалось

с помощью специального сигнала ОЕ. Для элементов типа ОК

в качестве входа ОЕ может быть использован один из обычных входов элемента. Если речь идет об элементе И-НЕ, то, подавая

0 на любой из входов, можно запретить работу элемента, поставив его выход в разомкнутое состояние независимо

от состояния других входов. Уровень 1 на этом входе разрешит работу элемента.

Слайд 32

Выход с открытым коллектором (4)

Положительной чертой элементов с

ОК при работе

в магистрально-модульных системах является их защищенность

от повреждений из-за ошибок управления, приводящих

к одновременной выдаче на шину нескольких слов, а также возможность реализации дополнительных операций монтажной логики.

Недостатком таких элементов является большая задержка переключения из 0 в 1. При этом переключении происходит заряд выходной ёмкости сравнительно малым током резистора R. Сопротивление резистора нельзя сделать слишком малым,

т. к. это привело бы к большим токам выходной цепи в статике при насыщенном состоянии выходного транзистора. Поэтому положительный фронт выходного напряжения формируется относительно медленно с постоянной времени RC.

До порогового напряжения (до середины полного перепада напряжения) экспоненциально изменяющийся сигнал изменится за время 0.7RC.

Слайд 33

Выход с открытым коллектором (5)

При работе с элементами

типа ОК проектировщик должен задать сопротивление резистора R, которое

не является стандартным, а определяется для конкретных условий. Анализ статических режимов задает ограничения величины сопротивления R снизу и сверху. Значение сопротивления резистора R выбирается в этом диапазоне

с учётом быстродействия схемы и потребляемой ею мощности.

Ограничение снизу величины сопротивления резистора R связано с тем, что её уменьшение может вызвать перегрузку насыщенного транзистора по току.

Ограничение сверху величины сопротивления резистора R связано с необходимостью обеспечения достаточно высокого уровня напряжения U1, формируемого в схеме при запертом состоянии всех выводов элементов с ОК.

Слайд 34

Выход с открытым эмиттером

Выход с открытым эмиттером характерен

для элементов типа ЭСЛ. Для работы на магистраль такие

элементы

не используются. Возможность соединять друг с другом выходы с открытым эмиттером при объединении эмиттерных резисторов в один общий резистор приводит к схеме, называемой «эмиттерный дот» и используемой

при построении логических схем

для получения дополнительной операции монтажной логики.