Слайд 2

Учебные вопросы:

Назначение и структура центрального процессора (ЦП), состав

устройств.

Центральное устройство управления (УУ).

Арифметико-логическое устройство (АЛУ): назначение, основные характеристики,

обобщенная структурная схема.

Взаимодействие блоков АЛУ при выполнении различных арифметических и логических операций.

Архитектура и микроархитектура процессора.

RISC- и CISC-процессоры, их использование в ПЭВМ будущих поколений.

Структура базового микропроцессора (МП) современных моделей для IMB-совместимых ПЭВМ, взаимодействие его узлов и блоков.

Параметры микропроцессоров.

Понятия: кэш-память, конвейеризация, разрядность, технология производства

Слайд 3

Назначение и структура центрального процессора (ЦП), состав устройств

Процессором

называется устройство, непосредственно осуществляющее процесс обработки данных и программное

управление этим процессом. Процессор дешифрирует и выполняет команды программы, организует обращения к оперативной памяти, в нужных случаях инициирует работу периферийных устройств, воспринимает и обрабатывает запросы, поступающие из устройств машины и из внешней среды (“запросы прерывания”).

Процессор занимает центральное место в структуре ЭВМ, так как он осуществляет управление взаимодействием всех устройств, входящих в состав ЭВМ.

Слайд 4

Центральное устройство управления (УУ)

Устройство управления организует процесс выполнения

программ и координирует взаимодействие всех устройств ЭВМ во время

её работы.

Центральное устройство управления организует и координирует автоматическое взаимодействие всех устройств ЭВМ в процессе решения задачи.

Основной задачей Центрального устройства управления является выборка из памяти кодов команд программ и их преобразование в необходимые последовательности синхронизирующих, разрешающих, устанавливающих, стробирующих и других сигналов

Слайд 5

Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная структурная

схема

Арифметико-логическое устройство процессора выполняет логические и арифметические операции над

данными. В общем случае в АЛУ выполняются логические преобразования над логическими кодами фиксированной и переменной длины (над отдельными битами, группами бит, байтами и их последовательностями) , арифметические операции над числами с фиксированной и плавающей точками, над десятичными числами, обработка алфавитно-цифровых слов переменной длины и др. Характер выполняемой АЛУ операции задается командой программы.

В процессоре может быть одно универсальное АЛУ для выполнения всех основных арифметических и логических преобразований или несколько специализированных для отдельных видов операций. В последнем случае увеличивается количество оборудования процессора, но повышается его быстродействие за счет специализации и упрощения схем выполнения отдельных операций.

Слайд 6

Арифметико-логическое устройство (АЛУ): назначение

Арифметико-логическое устройство (АЛУ) - центральная

часть процессора, выполняющая арифметические и логические операции.

АЛУ реализует

важную часть процесса обработки данных. Она заключается в выполнении набора простых операций. Операции АЛУ подразделяются на три основные категории: арифметические, логические и операции над битами. Арифметической операцией называют процедуру обработки данных, аргументы и результат которой являются числами (сложение, вычитание, умножение, деление,...). Логической операцией именуют процедуру, осуществляющую построение сложного высказывания (операции И, ИЛИ, НЕ,...). Операции над битами обычно подразумевают сдвиги.

Слайд 7

Арифметико-логическое устройство (АЛУ): основные характеристики

АЛУ состоит из регистров,

сумматора с соответствующими логическими схемами и элемента управления выполняемым

процессом. Устройство работает в соответствии с сообщаемыми ему именами (кодами) операций, которые при пересылке данных нужно выполнить над переменными, помещаемыми в регистры.

Арифметико-логическое устройство функционально можно разделить на две части :

а) микропрограммное устройство (устройство управления), задающее последовательность микрокоманд (команд);

б) операционное устройство (АЛУ), в котором реализуется заданная последовательность микрокоманд (команд).

Слайд 8

Арифметико-логическое устройство (АЛУ): обобщенная структурная схема

Слайд 9

Структурная схема АЛУ

Структурная схема АЛУ и его связь

с другими блоками машины показаны на рисунке (предыдущий слайд).

В состав АЛУ входят регистры Рг1 - Рг7, в которых обрабатывается информация , поступающая из оперативной или пассивной памяти N1, N2, ...NS; логические схемы, реализующие обработку слов по микрокомандам, поступающим из устройства управления.

Слайд 10

Взаимодействие блоков АЛУ при выполнении различных арифметических и

логических операций

Обобщенная структура АЛУ

ИПУ – Инженерный Пульт Управления

МП

– Местная Память

УР – Управляющие Регистры

БКД – Блок Контроля и Диагностики

БССОП – Блок Связи С Основной Памятью

БЗП – Блок Защиты Памяти

Слайд 11

Центральное Устройство Управления

ЦУУ формирует управляющие сигналы для

следующих функций:

- выборки из ОЗУ (ПЗУ) кодов очередной команды

-

расшифровки кодов операций и признака выбранной операции

- формирование исоплнительного адреса операнда

- анализ запросов на прерывание исполняемой программы

- формирование адреса следующей команды

Слайд 12

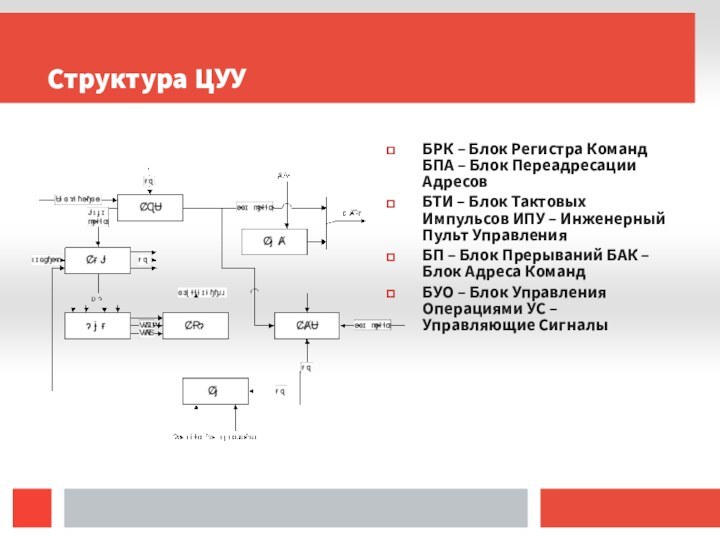

Структура ЦУУ

БРК – Блок Регистра Команд БПА

– Блок Переадресации Адресов

БТИ – Блок Тактовых Импульсов ИПУ

– Инженерный Пульт Управления

БП – Блок Прерываний БАК – Блок Адреса Команд

БУО – Блок Управления Операциями УС – Управляющие Сигналы

Слайд 13

ЦУУ

Алгоритм:

1)код очередной команды программы принимается для расшифровки

и исполнения в БРК, под воздействием УСов. Адрес формируется

в БАКе.

2)--------

3)Перед выборкой очередной команды производится анализ запроса на прерывание. Для этого включается БП.

В состав ЦУУ включается блок для формирования исполнительных адресов – БПА. В его состав включаются: индексные, базовые регистры, а также схема алгебраического сложения. БТИ – Блок Тактовых Импульсов.

Назначение – формирование последовательности тактовых импульсов, которые позволяют провести временное развертывание цикла работы процессора.

ИПУ – обеспечивает:

а) пуск или остановку ЭВМ

б) выполнение процессором заданного режима

в) вывод на средства индикации

Слайд 14

АЛУ

Назначение – обработка информации (операции +, -,

>>, и т.д.) и логические операции. Кроме того в

малых и средних машинах, в которых нету отдельного БУО, связ. с формированием действительных адресов в АЛУ выполняется действия адресной арифметики или действия связанные с преобразованием адресов.

Алгоритм операции включает последовательность элем. действий:

прием кода операнда

преобразование кода операнда

суммирование кодов двух операндов

сдвиг кода операнда

выдача кода результата.

Слайд 15

АЛУ (2)

1) Регистры для хранения кодов операндов на

время выполнения действий над ними

2) Регистры сдвига вправо/влево на

один или несколько разрядов

3) Преобразователи для преобразования ПК в ОК или ДК.

4) Сумматор – для суммирования и других действий.

Самматоры делят по типу используемых для суммирования базовых элементов: 1) комбинационного 2) накапливающего и по способу осуществления 3) последовательнго и параллельного действия.

АЛУ ЭВМ малой производительности, сумматоры параллельного типа – средняя и высокая производительность (основа – совокупность Т-триггеров).

Слайд 16

АЛУ 3

Алгоритм работы:

1) перед суммированием по шине

сброс всех триггеров – уст. в 0 состояние (можно

использовать парафазное представление)

2) на счетные входы триггеров подается первое слагаемое и запоминается

3) на входы триггеров подается второе слагаемое.

4) триггер, в котором слагаемое=1 изменяет свое состояние на противоположное

5) переполнение разрядной сетки выявляется в результате переноса из старшего разряда и знакового.

Быстродействие параллельного сумматора ограничивается временем распространения переноса. Tпер=Т1(n~1). Для сокращения этого времени в сумматор включают цепь || переноса. В состав АЛУ входят: схема управления – руководство порядком выполнения последовательности микроопераций.

Слайд 17

Назначение и классификация АЛУ

Типы АЛУ:

используемая система

счисления

по формам представления числовых данных – с фиксированной или

плавающей запятой.

по виду связей между основными узлами – с непосредственной связью и с магистральной структурой.

Слайд 18

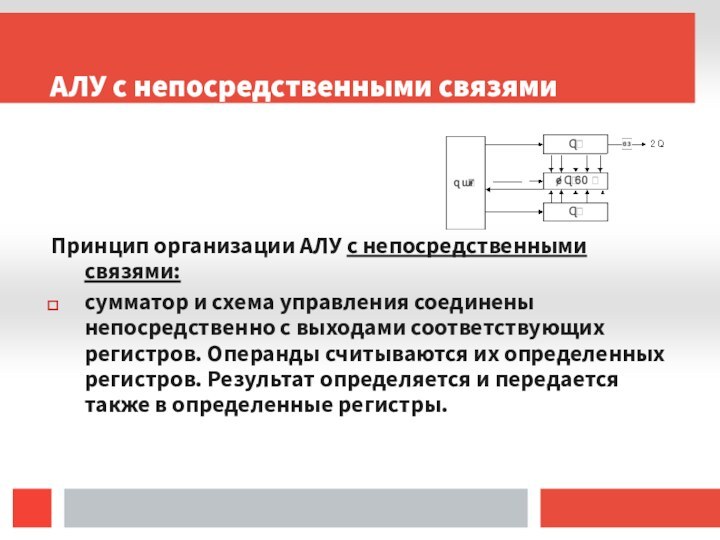

АЛУ с непосредственными связями

Принцип организации АЛУ с непосредственными

связями:

сумматор и схема управления соединены непосредственно с выходами соответствующих

регистров. Операнды считываются их определенных регистров. Результат определяется и передается также в определенные регистры.

Слайд 19

АЛУ магистральной структуры

Схемы для преобразования информации выделены

в отдельные блоки, включающие в себя сумматор и регистр

сдвига. Регистры служат лишь для хранения операндов во время их обработки. Вх/вых сумм регистров содержат только схемы приема и выдачи информации.

Слайд 20

Структура АЛУ для сложения и вычитания чисел с

фиксированной запятой

При выполнении сложения положительные слагаемые представляются в

прямом коде, отрицательные – в дополнительном. Производится сложение двоичных кодов, включая разряды знаков. Если при этом возникает перенос из знакового разряда суммы при отстуствии переноса в этот разряд или перенос в знаковый разряд при отсутствии переноса из разряда знака, то имеется переполнение разрядной сетки соответственно при отрицательной и положительной суммах. Если нет переносов из знакового разряда и в знаковый разряд суммы или есть оба этих переноса, то переполнения нет и при 0 в знаковом разряде сумма положительна, а при 1 отрицательна и представленя в ДК.

Слайд 21

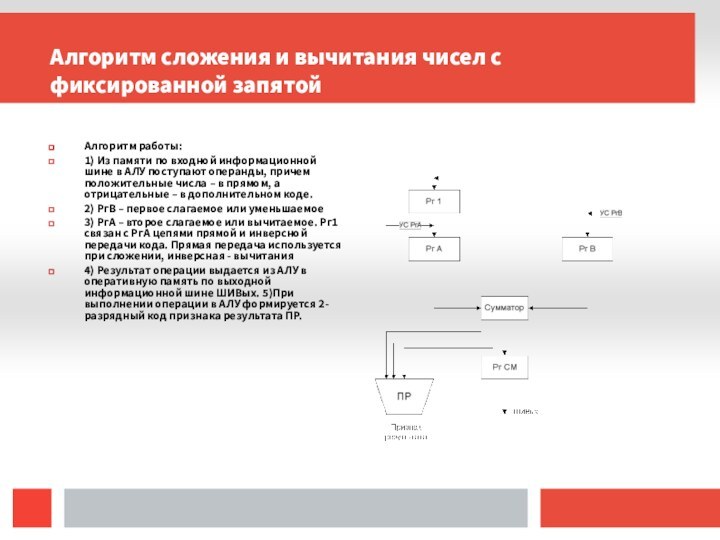

Алгоритм сложения и вычитания чисел с фиксированной запятой

Алгоритм

работы:

1) Из памяти по входной информационной шине в АЛУ

поступают операнды, причем положительные числа – в прямом, а отрицательные – в дополнительном коде.

2) РгВ – первое слагаемое или уменьшаемое

3) РгА – второе слагаемое или вычитаемое. Рг1 связан с РгА цепями прямой и инверсной передачи кода. Прямая передача используется при сложении, инверсная - вычитания

4) Результат операции выдается из АЛУ в оперативную память по выходной информационной шине ШИВых. 5)При выполнении операции в АЛУ формируется 2-разрядный код признака результата ПР.

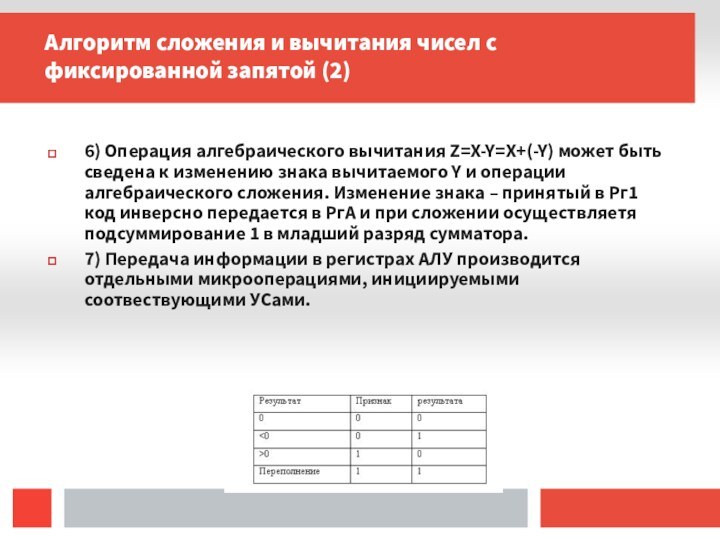

Слайд 22

Алгоритм сложения и вычитания чисел с фиксированной запятой

(2)

6) Операция алгебраического вычитания Z=X-Y=X+(-Y) может быть сведена к

изменению знака вычитаемого Y и операции алгебраического сложения. Изменение знака – принятый в Рг1 код инверсно передается в РгА и при сложении осуществляетя подсуммирование 1 в младший разряд сумматора.

7) Передача информации в регистрах АЛУ производится отдельными микрооперациями, инициируемыми соотвествующими УСами.

Слайд 23

Структура АЛУ для умножения чисел с фиксированной запятой

(сумматор

частичных произведений)

В ЭВМ операция умножения чисел с фиксированной запятой

с помощью соответствующих алгоритмов сводится к операциям сложения и сдвига. Произведение двух (n-1)-разрядных чисел может иметь 2(n-1) значащих разрядов. Т.о. при операции умножения целых чисел необходимо предусмотреть возможность формирования в АЛУ произведения, имеющего двойную по сравнению с сомножителем длину. В ЭВМ, в которых числа с фиксированной запятой являются дробями, младшие n-1 разрядов произвдения часто отбрасываются (возможно с операцией округления).

Слайд 24

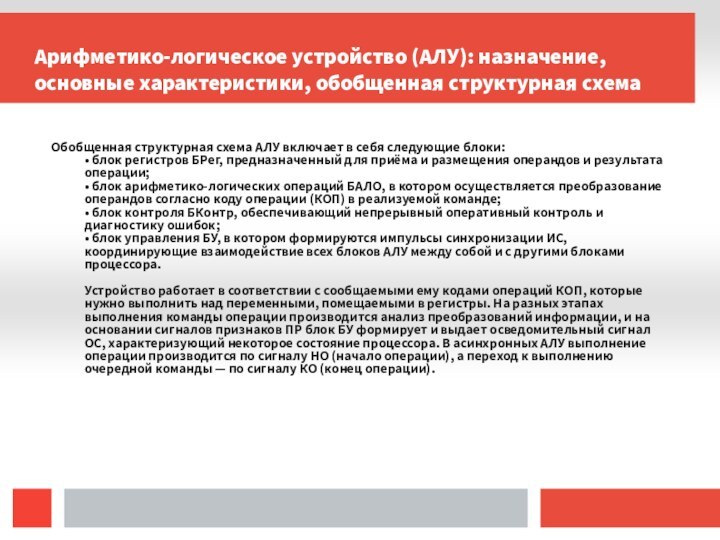

Арифметико-логическое устройство (АЛУ): назначение, основные характеристики, обобщенная структурная

схема

Обобщенная структурная схема АЛУ включает в себя следующие блоки:

•

блок регистров БРег, предназначенный для приёма и размещения операндов и результата операции;

• блок арифметико-логических операций БАЛО, в котором осуществляется преобразование операндов согласно коду операции (КОП) в реализуемой команде;

• блок контроля БКонтр, обеспечивающий непрерывный оперативный контроль и диагностику ошибок;

• блок управления БУ, в котором формируются импульсы синхронизации ИС, координирующие взаимодействие всех блоков АЛУ между собой и с другими блоками процессора.

Устройство работает в соответствии с сообщаемыми ему кодами операций КОП, которые нужно выполнить над переменными, помещаемыми в регистры. На разных этапах выполнения команды операции производится анализ преобразований информации, и на основании сигналов признаков ПР блок БУ формирует и выдает осведомительный сигнал ОС, характеризующий некоторое состояние процессора. В асинхронных АЛУ выполнение операции производится по сигналу НО (начало операции), а переход к выполнению очередной команды — по сигналу КО (конец операции).

Слайд 25

CISC против RISC

Принципиально новое, что отличает RISC- от

CISC-процессоров – это:

отсутствие аппаратного стека – все операнды хранятся

в регистрах общего назначения (РОН);

отсутствие регистра – счетчика команд;

наличие конвейера, позволяющего за один такт процессора осуществлять несколько вычислений;

четкое разделение потоков команд (инструкций) и данных;

полное равноправие РОН;

Слайд 26

Структура базового микропроцессора (МП) современных моделей для IMB-совместимых

ПЭВМ, взаимодействие его узлов и блоков

самостоятельно

Слайд 27

Параметры микропроцессоров

разрядность;

рабочая тактовая частота;

размер кэш-памяти;

состав

инструкций;

конструктив;

рабочее напряжение и т. д.

Слайд 28

Параметры микропроцессоров

Разрядность шины данных микропроцессора определяет количество разрядов,

над которыми одновременно могут выполняться операции; разрядность шины адреса

МП определяет его адресное пространство.

Адресное пространство -- это максимальное количество ячеек основной памяти, которое может быть непосредственно адресовано микропроцессором.

Рабочая тактовая частота МП во многом определяет его внутреннее быстро-действие, поскольку каждая команда выполняется за определенное количество тактов. Быстродействие (производительность) ПК зависит также и от тактовой частоты шины системной платы, с которой работает (может работать) МП.

Кэш-память, устанавливаемая на плате МП, имеет два уровня:

L1 -- память 1-го уровня, находящаяся внутри основной микросхемы (ядра) МП и работающая всегда на полной частоте МП (впервые кэш L1 был введен в МП i486 и в МП i386SLC);

L2 -- память 2-го уровня, кристалл, размещаемый на плате МП и связанный с ядром внутренней микропроцессорной шиной (впервые введен в МП Pentium II). Память L2 может работать на полной или половинной частоте МП. Эффективность этой кэш-памяти зависит и от пропускной способности микропроцессорной шины.

Слайд 29

Параметры микропроцессоров

Состав инструкций -- перечень, вид и тип

команд, автоматически исполняемых МП. От типа команд зависит классификационная

группа МП (CISC, RISC, VLIW и т. д.). Перечень и вид команд определяют непосредственно те процеду-ры, которые могут выполняться над данными в МП, и те категории данных, над которыми могут применяться эти процедуры. Дополнительные инструкции в не-больших количествах вводились во многих МП (286, 486, Pentium Pro и т. д.). Но существенное изменение состава инструкций произошло в МП i386 (этот со-став далее принят за базовый), Pentium MMX, Pentium III, Pentium 4.

Конструктив подразумевает те физические разъемные соединения, в которые устанавливается МП и которые определяют пригодность материнской платы для установки МП. Разные разъемы имеют разную конструкцию (Slot -- щеле-вой разъем, Socket -- разъем-гнездо), разное количество контактов, на которые подаются различные сигналы и рабочие напряжения.

Рабочее напряжение также является фактором пригодности материнской платы для установки МП.

Слайд 30

Кэш-память

Кэш – память

Это статическая память (Statiс RAM

– SRAM), которая, в отличие от динамической памяти, не

требует периодической регенерации (обновления). Время доступа у этой памяти не более 2 нс., т. е. она может синхронно работать с процессором на частоте 500 МГц и более. Контроллер кэш – памяти находится в чипе северного моста чипсета материнской платы.

В x386 процессорах кэш – память объемом 128 Кб располагалась на материнской плате. Начиная с процессоров x486, появился дополнительный кэш в процессоре, работающий на его частоте, - кэш первого уровня (Level I – LI). На материнской плате устанавливается кэш второго уровня (L2). В большинстве современных процессоров кэш LI и L2 встроены в ядро процессора. Причем если в Pentium II и Pentium III кэш второго уровня работает на половинной частоте процессора, то у Celeron, AMD K6 – III, Athlon и Pentium IV – на частоте процессора, что положительно сказывается на производительности.

Слайд 31

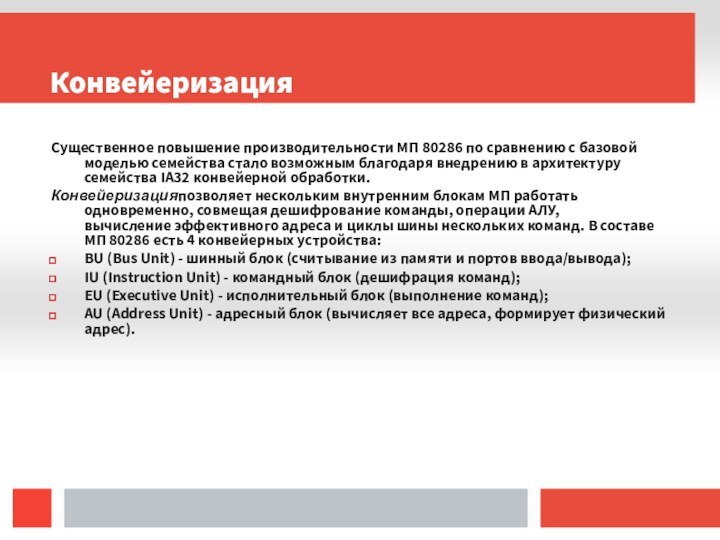

Конвейеризация

Существенное повышение производительности МП 80286 по сравнению с

базовой моделью семейства стало возможным благодаря внедрению в архитектуру семейства IA32

конвейерной обработки.

Конвейеризацияпозволяет нескольким внутренним блокам МП работать одновременно, совмещая дешифрование команды, операции АЛУ, вычисление эффективного адреса и циклы шины нескольких команд. В составе МП 80286 есть 4 конвейерных устройства:

BU (Bus Unit) - шинный блок (считывание из памяти и портов ввода/вывода);

IU (Instruction Unit) - командный блок (дешифрация команд);

EU (Executive Unit) - исполнительный блок (выполнение команд);

AU (Address Unit) - адресный блок (вычисляет все адреса, формирует физический адрес).

Слайд 32

Конвейеризация в 286

Конвейеризация команд в МП 80286

Слайд 33

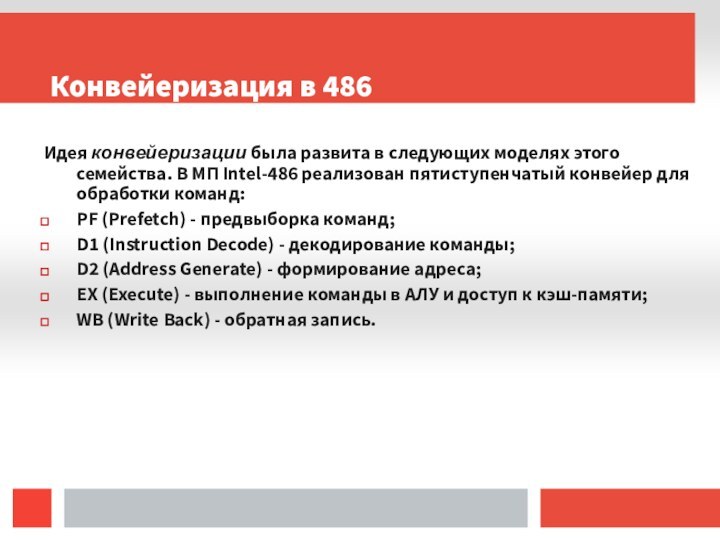

Идея конвейеризации была развита в следующих моделях этого семейства. В

МП Intel-486 реализован пятиступенчатый конвейер для обработки команд:

PF (Prefetch)

- предвыборка команд;

D1 (Instruction Decode) - декодирование команды;

D2 (Address Generate) - формирование адреса;

EX (Execute) - выполнение команды в АЛУ и доступ к кэш-памяти;

WB (Write Back) - обратная запись.

Конвейеризация в 486

Слайд 34

Конвейеризация в Pentium

Блок-схема архитектуры МП Pentium

Слайд 35

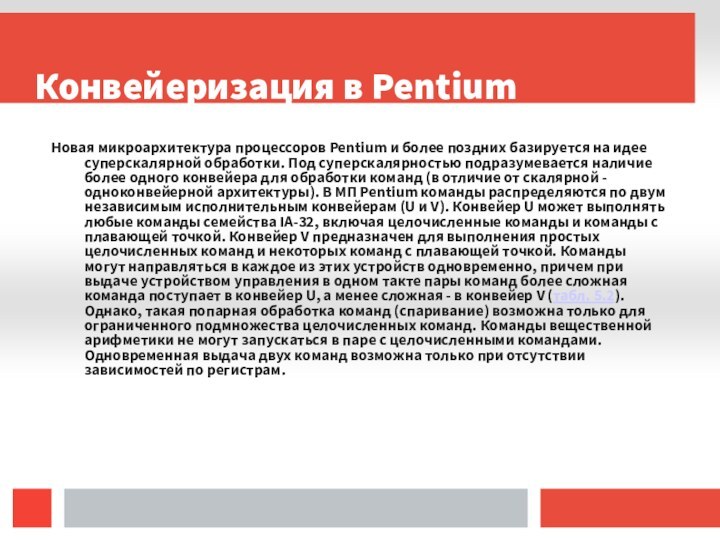

Конвейеризация в Pentium

Новая микроархитектура процессоров Pentium и более

поздних базируется на идее суперскалярной обработки. Под суперскалярностью подразумевается

наличие более одного конвейера для обработки команд (в отличие от скалярной - одноконвейерной архитектуры). В МП Pentium команды распределяются по двум независимым исполнительным конвейерам (U и V). Конвейер U может выполнять любые команды семейства IA-32, включая целочисленные команды и команды с плавающей точкой. Конвейер V предназначен для выполнения простых целочисленных команд и некоторых команд с плавающей точкой. Команды могут направляться в каждое из этих устройств одновременно, причем при выдаче устройством управления в одном такте пары команд более сложная команда поступает в конвейер U, а менее сложная - в конвейер V (табл. 5.2). Однако, такая попарная обработка команд (спаривание) возможна только для ограниченного подмножества целочисленных команд. Команды вещественной арифметики не могут запускаться в паре с целочисленными командами. Одновременная выдача двух команд возможна только при отсутствии зависимостей по регистрам.

Слайд 36

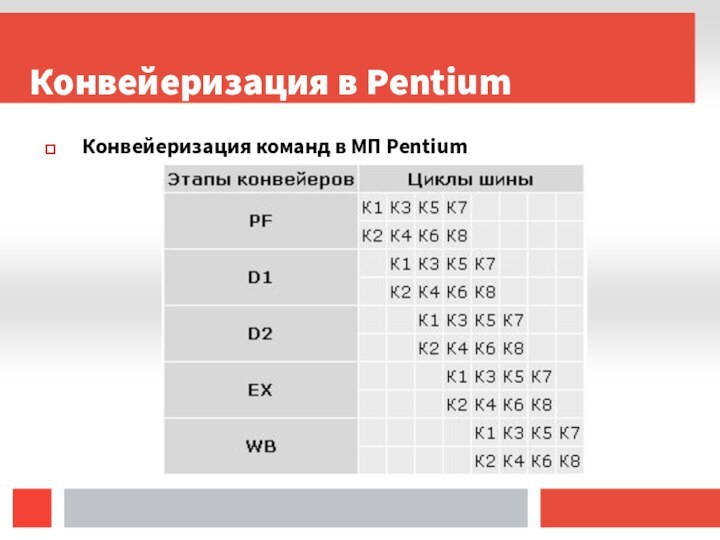

Конвейеризация в Pentium

Конвейеризация команд в МП Pentium

Слайд 37

Динамическое (спекулятивное) исполнение

Одной из главных особенностей шестого поколения

микропроцессоров архитектуры IA32 является динамическое(спекулятивное) исполнение. Под этим термином подразумевается следующая

совокупность возможностей:

Глубокое предсказание ветвлений (с вероятностью >90% можно предсказать 10-15 ближайших переходов).

Анализ потока данных (на 20-30 шагов вперед просмотреть программу и определить зависимость команд по данным или ресурсам).

Опережающее исполнение команд (МП P6 может выполнять команды в порядке, отличном от их следования в программе).

Слайд 38

Особенности P6

Внутренняя организация МП P6 соответствует архитектуре RISC,

поэтому блок выборки команд, считав поток инструкций IA-32 из

L1 кэша инструкций, декодирует их в серию микроопераций. Поток микроопераций попадает в буфер переупорядочивания (пул инструкций). В нем содержатся как не выполненные пока микрооперации, так и уже выполненные, но еще не повлиявшие на состояние процессора. Для декодирования инструкций предназначены три параллельных дешифратора: два для простых и один для сложных инструкций. Каждая инструкция IA-32 декодируется в 1-4 микрооперации. Микрооперации выполняются пятью параллельными исполнительными устройствами: два для целочисленной арифметики, два для вещественной арифметики и блок интерфейса с памятью. Таким образом, возможно выполнение до пяти микроопераций за такт.

Слайд 39

Особенности P6

Блок исполнительных устройств способен выбирать инструкции из

пула в любом порядке. При этом благодаря блоку предсказания

ветвлений возможно выполнение инструкций, следующих за условными переходами. Блок резервирования постоянно отслеживает в пуле инструкций те микрооперации, которые готовы к исполнению (исходные данные не зависят от результата других невыполненных инструкций) и направляет их на свободное исполнительное устройство соответствующего типа. Одно из целочисленных исполнительных устройств дополнительно занимается проверкой правильности предсказания переходов. При обнаружении неправильно предсказанного перехода все микрооперации, следующие за переходом, удаляются из пула и производится заполнение конвейера команд инструкциями по новому адресу.

Взаимная зависимость команд от значения регистров архитектуры IA-32 может требовать ожидания освобождения регистров. Для решения этой проблемы предназначены 40 внутренних регистров общего назначения, используемых в реальных вычислениях.

Слайд 40

Разрядность

Разрядность

Первые процессорные регистры могли хранить лишь 4

– битные числа. Затем появились 8 – и 16

– битные процессоры, с появлением процессора x386 был реализован 32 – битный режим, что позволило работать с числами размерностью свыше двух миллиардов.

Слайд 41

Блок схема микропроцессора Pentium Pro

Слайд 42

Технология производства МП

Выращивание диоксида кремния и создание проводящих

областей

Тестирование

Изготовление корпуса.

Доставка.

Слайд 43

Технология производства

http://www.modlabs.net/articles/sovremennye-mikroprocessory

Слайд 45

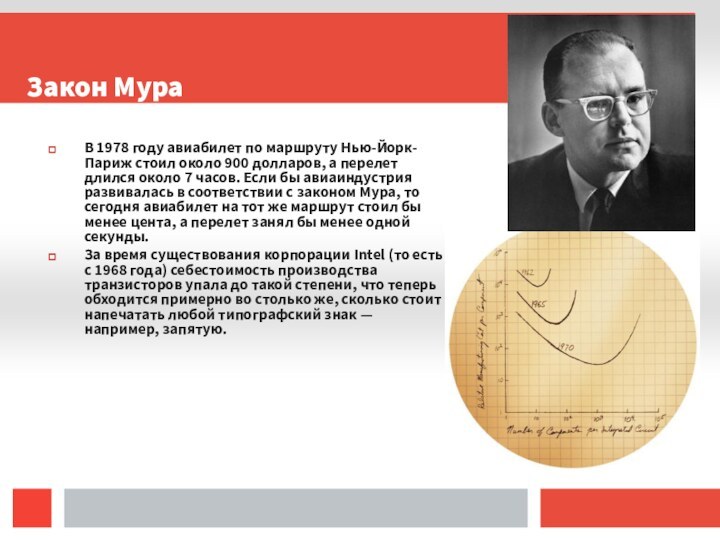

Закон Мура

50 лет назад микроэлектроника пребывала в зачаточном

состоянии. Чипов тогда производилось совсем мало, в самой сложной

микросхеме компании Fairchild было всего 64 транзистора, о каких-либо достоверных статистических данных в этой отрасли не приходилось и говорить. Остается лишь поражаться, как в таких обстоятельствах Гордон Мур сумел предугадать фантастические темпы развития всей отрасли на несколько десятилетий вперед и предсказать, что количество транзисторов на чипе ежегодно будет удваиваться. Более того, одновременно он сделал провидческий прогноз последствий этого, предсказав, что по мере экспоненциального увеличения числа транзисторов на микросхеме процессоры будут становиться все более дешевыми и быстродействующими, а их производство — все более массовым.

В своей первоначальной формулировке он действовал до 1975 года, когда, выступая на конференции «International Electron Devices Meeting», Гордон Мур внес в него коррективы, высказав предположение, что при производстве все более сложных чипов удвоение числа транзисторов будет происходить каждые два года. И опять он оказался прав, разве что в последние годы количество транзисторов на микропроцессоре порой удваивается с интервалом в полтора года.