Слайд 2

История возникновения микроэлектроники.

Открытие транзистора

Начало развитию микроэлектроники было

положено в 1947г., когда сотрудники «Лаборатории Белла» Уильям Шокли,

Джон Бардин и Уолтер Браттейн создали биполярный транзистор.

В 1956 году они были награждены Нобелевской премией по физике «за исследования полупроводников и открытие транзисторного эффекта».

Транзисторы заменили вакуумные лампы в большинстве электронных устройств, совершив революцию в создании интегральных схем и компьютеров.

Слово «транзистор» (transistor, образовано от слов transfer — передача и resist — сопротивление),

Сверху вниз: Шокли, Бардин, Браттейн

Слайд 3

История возникновения микроэлектроники.

Открытие интегральной микросхемы

В 1958 году

двое учёных, работавших в разных компаниях, изобрели практически идентичную

модель интегральной схемы. Один из них, Джек Килби, работал на Texas Instruments, другой, Роберт Нойс, был одним из основателей небольшой компании по производству полупроводников Fairchild Semiconductor. Обоих объединил вопрос: «Как в минимум места вместить максимум компонентов?». Транзисторы, резисторы, конденсаторы и другие детали в то время размещались на платах отдельно, и учёные решили попробовать их объединить на одном монолитном кристалле из полупроводникового материала. Только Килби воспользовался германием, а Нойс предпочёл кремний.

В1961 году Fairchild пустила интегральные схемы в свободную продажу, и их сразу стали использовать в производстве калькуляторов и компьютеров вместо отдельных транзисторов, что позволило значительно уменьшить размер и увеличить производительность.

Сверху вниз: Д.Килби, Р.Нойс,

Слайд 4

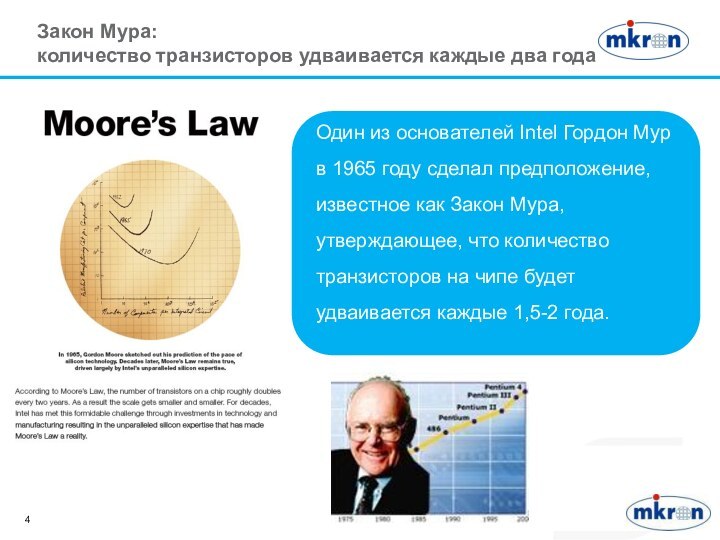

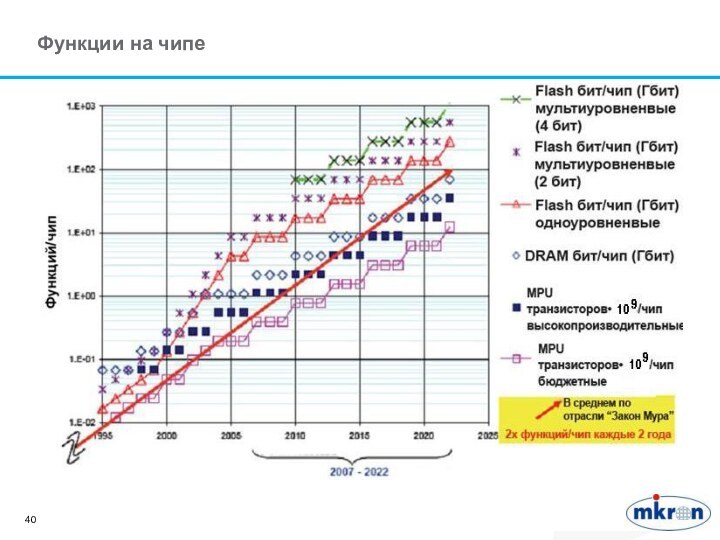

Один из основателей Intel Гордон Мур в 1965

году сделал предположение, известное как Закон Мура, утверждающее, что

количество транзисторов на чипе будет удваивается каждые 1,5-2 года.

Закон Мура:

количество транзисторов удваивается каждые два года

Слайд 5

Закон Мура

Сам Мур так оценивает выполнение своего

правила

Слайд 6

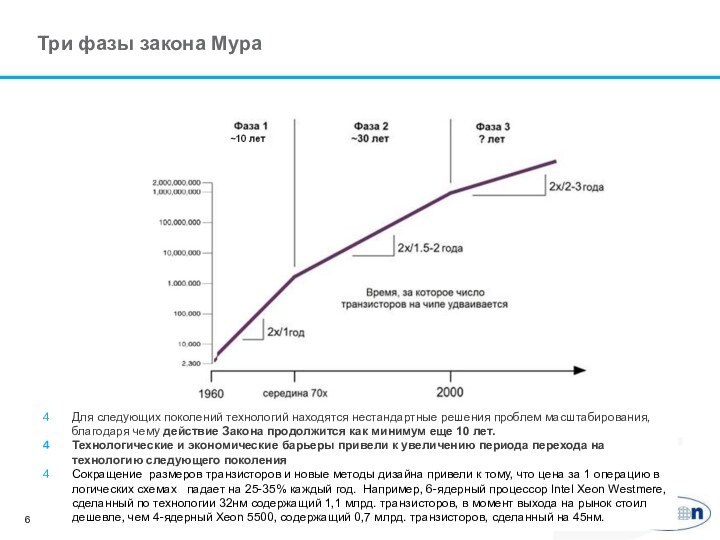

Три фазы закона Мура

Для следующих поколений технологий находятся

нестандартные решения проблем масштабирования, благодаря чему действие Закона продолжится

как минимум еще 10 лет.

Технологические и экономические барьеры привели к увеличению периода перехода на технологию следующего поколения

Сокращение размеров транзисторов и новые методы дизайна привели к тому, что цена за 1 операцию в логических схемах падает на 25-35% каждый год. Например, 6-ядерный процессор Intel Xeon Westmere, сделанный по технологии 32нм содержащий 1,1 млрд. транзисторов, в момент выхода на рынок стоил дешевле, чем 4-ядерный Xeon 5500, содержащий 0,7 млрд. транзисторов, сделанный на 45нм.

Слайд 7

Изменение топологических размеров в производстве

Ист. ITRS

Слайд 9

Основные этапы маршрута проектирования

Систем-на-Кристалле

Разработка RTL описания

(VHDL/Verilog)

Логический синтез

моделирование

Разработка

топологии

Верификация топологии

Проверка на КТО и соответствие

электрической схеме

Экстракция из топологии

RC-элементов

схемы

Моделирование схемы и

статический временной анализ

Синтез топологии ФШ

включая ОРС

Слайд 10

Основные технологические операции

1. Перенос изображения.

1.1 Оптическая иммерсионная

литография (Photo ArFi), обеспечивает разрешение до 20 нм в

технологии двойного экспонирования DP.

1.2 Плазмохимическое травление (ПХТ/Plasma Etch), преимущественно реактивно – ионное (RIE).

2. Химическое осаждение (CVD), плазмо-стимулированное осаждение (PECVD) и осаждение при низком давлении (LPCVD), включая атомно-слоевое осаждение (LAD) диэлектриков, металлов, барьерных слоёв, жестких масок.

3. Процессы напыления зародышевых, металлических слоёв (PVD).

4. Процессы ионной имплантации (Implant) .

5. Процессы электрохимического осаждения меди (Cu plating) .

6. Процессы химико–механической планаризации (ХМП/CMP) диэлектриков, меди, вольфрама.

7. Термо–диффузионные процессы (Diffusion)

8. Процессы быстрого термического отжига (RTP)

9. Метрологические операции по всему маршруту, включая контроль дефектности (Metro)

10. Процессы жидкостной химии по всему маршруту Х/О (Wet).

Слайд 11

Основные задачи при уменьшении проектной нормы

Проблемы(уменьшение разброса) технологических

операций (Photo, Plasma Etch, Impl, CMP, Wet, CVD, PECVD,

LPCVD, PVD, LAD, RTP, Cu plating, Metro, Test).

2. Уменьшение задержки в RC-цепочках межсоединений . Их влияние на задержку сильно возрастает, т.к. задержка в транзисторе уменьшается, а в межсоединениях возрастает, нобходима оптимизация.

Уменьшение уд. сопротивления металлической разводки и использование Low-K диэлектриков

3. Снижение уровня утечек в активном и пассивном

режимах . Возрастает плотность статической

потребляемой мощности из – за токов утечек и

становится сравнимой с динамической мощностью

4. Обеспечение приемлемого значения сигнал/шум

5. Обеспечение контроля электромиграции медных

проводников с помощью барьерных слоёв,

блокирующих диффузию

Слайд 12

Энергетические проблемы

Горячая плита

101000

00

Ватт/см²

Ядерный реактор

Поверхность

солнца

Ракетный двигатель

Слайд 13

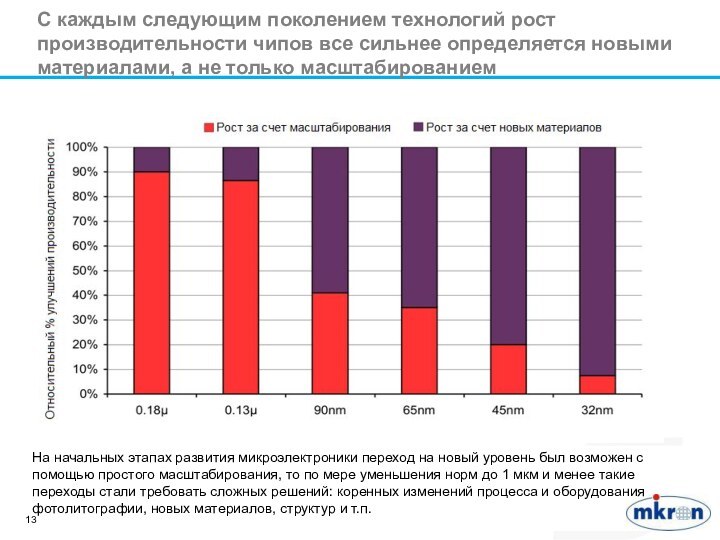

С каждым следующим поколением технологий рост производительности чипов

все сильнее определяется новыми материалами, а не только масштабированием

На

начальных этапах развития микроэлектроники переход на новый уровень был возможен с помощью простого масштабирования, то по мере уменьшения норм до 1 мкм и менее такие переходы стали требовать сложных решений: коренных изменений процесса и оборудования фотолитографии, новых материалов, структур и т.п.

Слайд 14

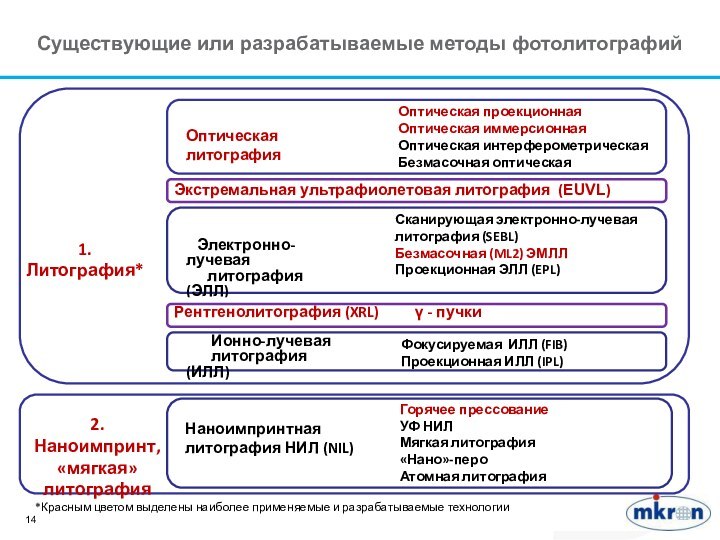

Существующие или разрабатываемые методы фотолитографий

*Красным цветом выделены наиболее

применяемые и разрабатываемые технологии

Слайд 16

Проблемы дальнейшего развития по Закону Мура:

Удельное сопротивление

Cu

Поскольку шаг межсоединений продолжает сокращаться, более высокое электрическое сопротивление

будет связано не только с удельным сопротивлением меди, но также и с другими источниками, например, рассеянием на границе зерен и поверхностным рассеянием электронов. Покрытие CoWP

Как показано на рисунке, эти вторичные источники сопротивления начинают доминировать при минимальных размерах элементов ИС менее 30нм.

Слайд 17

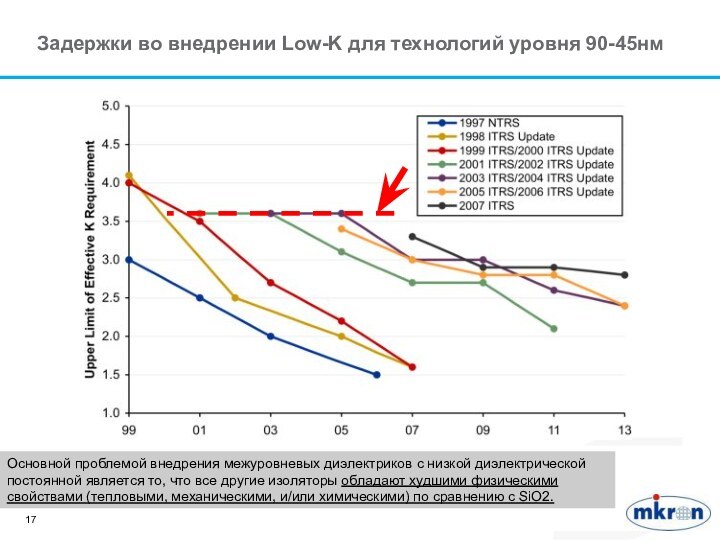

Задержки во внедрении Low-K для технологий уровня 90-45нм

Основной

проблемой внедрения межуровневых диэлектриков с низкой диэлектрической постоянной является

то, что все другие изоляторы обладают худшими физическими свойствами (тепловыми, механическими, и/или химическими) по сравнению с SiO2.

Слайд 18

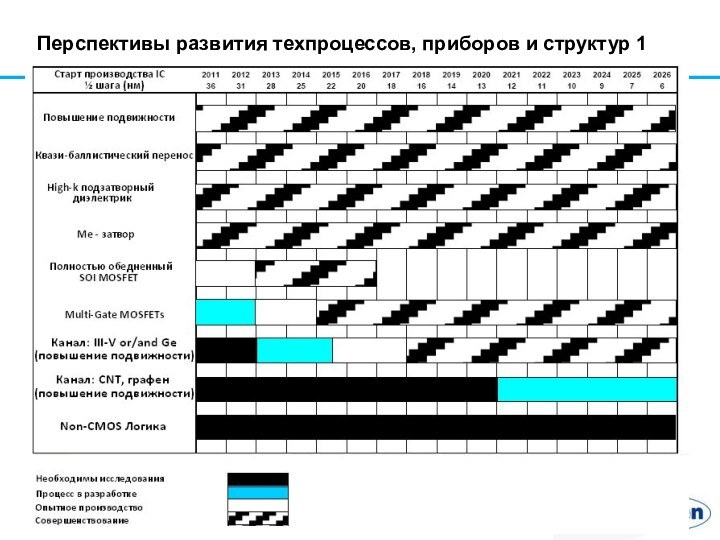

Перспективы развития техпроцессов, приборов и структур 1

Слайд 19

Перспективы развития техпроцессов, приборов и структур 2

Слайд 21

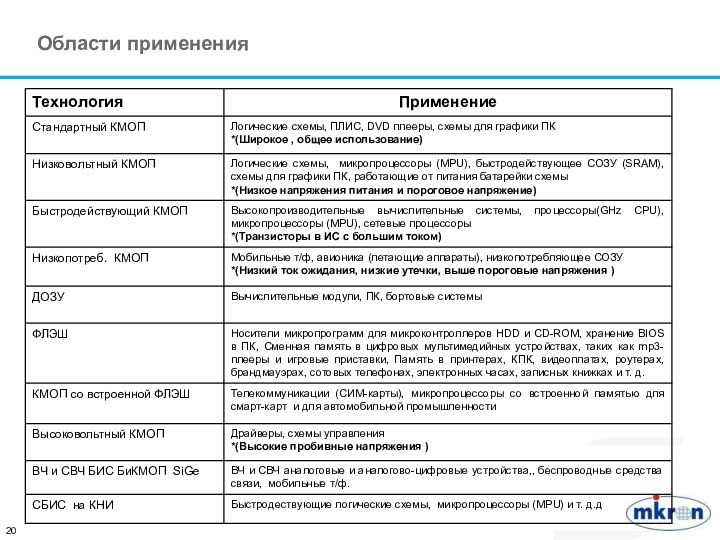

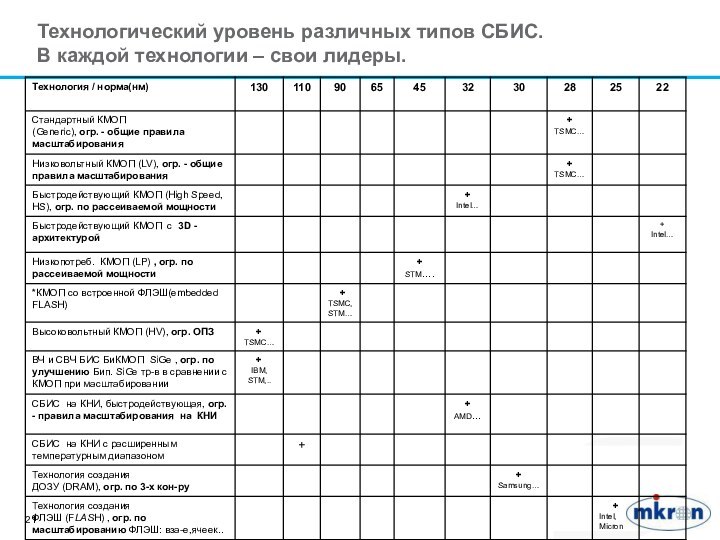

Технологический уровень различных типов СБИС. В каждой технологии

– свои лидеры.

Слайд 22

Стартовая

Состояние по разработке новых технологий в ОАО «НИИМЭ»

Семейство технологий с проектными нормами 180 нм

В течение последних

5 лет в развитие технологий и производства инвестировано около $1 млрд.

Слайд 23

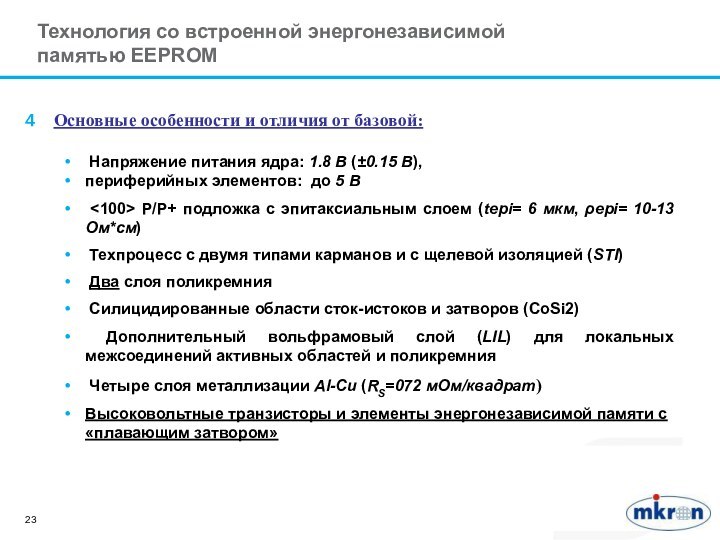

Технология со встроенной энергонезависимой памятью EEPROM

Основные особенности и

отличия от базовой:

Напряжение питания ядра: 1.8 В (±0.15

В),

периферийных элементов: до 5 В

<100> P/P+ подложка с эпитаксиальным слоем (tepi= 6 мкм, ρepi= 10-13 Ом*см)

Техпроцесс с двумя типами карманов и с щелевой изоляцией (STI)

Два слоя поликремния

Силицидированные области сток-истоков и затворов (CoSi2)

Дополнительный вольфрамовый слой (LIL) для локальных межсоединений активных областей и поликремния

Четыре слоя металлизации Al-Cu (RS=072 мОм/квадрат)

Высоковольтные транзисторы и элементы энергонезависимой памяти с «плавающим затвором»

Слайд 24

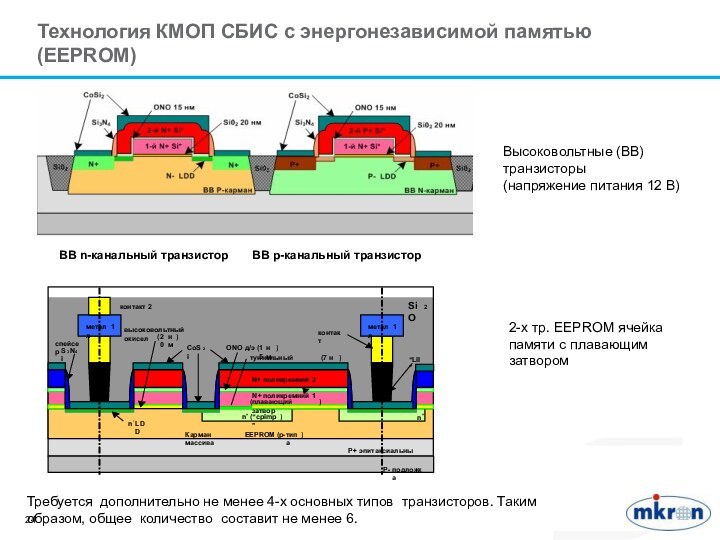

Технология КМОП СБИС с энергонезависимой памятью (EEPROM)

ВВ n-канальный

транзистор

ВВ p-канальный транзистор

Высоковольтные (ВВ) транзисторы

(напряжение питания 12 В)

2-х

тр. EEPROM ячейка памяти с плавающим затвором

Требуется дополнительно не менее 4-х основных типов транзисторов. Таким образом, общее количество составит не менее 6.

Слайд 25

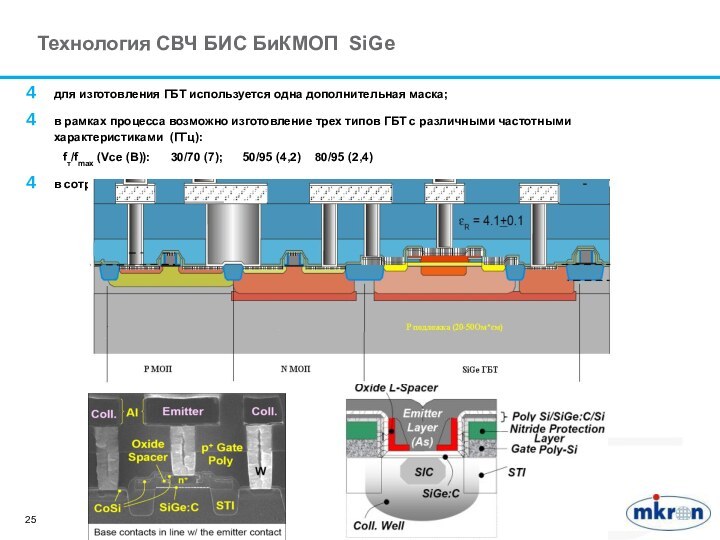

Технология СВЧ БИС БиКМОП SiGe

для изготовления ГБТ используется

одна дополнительная маска;

в рамках процесса возможно изготовление трех типов

ГБТ с различными частотными характеристиками (ГГц):

fт/fmax (Vce (В)): 30/70 (7); 50/95 (4,2) 80/95 (2,4)

в сотрудничестве с компанией IHP ведется разработка элементов с частотой 16ГГц

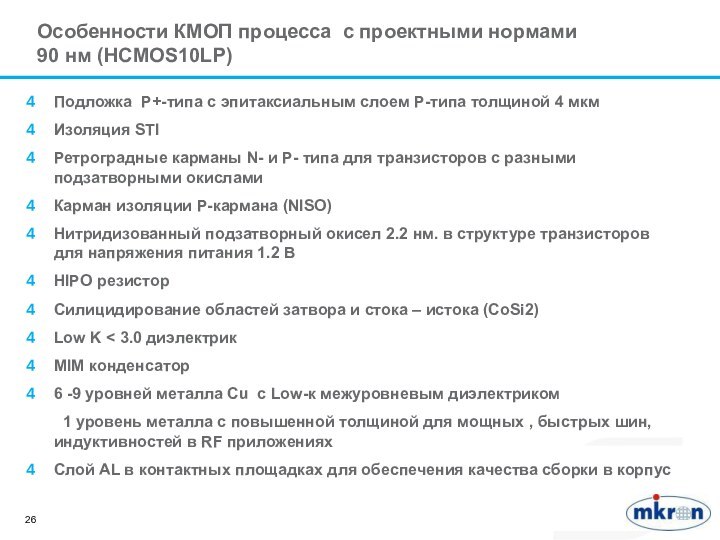

Слайд 26

Особенности КМОП процесса с проектными нормами 90 нм

(НСMOS10LP)

Подложка Р+-типа с эпитаксиальным слоем Р-типа толщиной 4 мкм

Изоляция

STI

Ретроградные карманы N- и P- типа для транзисторов с разными подзатворными окислами

Карман изоляции Р-кармана (NISO)

Нитридизованный подзатворный окисел 2.2 нм. в структуре транзисторов для напряжения питания 1.2 В

НIPO резистор

Силицидирование областей затвора и стока – истока (CоSi2)

Low K < 3.0 диэлектрик

MIM конденсатор

6 -9 уровней металла Сu с Low-к межуровневым диэлектриком

1 уровень металла с повышенной толщиной для мощных , быстрых шин, индуктивностей в RF приложениях

Слой AL в контактных площадках для обеспечения качества сборки в корпус

Слайд 27

Технологический процесс с проектными нормами

90 нм HCMOS10LP 2011

год

GO1

2.2Å (LP)

Два VT

6 - 9 слоев Ме

6M1T, 7M2T, 8M2T

and 9M2T

СОЗУ

Один VT / Низкое VT

GO2

50 Å

Один VT

+2 маски / уровень Ме

+1 маска

Без дополнений

-2/+2 маски

+1 маска

+2 маски

+4 маски

Базовый процесс 90 нм

34 маски, 35 слоев

6 уровней металлизации Cu

(5 тонких + 1 толстый)

Два подзатворных оксида, два Vt процесса

Стандартные Vt транзисторы SVT,

высоковольтные транзисторы НVT

Vdd 1.2В (маломощные)

с возможностью 2.5В I/O

Слайд 28

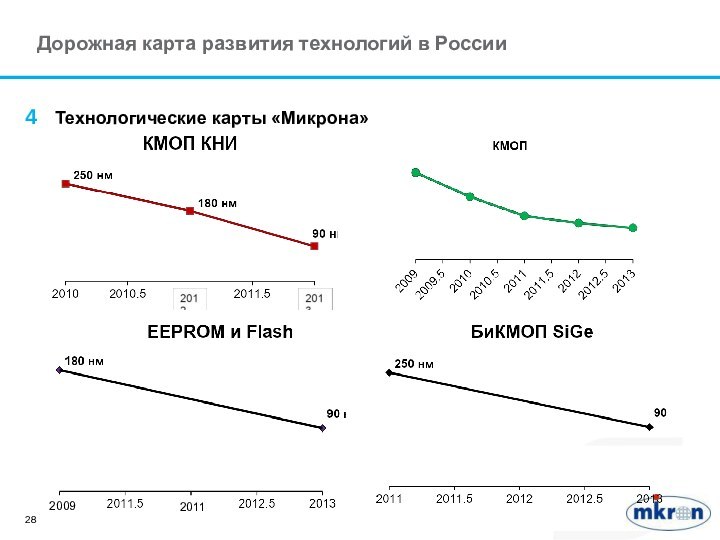

Технологические карты «Микрона»

Дорожная карта развития технологий в России

2009

2011

Слайд 29

Технологии памяти.

1 –транзисторная FLASH ячейка памяти с

плавающим затвором

Электрическая схема архитектуры NOR и сечение матрицы 1-транзисторных

ячеек. С повышением степени интеграции СБИС необходимо уменьшать размер ячейки

Слайд 30

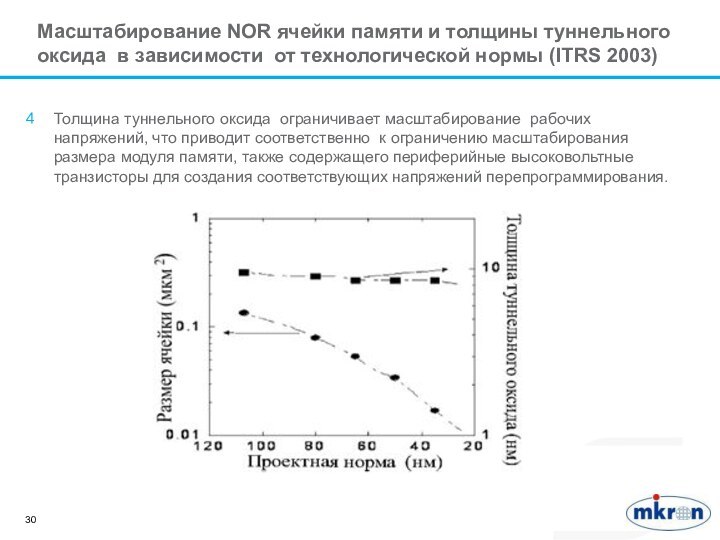

Толщина туннельного оксида ограничивает масштабирование рабочих напряжений, что

приводит соответственно к ограничению масштабирования размера модуля памяти,

также содержащего периферийные высоковольтные транзисторы для создания соответствующих напряжений перепрограммирования.

Масштабирование NOR ячейки памяти и толщины туннельного оксида в зависимости от технологической нормы (ITRS 2003)

Слайд 31

Потребность в других видах энергонезависимой памяти

Из-за ограничений

Flash-памяти, которая, тем не менее, продолжает эволюционное развитие (новые

конструкции и технологии), появилась потребность в других «революционных» (новые физические принципы) видах памяти (FRAM, MRAM, PCM…..)

Желательны следующие характеристики:

Показатели функционирования:

Увеличенное количество циклов перезаписи

Более быстрое время записи, считывания

Большая гибкость (уровень модульности)

Масштабируемость:

Большая масштабируемость по сравнению с Flash

Разработка и технология:

Более простое встраивание (интеграция) в логические ИС

Слайд 32

Другие виды энергонезависимой памяти

Сегнетоэлектрическая (FRAM)

Механизм записи –

электрическое поле, создаваемое

в слое сегнетоэлектрика при помощи напряжения,

прикладываемого

к пластинам конденсатора

Магнитная (MRAM)

Принцип основан на изменении сопротивления элемента памяти

при воздействии импульса тока в цепи записи – стирания.

Основное преимущество – отсутствие высоковольтных цепей.

На основе изменения фазового состава (PCM)

Механизм хранения – аморфная/ поликристаллическая фаза

халькогенидного сплава (Ge2Sb2Te5, GST)

Механизм записи – индуцируемый током эффект Джоуля

Механизм распознавания – изменение сопротивления GST

Слайд 33

Ячейки памяти на основе нанокластеров. Достоинства и недостатки.

Поиск

универсальной памяти продолжается.

Типовая ячейка энергонезависимой памяти на основе плавающего

затвора (слева) и ячейка энергонезависимой памяти на основе ловушек заряда с помощью кремниевых нанокристаллов, расположенных в слое диоксида кремния (справа).

Преимущества энергонезависимой памяти на нанокристаллах:

энергонезависимая память на кремниевых нанокристаллах подобна памяти на основе накопления заряда в нитриде (SONOS);

уменьшено влияние дефектов в изолирующем оксиде;

упрощен процесс формирования ячеек памяти;

использование нанокластеров приводит к более эффективному стиранию и программированию и улучшенной устойчивости к дефектам по сравнению с типовой энергонезависимой памятью на плавающем затворе.

К недостаткам следует отнести невозможность масштабирования до размеров длины канала, сравнимой с нанокластером ( ~ 10 нм), из-за разброса их размеров и расстояния между ними происходит разброс параметров элемента памяти, таких как пороговое напряжение, окно памяти и т.д.

Слайд 34

SONOS : преимущества и недостатки

Время жизни электронов

в локализованном состоянии составляет более 10 лет. Высокая эффективность

захвата электронов (или дырок) связана с большим сечением захвата на ловушки (порядка 10-13 см2) и большой их концентрацией (порядка 1019 см-3).

Появление локальной утечки в окисле не приводит к стеканию в подложку основной части информационного заряда, как это имело бы место в случае с проводящим плавающим затвором, поскольку заряд локализован на изолированных ловушках.

Совместимость с типовой КМОП технологией и снижение напряжения перепрограммирования до 8-9 В с перспективой дальнейшего его уменьшения упрощают разработку устройств и используемые технологические процессы.

При выборе конструкции элемента памяти необходимо оптимизировать взаимно противоречивые требования: время перепрограммирования, большое число циклов запись-стирание, время хранения.

Использование блокирующего диэлектрика с большой диэлектрической проницаемостью (high- k) позволяет увеличить толщину туннельного диэлектрика, улучшить температурный диапазон. Данная память может быть масштабирована до размеров 30 - 20 нм.

Поиск новых конструктивно – технологических вариантов, типа BE-SONOS

Поэтому использование многослойного диэлектрика ONO со слоем нитрида кремния представляется перспективным.

Слайд 36

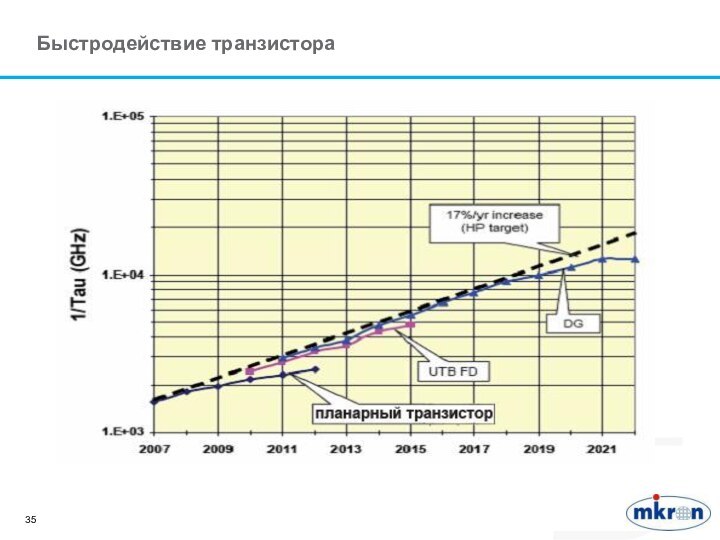

Сравнение типового МОП транзистора с UTB FD транзистором

П

о ITRS основной прогресс до 2021 будет связан с

КНИ - технологией

UTB FD - полевой транзистор с ультратонким (менее 10 нм) нелегированным полностью обедненным каналом (КНИ).

Основные преимущества UTB FD :

баллистический перенос носителей, увеличение тока и быстродействия

низкие токи утечки закрытого состояния

Типовой МОП транзистор

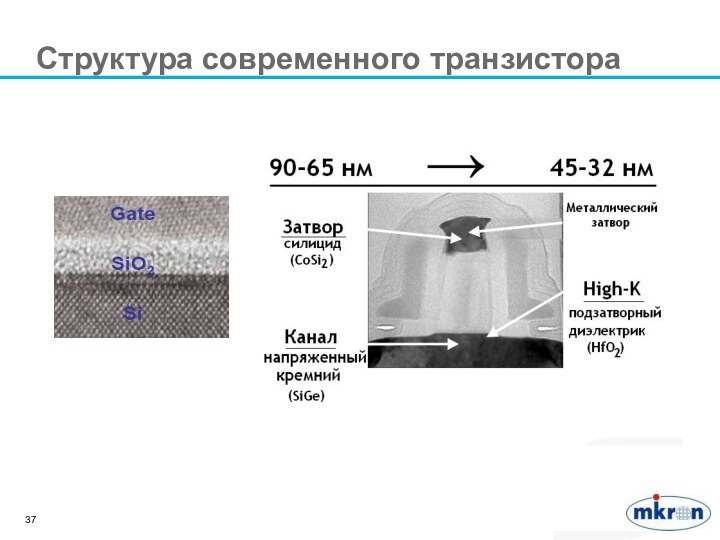

Слайд 37

Структура современного транзистора

Слайд 38

Многозатворные транзисторы (Fin,…)

Общее направление большинства модификаций классической

архитектуры полевого транзистора состоит в переходе к 3D-структуре

Интел

планировал перейти на Fin FET на уровне 22нм, но переход отложен до 15нм.

22 нм транзисторы ф.Интел

Слайд 39

Прогноз развития инновационных технологий (источник: Intel)

Слайд 41

Развитие процессоров и памяти.

Ни одна отрасль не изменила

мир и социальных уклад так, как микроэлектроника.

Рост производительности и

сложности чипов позволяет просчитывать все более точные модели, создавать искусственный интеллект и самообучающиеся нейронные сети.

К 2022г. Суперкомпьютер будет размещен на одном чипе.

Слайд 42

При длине канала L около менее 6 нм

– большие точки утечки между стоком и истоком за

счет прямого тунелирования носителей.

Необходимость использования новых материалов, конструкций и приборов на новых физически принципах

Физический предел и проблемы при длине канала <10 нм

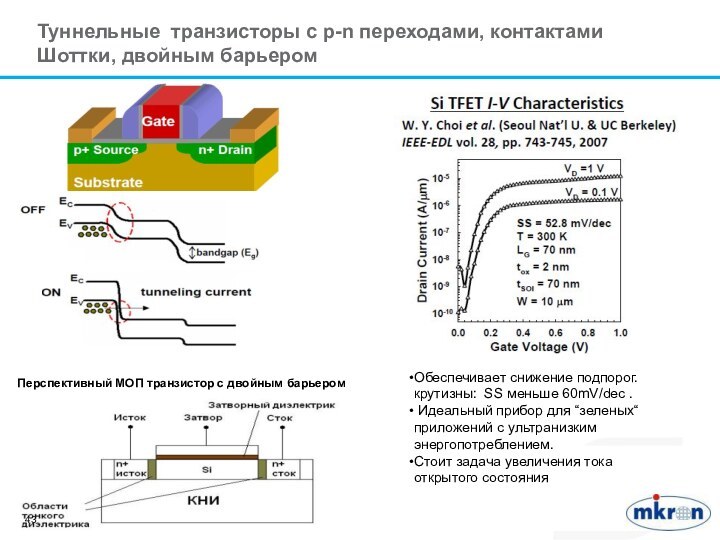

Слайд 43

Обеспечивает снижение подпорог. крутизны: SS меньше 60mV/dec .

Идеальный прибор для “зеленых“ приложений с ультранизким энергопотреблением.

Стоит

задача увеличения тока открытого состояния

Перспективный МОП транзистор с двойным барьером

Туннельные транзисторы c p-n переходами, контактами Шоттки, двойным барьером

Слайд 44

Окружение области канала затвором естественным образом стимулирует применение

«Nanowire» ( нанопроволок и нанотрубок)

Полевой транзистор с каналом из

нанопроволоки (или углеродной нанотрубки) в качестве биохимического сенсора.

Источник: http://astro.temple.edu

Сечение структуры с волнообразным рельефом

с λ =150 нм в α-Si для получения «Nanowire», 30-40нм

Источник: Отличительные особенности и проблемы

КМОП технологии при уменьшении проектной нормы

до уровня 0,18 мкм и меньше / Красников Г.Я., Орлов О.М.

// Российские нанотехнологии, 2008 , Том 3, N 7 - 8, C. 124-128.

Транзисторы на основе «Nanowire»

Слайд 45

Одноэлектронный транзистор (слева -- схема, справа – реализация).

Источник:

Преснов Д.Е., МГУ, 2010г.

http://www.nanometer.ru/2010/

02/18/silicon_168602.html

Хотя идея одноэлектронного транзистора предложена К.

Лихаревым в 1986г., до сих пор имеются только лабораторные разработки одноэлектронных транзисторов (SET).

Молекулярный транзистор.

Источник: Electronics below 10nm, K.Likharev, http://pavel.physics.sunysb.edu/~likharev/nano/NanoGiga.pdf

Идея МТ близка к идее SET. Целевой молекулой может быть белок или фрагмент нуклеиновой кислоты.

Спиновый транзистор, предполагаемый конкурент обычного полевого транзистора. Достижение преимуществ: низкое управляющее напряжение, малое энергопотребление, высокое быстродействие пока противоречиво. Необходимы структуры, которые имеют более сильное спин-орбитальное взаимодействие.

Предложен S.Datta& B.Das, в 1990г.

Спиновый транзистор, одноэлектронный транзистор

Слайд 46

QWET (In 0.7 Ga 0.3 As) на кремнии

(источник: Intel )

Преимущество – достижение исключительно высоких подвижностей при

сложной технологии. Гибридная технология позволяет совмещать новые материалы с кремнием.

Разрабатываются технологии для использования оптических каналов передачи данных внутри одной микросхемы

Слайд 47

Развитие микроэлектроники по Муру и «вне Мура»

Слайд 48

3D сборка

Развивающиеся технологии сборки кристаллов:

Технология «система в корпусе»

3D

сборка с применением межкристалльных сквозных соединений

Сборка «чип на чипе»

Применение

изолированных проводников для разварки чипов (проводник в изоляторе)

Технологии позволяют увеличить скорость передачи сигнала между чипами.

Разрез 3D чипа

Фото разварки стопки чипов (проводник в изоляторе)

Примеры разварки стека чипов («чип на чипе») и посадки на плату

Глубина транзисторных структур ~1мкм, а толщина подложки ~ 1000мкм