современных процессоров, TMS320F28x тактируется от генератора более низкой внешней

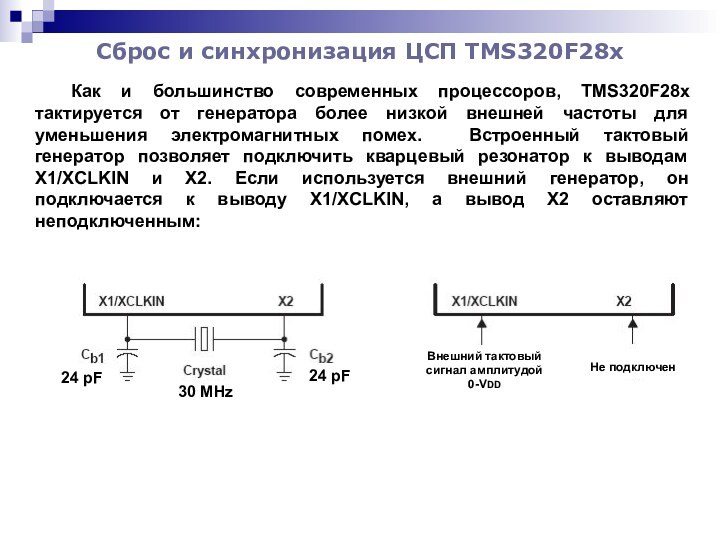

частоты для уменьшения электромагнитных помех. Встроенный тактовый генератор позволяет подключить кварцевый резонатор к выводам X1/XCLKIN и X2. Если используется внешний генератор, он подключается к выводу X1/XCLKIN, а вывод X2 оставляют неподключенным:24 pF

30 МHz

24 pF

Внешний тактовый сигнал амплитудой

0-VDD

Не подключен